# A Clamping Circuit Based Voltage Measurement System for High Frequency Flying Capacitor Multilevel Inverters

Georgios Kampitsis, *Member, IEEE*, Efstratios Batzelis, *Senior Member, IEEE*, Paul D. Mitcheson, *Senior Member, IEEE* and Bikash C. Pal, *Fellow, IEEE*

Abstract- In an era where high-frequency flying capacitor (FC) multilevel inverters (MLI) are increasingly gaining attention in energy conversion systems that push the boundaries of power density, the need for a compact, fast, and accurate FC voltage monitoring is also increasing. In this paper we designed and developed a new FC measurement system, based on precise sampling of the inverter switching node voltage, through a bidirectional clamping circuit. The deviation of FC voltages from their nominal values are extracted by solving a set of linear equations. With a single sensor per phase and no isolation requirements, as opposed to dozens of sensors in traditional FC monitoring, our approach results in significantly lower cost, complexity, and circuit-size. Detailed device-level simulations in LTspice and system-scale simulations in Matlab, validate the accuracy and speed of the proposed measurement system and the balancing strategy in steady state, abrupt load change and imbalance conditions. Experiments carried out in a 3-phase Gallium-Nitride 5-level inverter prototype, reveal a gain in precision and bandwidth that is more than 30 times that of conventional methods, at a fraction of their cost and footprint. The recorded performance renders the developed sensor an ideal solution for fast MLIs based on wide-bandgap technology.

#### I. INTRODUCTION

The emergence of wide bandgap (WBG) technology in the last decade has revolutionized the field of power electronics and opened the road for more efficient and miniaturized energy systems. Particularly, the advantageous characteristics of Gallium Nitride (GaN) devices, such as high switching speed capability and low on-state resistance, in combination with their relatively low breakdown voltage rating, make them the ideal candidate for future multilevel inverters (MLI) for distributed energy resources (DER). Such systems favor the use of smaller magnetic components and the elimination of bulky and unreliable electrolytic capacitors, reaching record-level power densities. More importantly, the lateral structure of GaN high electron mobility transistors (HEMPT) allows the monolithic integration of several power devices, and potentially the entire MLI on a single chip [1]–[4].

Among different MLI topologies [5], the flying capacitor (FC) GaN inverter has the highest potential for miniaturization [6]–[11], due to the absence of clamping diodes and the redundancy of switching states. But like any MLI, reliable operation of the FC inverter requires a balancing mechanism to ensure that the capacitor voltages remain constant.

The simplest way to achieve this is through natural balancing, an open loop control technique that drives the transistors such that the average current flowing through the capacitors remains zero. A review of the modulation strategies that offer natural balancing is performed in [12]. Among them, the phase shifted PWM (PSPWM) is the most widely used technique in literature, due to its implementation simplicity, but exhibits very slow balancing response times in low modulation indices. To overcome this limitation, a modified PSPWM technique with optimal utilization of the switching state redundancies is proposed in [13]-[15]. A combination of natural balancing and improved output harmonic content is achieved with the modified phase disposition PWM (PD-PWM), which uses multiple trapezoidal-shaped carriers or reshaped reference signals [16]-[19]. To further assist the natural balancing process, an RLC circuit, known as balancing booster, can be placed at the inverter output [16], [17], [20], but introduces additional power losses and increases the system size.

Although natural balancing can be proven effective in steady state conditions, in practical implementations there are many factors that can lead to voltage imbalance among the FC, such as asymmetric load disturbances [21], [22], input source non-idealities [23], circuit parasitics, mainly the power devices voltage drop, and timing mismatches introduced by the deadband and the drivers' propagation delay [23], [24]. The voltage imbalance becomes a major concern in high power density MLIs, due to use of small-value thin-film or ceramic capacitor to replace the large electrolytic capacitors [25]. Consequently, it is necessary to adopt a reliable closed-loop active balancing control

However, regardless of the control structure, the precise knowledge of the voltage of each FC in real-time is always required. This is traditionally done via individual and galvanically isolated voltage sensors coupled with each FC [22], [25]–[32]. However, such sensors are expensive and bulky components that increase the system cost, size, and complexity, especially in MLIs with a large number of levels. For example,

$U.K.\ (e\text{-mail: e.batzelis@soton.ac.uk}).$

G. Kampitsis was supported by the European Union's Horizon 2020 Research and Innovation program under the Marie Sklodowska-Curie Grant Agreement 891035. E. Batzelis was supported by the Royal Academy of Engineering under the Engineering for Development Research Fellowship scheme (no. RF\201819\18\86)

G. Kampitsis, B. Pal, and P. Mitcheson are with the Department of Electrical and Electronic Engineering, Imperial College London, SW7 2AZ, U.K. (e-mail: g.kampitsis@imperial.ac.uk, paul.mitcheson@imperial.ac.uk, b.pal@imperial.ac.uk). Efstratios I. Batzelis is with the School of Electronics and Computer Science, University of Southampton, SO17 1BJ Southampton,

a 7-level, 3-phase inverter requires 15 isolated voltage sensors. Particularly for high voltage applications, these sensors are becoming increasingly complex and expensive and less accurate, due to the high insulation requirements and the wide measurement range [33].

One of the most prevalent alternatives found in literature is based on real-time state estimation algorithms that use only the phase current measurement as input. There are several implementations of this method, the most promising of which are based on the discrete Kalman filter [34], [35], the backstepping approach [36], the discrete time model [37], the sliding mode observation [38], the peak inductor current detection [21] and the finite-control-set model predictive-control [24]. The major drawback of such techniques is their low response speed because of their computational burden. At the same time, the requirement for a high sampling rate for the measured current, higher than the switching frequency, makes this approach practically unsuitable for high-frequency MLI applications.

A viable alternative is to compute the FC voltages by sampling the inverter output voltage at the switching node through a single voltage sensor, during different switching states [33]. Once an adequate sampling has been obtained, the FC voltages can be calculated by solving a system of algebraic equations [37]. This AC-side monitoring technique was used in [39] to estimate the voltage states of a DC/DC FC multilevel converter and investigate the system observability and controllability. This technique requires a fixed duty cycle and cannot be directly applied to an inverter. In [40] and [41] the DC voltages of a cascaded H-bridge (CHB) multilevel inverterbased static synchronous compensator (STATCOM) were extracted by a single voltage sensor per phase. Specifically in [40], the sampling was performed close to the zero crossing of the inverter output voltage waveform, where only one cell of the CHB is active, directly associating the measured value to a capacitor's voltage. Although simple, this approach is not applicable to FC MLIs, where each FC is charged to a different voltage level. A modified technique is proposed in [41] and [42], where the samples are not restricted around zero crossing but are also taken when the output reaches its maximum and minimum voltage. A generalized voltage estimation method is proposed in [43] and [44], applicable to several MLI topologies. The voltage extraction is performed after every switching transition with a sampling frequency twice the switching frequency, resulting in high resolution of the estimated capacitor voltages.

However, all AC-side monitoring techniques found in literature suffer from a limited sensor bandwidth with respect to the DC voltage level, which prevents their application to the modern GaN-based high-switching-frequency (above  $10~\rm kHz$ ) inverters. The problem lies in the need for a large time delay (typically a few tenths of  $\mu$ s) between the beginning of the voltage transient and the measurement instance, the value of which is determined by the resistors of the commonly used voltage divider and the internal capacitor of the analog to digital conversion (ADC) module, [39], [41],[44]. The higher the DC

voltage level, the larger the value of voltage divider resistors, resulting in narrower sensor bandwidth.

Therefore, it is evident that accurate voltage detection remains an open issue in high frequency MLI, and especially GaN-based MLI that typically operate at a few hundreds of kHz. Our voltage detection approach is an AC-side monitoring technique that relies on the precise measurement of the inverter phase voltage around zero crossing, via a novel bidirectional clamping circuit. By clamping and sampling the inverter voltage solely during the zero switching states (ZSS), we capture only the FC voltage variation, meaning that we need a smaller measurement range and thus, we achieve faster sample and hold (S&H) acquisition. This, in turn, helps increase the sensor resolution by 30 times, compared to traditional monitoring systems, and accordingly broaden the measurement bandwidth (> 200 kHz), while keeping the complexity and cost to a minimum, by using a single voltage sensor per phase. To the best of the authors knowledge, this is the first attempt to implement a voltage detection system for FC MLI that combines high measurement bandwidth and high resolution with low cost, simplicity, and small footprint. Several applications with strict size and weight restrictions could benefit from our compact and reliable voltage monitoring system, including electric aircraft drive systems [45], distribution system for data centers [46], electric vehicle chargers [47] and grid connected DER [48].

The rest of the paper is structured as follows: The principles of operation of the new measurement system are given in Section II, with focus on the optimum pulse width modulation (PWM) strategy. The theoretical analysis of the bidirectional clamping circuit is presented in Section III, followed by the simulation and experimental results in Section IV and V, respectively. A comparative assessment of the performance of the proposed system against other FC sensing solutions is presented in Section VI and the final remarks and conclusions are reported in Section VII.

### II. SWITCHING NODE MEASUREMENT SYSTEM

The proposed solution employs a single measurement unit at the switching node of each MLI phase, to sample the output voltage with respect to the mid-point of the DC-link,  $v_{x0}$  (where x denotes the phase, x = a, b, c), only during the ZSS, i.e., the inverter states that correspond to zero output voltage. This selective sampling along with the small voltage deviation of the FCs from their ideal value (a few volts in worst case), allows us to clamp the  $v_{x0}$  voltage close to zero and thus, substantially increase the measurement resolution. This is in contrast to the methods in [40]–[44] that measure  $v_{x0}$  at the entire range of output voltage and suffer from delays, low bandwidth and moderate resolution.

# A. Switching States for Zero Output Voltage

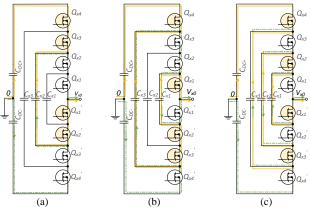

A 5-level inverter has six ZSS, all of which are illustrated in Figure 1. Three of these modes involve the conduction of the top-side DC-link capacitor,  $C_{DC+}$  and are represented with the yellow dotted line, while the complementary states involve the

Figure 1. Three operation modes of a 5-level FC inverter leg that correspond to zero output voltage. The unique switching states involve the conduction of  $C_{DC+}$  and are highlighted with yellow dashed line and the complementary states involve the conduction of  $C_{DC-}$  and are marked with green dashed-dotted line.

condition of the bottom-side capacitor  $C_{DC}$  and are represented with the green dashed-dotted line.

The ZSS, along with the transistors and the FC that are conducting the load current are listed in TABLE I. Note that the conduction or blockage of a power device  $Q_j$ , j = 1, ..., 4 is denoted by a binary number 1 or 0, and the positive sign represents charging and the negative discharging of the FC. For ease of reference to the circuits of Figure 1, the table also includes the respective sub-figure numbers. The last column describes the inverter output voltage as a function of the FCs voltage deviation from their nominal value, i.e.  $\Delta v_{Cj} = v_{DC} \cdot j/(N-I) - v_{Cj}$ , where j = I, ..., N-2, and N is the number of levels.

The presence of three independent equations proves that sampling only during the ZSS is adequate for extracting all FC voltages (solving 3 equations with 3 unknowns). However, the traditional PWM techniques normally generate up to two ZSS. Therefore, the challenge lies in finding the optimal PWM technique that combines natural balancing with low total harmonic distortion (THD) and provides all the ZSS.

#### B. PWM Strategy

As mentioned earlier, the conventional PWM techniques fail to generate the right number of redundant states to solve the system of linear equations. The well-known phase disposition (PD), phase opposition disposition (POD) and alternative phase opposition disposition (APOD), result in poor balancing due to the single switching state around zero crossing, i.e.  $S_I$  (0011). This is attributed to the inherent structure of these PWM techniques that require a level shift of the carriers only in the *Y-axis*, thus keeping the two sets of carriers separated at the either side of the reference around zero crossing. An alternative to the

TABLE I ZERO SWITCHING STATES AND FLYING CAPACITOR CURRENT DIRECTION IN A 5-LEVEL FC INVERTER.

| State    | Fig.1 | $Q_{xI}$ | $Q_{x2}$ | $Q_{x3}$ | $Q_{x4}$ | $C_{xI}$ | $C_{x2}$ | $C_{x3}$ | $v_{x0}$                                               |

|----------|-------|----------|----------|----------|----------|----------|----------|----------|--------------------------------------------------------|

| $S_{I}$  | (a)   | 0        | 0        | 1        | 1        |          | +        |          | $\Delta v_{Cx2}$                                       |

| $S_2$    | (b)   | 1        | 0        | 0        | 1        | -        |          | +        | $\Delta v_{Cx3}$ - $\Delta v_{Cx1}$                    |

| $S_3$    | (c)   | 0        | 1        | 0        | 1        | +        | -        | +        | $\Delta v_{Cx3}$ - $\Delta v_{Cx2}$ + $\Delta v_{Cx1}$ |

| $S_{I}'$ | (a)   | 1        | 1        | 0        | 0        |          | -        |          | -∆vcx2                                                 |

| $S_2'$   | (b)   | 0        | 1        | 1        | 0        | +        |          | -        | $-\Delta v_{Cx3} + \Delta v_{Cx1}$                     |

| $S_3'$   | (c)   | 1        | 0        | 1        | 0        | -        | +        | -        | $-\Delta v_{Cx3} + \Delta v_{Cx2} - \Delta v_{Cx1}$    |

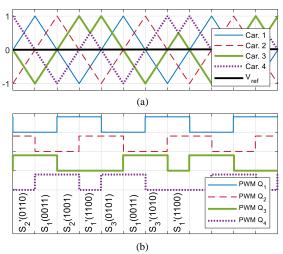

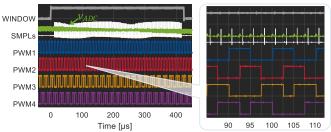

Figure 2. ZSS sequence around  $v_{ref} = 0$  for the CSPS PWM [13]. (a) Carrier and reference signal around zero crossing and (b) respective generated pulses.

conventional PD is proposed in [18], where a trapezoidal carrier replaces the triangular waveforms. The resulting pulse sequence of the modified PD (MPD) matches the sequence of the commonly used phase shift (PS) PWM technique, which is  $S_1(0011) - S_2(1001) - S_1'(1100) - S_2'(0110)$ . It is the shift of the carriers in time that facilitate the production of different switching states. Therefore, these techniques increase the independent switching states to 2, but they are still insufficient for the proposed measurement system.

In contrast to the previously mentioned techniques, the carrier swapping phase shift (CSPS) PWM, that was first introduced in [13], not only generates an appropriate combination of ZSS, but it also improves the passive natural balancing. The principle of operation of this method is based on the exchange of two carriers at their meeting point, as presented graphically in Figure 2. In this example, carriers 3 and 4, marked with thick lines, swap direction when they both reach the 0.5 mark in every period. A complete switching sequence is now comprised by 8 pulses, as revealed by Figure 2 (b), which is:  $S_2'(0110) - S_1(0011) - S_2(1001) - S_1'(1100) - S_3(0101) - S_1(0011) - S_3'(1010) - S_1'(1100)$ .

Having ensured that all the required ZSS can be produced, the system of linear equations of TABLE I can now be solved, as shown analytically in (1).

$$\begin{bmatrix} \Delta v_{Cx1} \\ \Delta v_{Cx2} \\ \Delta v_{Cx3} \end{bmatrix} = \frac{1}{2} \cdot \begin{bmatrix} 1 & -1 & 1 \\ 2 & 0 & 0 \\ 1 & 1 & 1 \end{bmatrix} \cdot \begin{bmatrix} v_{x0}(S_1) \\ v_{x0}(S_2) \\ v_{x0}(S_3) \end{bmatrix}$$

(1)

## C. Minimizing the Measurement Error

The two capacitors forming the DC-Link,  $C_{DC+}$  and  $C_{DC-}$ , may be charged to slightly different voltage levels:  $v_{DC+} = v_{DC}/2 + \Delta v_{DC}$  and  $v_{DC-} = v_{DC}/2 - \Delta v_{DC}$ . Such oscillations usually occur in single phase inverters with small DC-link capacitors or 3-phase grid-connected inverter applications under grid voltage disturbances. This deviation will also be reflected to the inverter output voltage and our measurements, given that the current flows through  $C_{DC+}$  during the unique switching states and through  $C_{DC-}$  during their complementary ones. For example, the output inverter voltage during the ZSS  $S_2$  and  $S_2'$  are

accurately presented in (2). To eliminate the effect of the DClink capacitor mismatch we need to calculate the difference of the two measurements that correspond to two complementary ZSS, as described in (3). To increase the measurement accuracy even further, we can sample multiple sequence of pulses and calculate the average for each state, as shown in (4), where M is the number of repetitive sequences (measurement window). The only exception to this equation is for  $S_1$  state that is sampled twice within one complete sequence.

$$\begin{cases} v_{x0}(S_2) = \Delta v_{Cx3} - \Delta v_{Cx1} + \Delta v_{DC} \\ v_{x0}(S_2') = -\Delta v_{Cx3} + \Delta v_{Cx1} + \Delta v_{DC} \end{cases}$$

(2)

$$v_{x0}(j) = \frac{v_{x0}(S_j) - v_{x0}(S_j')}{2}, j = 1, ..., 3$$

(3)

$$\bar{v}_{x0}(j) = \frac{1}{M} \sum_{1}^{M} \frac{v_{x0}(S_j) - v_{x0}(S_j')}{2}, j = 1, ..., 3$$

(4)

However, care should be taken on the length of the measurement window (i.e. the number of the sampled sequences), because the pulse width of the ZSS gets narrower as we move away from the zero-crossing point of the reference voltage. More specifically, the maximum length of the measurement window depends on the number of levels of the inverter, the switching frequency,  $F_{sw}$ , the amplitude modulation index,  $m_a$ , and the sample and hold time of the analog to digital conversion module (ADC),  $T_{ADC}$ .

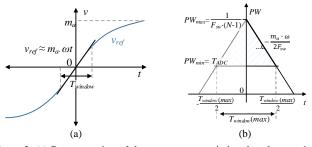

To quantify this relation, we consider a linear approximation the reference sin-wave close to zero crossing,  $v_{ref} = m_a \cdot \sin(\omega t) \cong m_a \cdot \omega t$ , as illustrated in Figure 3(a). The corresponding pulse width, PW, of the ZSS gets its maximum value at t = 0,  $PW_{max} = 1/[(N-1) \cdot F_{sw}]$ , and drops with a rate of  $m_a \cdot \omega/(2F_{sw})$ , according to Figure 3(b) and (5). The maximum pulse width also defines the sampling period,  $F_{smpl} = (N-1) \cdot F_{sw}$ .

Given that the minimum pulse width should be equal to  $T_{ADC}$ , the maximum number of repetitive sequences is given by (6), where  $L_{sq}$ , is the number of pulses in one full switching cycle  $(L_{sq} = 8 \text{ in CSPS PWM})$ . Note that the measurement window extends on either side of the zero-crossing point, thus the final  $M_{max}$  is double the value of (6). Let us take as an example a 5level inverter, operating at  $F_{sw} = 200$  kHz, 50 Hz reference frequency,  $T_{ADC} = 0.675 \,\mu s$  and assume the extreme case of a unity amplitude modulation index. The maximum number of repetitive sequences is 36, i.e., 18 sequences on either side of the zero-crossing point.

Figure 3. (a) Representation of the measurement window length around zero crossing of the reference signal and (b) corresponding pulse width variation with time, when  $m_a = 1$ .

$$PW = -\frac{m_a \cdot \omega t}{2F_{\text{sw}}} + \frac{1}{(N-1) \cdot F_{\text{sw}}}$$

(5)

$$\frac{M_{max}}{2} = \frac{2 \cdot \left(\frac{1}{N-1} - F_{sw} \cdot T_{ADC}\right)}{m_a \cdot \omega} \cdot \frac{F_{sw}}{L_{sq}} \tag{6}$$

By substituting (4) into (1), we obtain the core equations (7), which give the FCs voltage deviation from their nominal values and will later be implemented in the microcontroller.

$$\begin{bmatrix}

\Delta v_{Cx1} \\

\Delta v_{Cx2} \\

\Delta v_{Cx3}

\end{bmatrix} = \frac{1}{4M} \cdot \begin{bmatrix}

1 & -1 & 1 \\

2 & 0 & 0 \\

1 & 1 & 1

\end{bmatrix} \cdot \begin{bmatrix}

\frac{1}{2} \cdot \sum_{1}^{2M} (v_{x0}(S_1) - v_{x0}(S'_1)) \\

\sum_{1}^{M} (v_{x0}(S_2) - v_{x0}(S'_2)) \\

\sum_{1}^{M} (v_{x0}(S_3) - v_{x0}(S'_3))

\end{bmatrix}$$

(7)

# D. Sensitivity Analysis

In this subsection, a sensitivity analysis is performed to evaluate the effect of specific parameters on the operation of the measurement system.

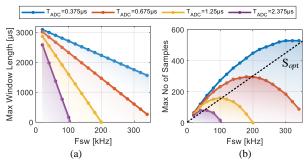

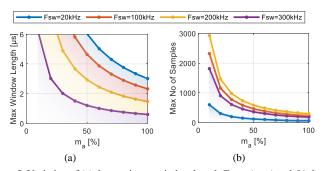

Variable  $F_{sw}$  and  $T_{ADC}$ . Here we investigate the effectiveness of the proposed measurement system in a wide range of switching frequencies and acquisition speeds. Particularly, for lower  $F_{sw}$ , the measurement window can be extended further away from the zero-crossing due to the wider pulses, considering we keep the same value for  $T_{ADC}$ . The relation between the maximum measurement window length,  $T_{window}(max)$ , and the switching frequency is given in (8), which was derived by solving (5) for t and substituting the pulse width (PW) with  $T_{ADC}$ . This relation is graphically represented in Figure 4(a) for realistic values of the sample-and-hold durations. At very low frequencies, all traces converge to the same value given by (9), making the selection of  $T_{ADC}$  less significant.

$$T_{window}(max) = -\frac{4 \cdot T_{ADC}}{m_a \cdot \omega} \cdot F_{sw} + \frac{4}{m_a \cdot \omega \cdot (N-1)}$$

(8)

$$T_{window}(max)|_{F_{sw} \to 0} = \frac{4}{m_a \cdot \omega \cdot (N-1)}$$

(9)

More importantly however, the maximum number of

$$T_{window}(max)|_{F_{sw}\to 0} = \frac{4}{m_a \cdot \omega \cdot (N-1)}$$

(9)

repetitive sequences,  $M_{max}$ , have a quadratic relation to the switching frequency, as shown in Figure 4(b). To find the optimum point where the sample intake is maximized, we take the derivative of (6) equal to zero, as expressed in (10). Substituting the latter into (6) yields the global maximum of the repetitive sequences in (11), which describes a linear relation to

Figure 4. Variation of (a) the maximum window length  $T_{window}(max)$  and (b) the maximum number of samples with the switching frequency, for a 5-level inverter with  $m_a = 1$  and various sample-and-hold times  $T_{ADC}$ .

the optimum operating frequency and is represented in number of samples  $(S_{opt} = L_{sq} \cdot M_{opt})$  by the black dashed line in Figure 4(b).

$$\frac{dM_{max}}{dF_{sw}} = 0 \leftrightarrow F_{opt} = \frac{1}{2 \cdot T_{ADC} \cdot (N-1)}$$

$$M_{opt} = \frac{2}{m_a \cdot \omega \cdot L_{sq} \cdot (N-1)} \cdot F_{opt}$$

(10)

$$M_{opt} = \frac{2}{m_a \cdot \omega \cdot L_{sa} \cdot (N-1)} \cdot F_{opt} \tag{11}$$

This analysis shows that the proposed measurement system can operate in the entire range defined by the area below a particular trace in Figure 4, from low to very high switching frequencies. However, in low frequencies we have the additional option to take multiple samples within the same state to suppress the noise and increase the measurement accuracy.

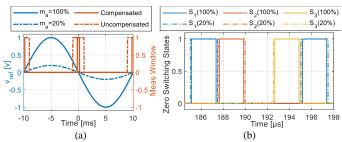

Variable  $m_a$ . In the previous examples we have considered the extreme case of a unity amplitude modulation index,  $m_a$ , which is not always the case. In practice, as  $m_a$  gets smaller, more ZSS appear further away from the zero-crossing point. This, in turn increases the maximum measurement window and the respective number of samples, according to (6) and (8). In fact, both are inversely proportional to  $m_a$ , as depicted in Figure 5 for a range of switching frequencies. In most practical applications, where  $m_a$  is not a fixed value but is the output of a closed loop controller, it is recommended to select the measurement window  $< T_{window}(max)$  that corresponds to  $m_a = 100\%$ .

The continuously varying  $m_a$  value poses a challenge for detecting the instance that the system enters the measurement window. More specifically, if the measurement window is detected by comparing  $|v_{ref}|$  with a fixed positive value, its length will constantly change, leading to an arbitrary number of samples intake. This can be resolved by considering a varying upper bound that accounts for the  $m_a$  swing, so that the window length remains constant. Its value can derive by tacking the linear approximation of the sine reference close to zero for t = $T_{window}$ , as in (12). Figure 6(a) illustrates the measurement windows (in red trace) for two modulation indices,  $m_a = 20\%$ and 100%. The wider dashed line represents the window length when  $m_a = 20\%$  and the modulation index variation is not taken into consideration (uncompensated). On the other hand, the window length stays the same for all modulation indices (solid red line) when (12) is applied.

$$|v_{ref}| \le m_a \cdot \omega \cdot T_{window}, \quad T_{window} \in [0, T_{window}(max)]$$

(12)

Figure 5. Variation of (a) the maximum window length  $T_{window}(max)$  and (b) the maximum number of samples with the amplitude modulation index, for a 5level inverter and various switching frequencies  $F_{sw}$ .

Figure 6. (a) Reference signals and measurement window for two cases of  $m_a$ . (b) Duration of the states  $S_1$ ,  $S_2$  and  $S_3$  at the edge of the measurement window for two cases of  $m_a$ , when  $T_{window}$  is 2% of the fundamental frequency.

More importantly, the ZSS always appear in the same predefined positions, regardless of the amplitude modulation index. This is supported by Figure 6(b), which shows the ZSS  $S_1$ ,  $S_2$  and  $S_3$  at the edge of the measurement window. Only a small reduction of the pulse duration is observed for larger indices, indicating that synchronizing the sampling action for  $m_a = 1$  is adequate for the entire range of  $m_a$  values.

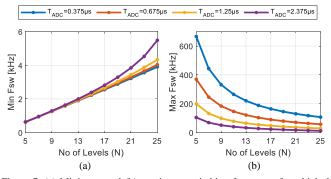

Application limits. The reduction of the maximum window length with the switching frequency and the amplitude modulation index (Figure 4 and Figure 5) signifies that there are operational limitations of the proposed measurement system, which may become confining in FC MLIs with a large number of levels. To calculate the boundaries of the switching frequency for which the proposed system continues to be applicable, we consider the case where only a single complete sequence of pulses is sampled (M = 1). This corresponds to  $T_{window}(max) = 2/F_{sw}$ , given that one complete sequence is unfolded within two switching periods, as shown in Figure 2. At the same time, we can consider the worst-case scenario of unity amplitude modulation index,  $m_a = 1$ , which corresponds to the narrowest measurement window. Solving (8) for  $F_{sw}$  we get the quadratic relationship (13), which leads to the minimum and maximum applicable frequencies of (14). Note that the positive sign in (14) corresponds to  $F_{sw}(max)$  and the negative sign to  $F_{sw}(min)$ . The latter also defines the maximum number of levels, expressed in (15), so that the argument of the square root is positive.

$$\left(\frac{2 \cdot T_{ADC}}{\omega}\right) F_{sw}^2 - \left(\frac{2}{\omega \cdot (N-1)}\right) F_{sw} + 1 = 0 \tag{13}$$

Figure 7. (a) Minimum and (b) maximum switching frequency for which the proposed clamping circuit continues to be applicable for various number of levels and sample-and-hold times.

$$F_{swmin}^{max} = \frac{1 \pm \sqrt{1 - 2 \cdot T_{ADC} \cdot \omega \cdot (N - 1)^2}}{2 \cdot T_{ADC} \cdot (N - 1)}$$

$$N \le 1 + \sqrt{\frac{1}{2 \cdot T_{ADC} \cdot \omega}}$$

(14)

$$N \le 1 + \sqrt{\frac{1}{2 \cdot T_{ADC} \cdot \omega}} \tag{15}$$

Figure 7 illustrates the minimum and maximum boundaries of the switching frequency for a variable number of levels and  $T_{ADC}$  values. Considering, for example,  $F_{sw} = 100$  kHz and  $T_{ADC}$ = 0.675 μs, the proposed clamping circuit is applicable in inverters of up to 15 levels by reducing the number of repetitive sequences to be sampled. However, in practical applications this reduction might come at a cost of lower measurement accuracy at the presence of switching noise.

#### III. BIDIRECTIONAL CLAMPING CIRCUIT

Placing a clamping mechanism at the inverter switching node allows us to capture just the FC voltage variation with a narrow measurement range and fast sampling. At the same time, the rest of the acquisition circuit (amplifiers, ADC module, microcontroller) remain safe from the high voltage swing of  $v_{x0}$ .

There are several different clamping circuits for highvoltage, high switching frequency waveforms, commonly used in short-circuit protection schemes (e.g. de-saturation approach) or in the evaluation of the dynamic on-resistance of the GaN devices, known as current collapse phenomenon, [49]— [55]. The basic idea is that when the input voltage surpasses a predefined level it gets clamped, allowing accurate measurements within a narrow window around zero voltage. Thus, the resolution of the data acquisition is increased by  $v_{PP}$  $v_{CLP}$ , where  $v_{PP}$  is the peek-to-peak input voltage and  $v_{CLP}$  the clamping voltage (e.g. 30 times for  $v_{pp} = 600 \text{ V}$  and  $v_{CLP} = 20$ V). However, these circuits provide only unipolar clamping capability, meaning that they cannot clamp, or they should not be operated with negative voltages altogether, which prevents their adoption in inverter applications.

The simplest bidirectional clamping method consists of two identical clamping diodes in a half bridge configuration, biased to  $\pm v_{DD}$ , and a high-power resistor  $R_{CLP}$  that connects the inverter output to the mid-point of the diode configuration. When  $|v_{x0}| > v_{DD}$  the diodes are conducting, saturating their midpoint voltage to  $\pm |v_{DD} - v_{D-on}|$ , where  $v_{D-on}$  is the diode voltage drop. As the clamping resistor's value increases, the current flowing through the diodes decreases, decoupling the measurement from the diodes' I-V characteristics and the power dissipation on the resistor decreases, meaning that a smaller package device can be used. However, the value of  $R_{CLP}$ , along with the parasitic capacitance of the diodes and the input capacitance of the next stage (e.g., amplifier) dictate the time response of the measurement unit. Therefore, this approach is viable in low switching frequencies (below 10 kHz) and high voltage applications.

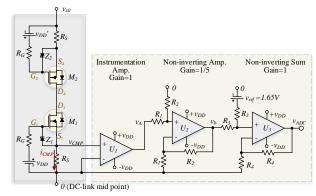

In this paper we propose a new circuit for precise bidirectional clamping, with low power dissipation, small footprint, and low implementation cost.

#### A. Principle of Operation

The core of the new clamping topology consists of two Ntype MOSFETs of similar characteristics, in common drain

Figure 8. Schematic diagram of the proposed bidirectional clamping circuit with two n-type MOSFETs in common drain configuration.

configuration and two source resistors,  $R_S$ , as shown in Figure 8. For each device, a fixed voltage source is connected across the gate terminal and the source resistor, so that the gate-tosource voltage,  $v_{GS}$ , depends on value of  $v_{x0}$ , and the resulting voltage drop across  $R_S$ . The principles of operation of the circuit are described in three separate modes:

• Mode 1.  $M_1$  and  $M_2$  are conducting: For small positive values of  $v_{x0}$ , both MOSFETs are on and the current  $i_{CMP}$ flows with a direction from  $S_I$  to the mid-point of the DClink, thus the clamping output voltage is given by (16).  $v_{CMP}$ can also be expressed as a function of the switching node voltage, as in (17), where  $R_{DSon}$  is the transistors onresistance. Under these conditions, the gate-to-source voltage levels are given by (18) and (19), considering that both polarization sources have the same amplitude  $v_{DD}' = v_{DD}$ .

$$v_{CMP} = i_{CMP} \cdot R_S \tag{16}$$

$$v_{CMP} = \frac{v_{x0}}{2} \cdot \frac{1}{1 + \frac{R_{DSon}}{R_S}} \tag{17}$$

$$v_{GS1} = v_{DD} - v_{CMP} \tag{18}$$

$$v_{GS2} = v_{DD}' + i_{CMP} \cdot R_s = v_{DD} + v_{CMP}$$

(19)

• Mode 2.  $M_1$  is blocking,  $M_2$  is conducting: As the switching node voltage increases, the controlling voltage of the low-side MOSFET drops according to (18) and enters the blocking mode when  $v_{GSI}$  reaches the threshold voltage,  $v_{th}$ , as expressed in (20). At this point, a voltage equilibrium is established, where the current  $i_{CMP}$  remains constant, the clamping circuit outputs a fixed value of  $v_{DD}$  -  $v_{th}$  and the transistor  $M_1$  operates at the critical blocking mode with its  $v_{GSI} = v_{th}$ . At the same time, the high-side MOSFET remains in conduction mode with its controlling voltage saturated at its maximum value, given by (21). This mode holds for all the inverter output voltage values above the upper bound described by (22).

$$v_{GS1} = v_{th} \leftrightarrow v_{CMP} = v_{DD} - v_{th} \tag{20}$$

$$v_{GS2max} = 2 \cdot v_{DD} - v_{th} \tag{21}$$

$$v_{x0} \ge 2 \cdot (v_{DD} - v_{th}) \cdot \left(1 + \frac{R_{DSon}}{R_S}\right) \tag{22}$$

• Mode 3.  $M_1$  is conducting and  $M_2$  is blocking: Similarly, when  $v_{x0} < 0$ ,  $M_2$  enters the blocking mode when (23) is satisfied. During this state, the low-side nMOS gets its maximum controlling voltage, given in (24) and the clamping circuit output is a fixed value of  $-v_{DD} + v_{th}$ . This operating mode corresponds to the switching node voltage rage given in (25), i.e., below the lower bound.

$$v_{GS2} = v_{th} \leftrightarrow v_{CMP} = -(v_{DD} - v_{th}) \tag{23}$$

$$v_{GS1max} = v_{GS2max} = 2 \cdot v_{DD} - v_{th} \tag{24}$$

$$v_{x0} \le -2 \cdot \left(v_{DD} - v_{th}\right) \cdot \left(1 + \frac{R_{DSon}}{R_S}\right) \tag{25}$$

It is important to note that the integrated antiparallel diodes of the MOSFETs are connected in a common-cathode configuration, thus there is no unregulated conduction under any circumstances.

The instrumentation amplifier  $U_I$  in Figure 8 is used as a buffer between the clamping point and the ADC module of the microcontroller, with the advantage that it rejects the common mode noise because of the well-matched integrated resistors. An amplifier with very low noise and a wide operating range should be selected for this stage, such as the AD8421ARMZ. The dual operational amplifier  $U_2$ - $U_3$  that follows is used for scaling and shifting the measured signal to the appropriate values for the ADC. The signal is first scaled down to fit within the acceptable ADC range (normally 3.3V) and then shifted by 3.3/2 V = 1.65 V. The operation amplifier should exhibit high slew rate and low peak-to-peak noise, such as the OPA2189.

The advantage of the proposed clamping circuit is that it can measure both positive and negative voltages with a resolution gain of  $v_{DC}/v_{DD}$  in contrast to traditional voltage measurements. This addresses the noise sensitivity that most AC-side monitoring systems suffer from.

## B. Design Recommendations and Reliable Operation

In this subsection we lay out some key design specifications to ensure safe operation of the proposed circuit, based on the previous mathematical analysis.

An important requirement is to ensure that the  $v_{GS}$  voltage never exceed the limits set by the manufacturer. This, in turn, determines the maximum allowable voltage source used for the polarization of the transistors. According to (24),  $v_{DD}$  should be lower than  $0.5 \cdot (v_{GSmax} + v_{th})$ .

Equation (17) reveals the dependance of the clamped voltage on the transistors on-resistance, quantified by the factor  $\lambda = R_{DSon}/R_S$ . To minimize this effect, transistors with low on-state resistance should be selected, compared to the value of  $R_S$ . However, it should be noted that large  $R_S$  values may introduce a time delay caused by the transistors parasitic output capacitance, thus a tradeoff between measurement deformation and acquisition speed needs to be found.

A general concern with clamping circuits that use active devices is the large voltage spike in transients with large  $dv_{x0}/dt$ . Sharp transition cause high current flowing through the transistors' parasitic capacitance and the source resistors. The simplest way to suppress these voltage peaks is to select transistors with small output and gate capacitance. Alternatively, a Zener diode can be placed between the gate and source terminals of each power device to clamp their voltage to values below  $(2 \cdot v_{DD} - v_{th})$ , as illustrated in Figure 8.

An example of the aforementioned recommendations is presented here, based on the STD8N60DM2 transistor and  $R_S$  = 200  $\Omega$ . According to the datasheet,  $-25 \text{ V} \le v_{GS} \le +25 \text{ V}$  and  $v_{th}$  = 4 V, thus the maximum allowable value for the polarization voltages is  $v_{DDmax}$  = 14.5 V. With a typical  $R_{DSon}$  = 0.55  $\Omega$  and 13.5 nC gate charge, the distortion factor  $\lambda$  is just 0.275% and the voltage spikes do not exceed 30 V.

#### IV. SIMULATION RESULTS

To evaluate the performance of the proposed FC measurement system a series of simulations were performed, starting with device-level simulation of the clamping circuit followed by system-scale simulations of the entire grid connected MLI.

#### A. Device-level Simulation

This section focuses on the detailed simulation of the clamping circuit in LTspice, using the analytical MOSFET and amplifier models, provided by the manufacturers. To reduce the simulation complexity and time, we can replace the entire power circuit (DC-link, inverter leg and load) by an independent source that represents the inverter switching node and has a predefined time-voltage sequence. This sequence can be generated by a high-level simulation platform, such as Matlab/Simulink.

The simulation parameters along with the component values are tabulated in TABLE II. The  $v_{x0}$  voltage source corresponds to a 5-level FC inverter, operating at 100 kHz switching frequency, 50 HZ fundamental frequency and  $v_{DC} = 700$ V. A relatively large voltage deviation from the nominal values has deliberately been introduced to all FC to evaluate the accuracy and speed of the clamping circuit in extreme conditions.

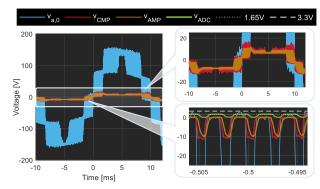

The inverter switching node voltage and the clamping circuit output are presented in Figure 9(a). In addition, the sequence of 8 states of the applied CSPS PWM are indicated in the zoomed view. It can be observed that the proposed scheme safely contains the voltage to the desired range  $\pm$  19 V, in accordance to (22) and (25). Additionally,  $v_{CMP}$  follows closely the  $v_{x0}$  waveform around zero crossing with half its amplitude, which agrees with (17) if we neglect the effect of the distortion factor ( $\lambda = 0.45\%$  in this scenario). A small voltage overshoot is evident during each transient, which is effectively limited by the Zenner diode across the gate-source terminals of the clamping transistors.

Figure 9(b) illustrates the gate-source voltages of the two transistors, along with the  $v_{th}$  line and the maximum allowable voltage level, given by (24). The zoom-box focuses on a small timeframe around t = 16 ms, when  $v_{x0}$  switches between 0 V and  $v_{DC}/4$ , thus the  $M_1$  clamps the positive switching node

TABLE II LTSPICE SIMULATION PARAMETERS, COMPONENTS AND VALUES.

| Parameter       | Name/Value | Parameter | Value        |

|-----------------|------------|-----------|--------------|

| Levels          | 5          | $F_{sw}$  | 100 kHz      |

| nMOSFETs        | STP8NM60   | VDC       | 700V         |

| Zener Diodes    | KDZ22B     | RS        | $200 \Omega$ |

| Instrumentation | AD8421     | $R_G$     | 1 Ω          |

| Amplifier       | AD6421     | VDD       | 15 V         |

Figure 9. LTspice simulation results of the proposed clamping circuit. (a) Switching node voltage and clamping circuit output, (b) gate-source voltages of  $M_1$  and  $M_2$ , and (c) instrumentation amplifier output against  $v_{CMP}$ .

voltage. As expected,  $v_{GSI} = v_{th}$  and  $v_{GS2} = 2 \cdot v_{DD} \cdot v_{th}$  during the non-zero switching states.

The output of the instrumentation amplifier,  $v_{AMP}$ , is plotted against the  $v_{CMP}$  waveform in Figure 9(c). The zoomed view reveals that  $v_{AMP}$  matches  $v_{CMP}$  in amplitude but exhibits smoother transients, as a result of the limited slew rate (35 V/ $\mu$ s) of the AD8421.

# B. System-Scale simulations

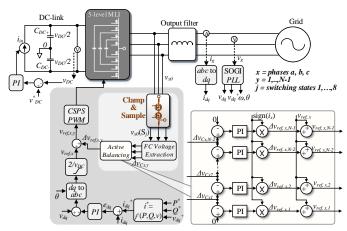

The complete control scheme of a grid-tied MLI with active balancing of the FC, based on the proposed measurement system, was developed in Matlab/Simulink, and is presented in Figure 10. A simple grid-following current control was employed, as in [56], and a double second order generalized integrator PLL (DSOGI PLL) helps extract the positive sequence of the grid voltage and calculate the instantaneous phase. The switching frequency was set at 100 kHz allowing for small DC-link and FC values of 50  $\mu$ F and 10  $\mu$ F, respectively. All the simulation parameters are listed in TABLE III.

The implemented active balancing scheme is based on the work of A.Gias et.al [57], according to which the voltage of each FC can be regulated from the duty cycle of the two adjacent switches. In particular, the average current through each FC is given by (26) as a function of the output current and the duty cycles produced by the current controller. According to this equation, if the output current is positive and the FC  $C_{xy}$  is overcharged, the controller should reduce the current  $\overline{\iota_{Cx,y}}$  by slightly increasing  $d_{x,y}$  and decreasing  $d_{x,y+l}$ . Similarly, if the capacitor is undercharged, the controller should increase  $\overline{\iota_{Cx,y}}$  by increasing  $d_{x,y+l}$  and decreasing  $d_{x,y}$ . The opposite holds for a negative load current.

Figure 10. Complete control scheme of the grid-connected MLI with active FC balancing using the measurements of the proposed clamping circuit.

$$\overline{\iota_{Cx,y}} = \left(d_{x,y+1} - d_{x,y}\right) \cdot \overline{\iota_o}, x = \text{a, b, c and } y = 1, \dots, N-2$$

(26)

However, contrary to [57], we generate this small variation around  $d_{x,y}$ , by adjusting the PWM reference voltage of each power device,  $v_{ref x,y}$ , separately, instead of feeding an offset directly to the resulting duty cycle. This approach achieves equivalent results but in a more efficient manner for practical implementation in a microcontroller. The active balancing control is mathematically represented by (27) and is illustrated in the control diagram of Figure 10. A  $\Delta v_{ref x,y}$  offset is introduced to the original reference voltage for each phase,  $v_{ref x}$ , tuned by a PI controller, the gains of which are listed in TABLE III. The controller's output is multiplied by the sign of the output current to ensure proper operation during both the positive and negative phase currents. The error signals correspond the voltage variation of the FC, as described by (28).

$$v_{ref x,y} = v_{ref x} + \underbrace{\operatorname{sign}(i_o) \left( k_{P-bal} + \frac{k_{l-bal}}{s} \right) \left( e_{x,y-1} - e_{x,y} \right)}_{\Delta v_{ref x,y}}$$

(27)

$$e_{x,y} = \Delta v_{Cx,y}$$

and  $e_{x,0} = e_{x,N-1} = 0$  (28)

To simulate a voltage imbalance in the FCs we simply introduce an asymmetry in phase leg a, in the form of a higher leakage current in one transistor, specifically the  $Q_{a,2}$ . The asymmetry is enforced in a step manner at  $t_0 = 100$  ms. During this scenario, the balancing control is disabled to facilitate better understanding of the clamping circuit and the measurement system in an extreme case.

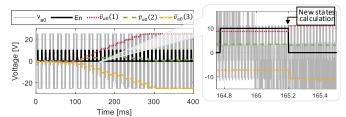

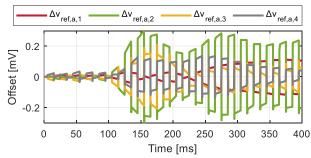

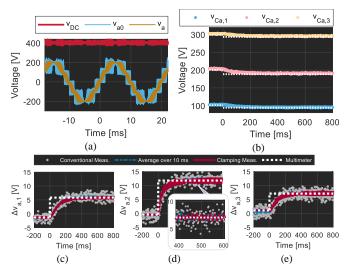

Figure 11 shows the clamped inverter voltage  $v_{a0}$ , along with the measurements over the 3 independent ZSS, according to (4). The window around zero-crossing during which the samples are captured and the averaging is performed is marked with a thick

TABLE III

MATLAB/SIMULINK SIMULATION PARAMETERS

| Parameter             | Value   | Parameter             | Value             |

|-----------------------|---------|-----------------------|-------------------|

| Levels                | 5       | $k_{P	ext{-}PLL}$     | 0.2               |

| $P_{nom}$             | 5 kW    | $k_{I	ext{-}PLL}$     | 3                 |

| $v_{DC}$              | 700 V   | ksogi                 | 3                 |

| $F_{sw}$              | 100 kHz | $k_{P	ext{-}current}$ | 20                |

| $C_{DC+}$ , $C_{DC-}$ | 50 μF   | $k_{I-current}$       | 2000              |

| $C_{FC}$              | 10 μF   | $k_{P	ext{-}bal}$     | $2 \cdot 10^{-5}$ |

| $L_F$                 | 270 μΗ  | $k_{I	ext{-}bal}$     | 0.02              |

Figure 11. Sampling of the clamped inverter output voltage during the three independent ZSS, around zero crossing.

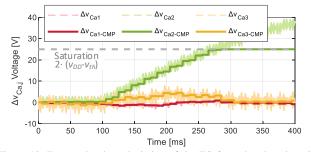

Figure 12. Extracted volage deviation of the FC from the clamping circuit measurements, during imbalanced conditions.

black line (En). As can be seen from the zoom-box on the right, the new values of  $\bar{v}_{a0}(j)$  are extracted at the end of the measurement window. Due to the introduced imbalance, the measurements reach the clamping value (25 V) at  $t_I = 285$  ms. After this point, the acquired data no longer capture the actual voltage deviation of the FC.

The extracted values from the clamping circuit,  $\Delta v_{Caj}$ , are presented in Figure 12 with thick solid lines. For comparison purposes, this graph also includes the reference  $\Delta v_C$  waveforms calculated from direct measured across the FC and the DC-link, as if we had a separate sensor over each capacitor. It can be observed that the proposed approach follows accurately the reference data, with an update rate of double the fundamental

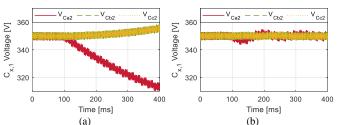

Figure 13. Variation of the FC  $C_{x,2}$  voltages with time, during asymmetric conditions, (a) without and (b) with an active balancing control.

Figure 14. Active balancing control output. Added offset on the reference voltage,  $\Delta v_{ref,x,y}$ , for each transistor in phase a.

grid frequency (steps of 10 ms). In this unbalanced scenario, the calculated  $\Delta v_{Ca,i}$  reach their maximum value at  $t_1$ .

Next, we repeat the simulation with the balance mechanism enabled. The voltage variation  $C_{x,2}$  during the imbalance with and without the enforcement of the active balancing control is illustrated in Figure 13. It is important to highlight that the asymmetry is cascaded in all phases, regardless of the origin of the initial imbalance, as can be observed from Figure 13(a). The imbalance is largely mitigated when the active balancing scheme is activated, as revealed by Figure 13(b). The added benefit of the active balancing controller is that the  $\bar{v}_{x0}(j)$  measurements do not reach the clamping voltage, ensuring accurate acquired data even under disturbances.

Figure 14 illustrates the active balancing controller output for phase a, during the introduction of the asymmetry. These offsets are added to the reference signal  $v_{ref,x}$ , and driven to the top-side transistors.

## C. Performance Under Dynamic Conditions

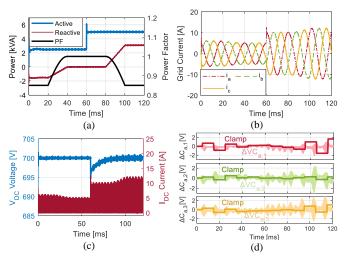

In this subsection, we investigate the effectiveness of the voltage monitoring system and the controllability of the FC during sudden load change, power factor (PF) variations and grid imbalances.

More specifically, the grid connected MLI was initially simulated with a step change of the active power fed to the grid, from 50% to 100% of the nominal value, as shown in Figure 15(a). At the same time, the reactive power increases with ramp-wise increments from -1.55 kVar to 0 and then to +3.1 kVar, which corresponds to a PF variation from 0.85-lagging to 1 then back to 0.85-leading. Please note that the active power step change happens when PF = 1 to decouple the effect of these two variations. The grid current waveforms are depicted in Figure 15(b). The DC-link capacitors experience a sudden voltage drop, shown in Figure 15(c), the extend of which is regulated by the PI DC-link controller. Under these conditions, the measurements extracted by the clamping circuit for phase a are plotted against the actual volage deviation of the FC from their nominal values in Figure 15(d). It is evident that even

Figure 15. Response of the proposed measurement system under abrupt load change and power factor variations. (a) Active and reactive power along with the PF variation, (b) grid injected current, (c) DC-link voltage and current, (d) proposed measurement output against the actual FC voltage variation  $\Delta V_{a,y}$ .

Figure 16. Dynamic response of the proposed measurement system under load imbalances. (a) Inverter and grid voltage, (b) grid current, (c) active and reactive power and (d) proposed measurement output against the actual FC voltage variation  $\Delta V_{a,v}$ .

under abrupt load changes the clamping circuit captures precisely the FC voltages. However, small oscillations exist for low PF values, which is a reflation of the FC charge variation under a non-zero capacitor current within the sampling window. Still, these oscillations are found acceptable for the 0.85 PF, which is a typical lower bound for many grid-connected inverters.

Further, the response of the system is examined under an abrupt grid imbalance, triggered by a single-phase grid voltage drop to 20% of its nominal value for 100 ms according to Figure 16(a), (e.g., a nearby single-line fault). This fault condition results in excess current flowing in phase a (Figure 16(b)), and subsequently in oscillations of the active and reactive power of double the fundamental frequency, as reveled in Figure 16(c). These oscillations are also reflected to the FC voltages in the form high frequency ( $F_{sw}$ ) ripple enclosed within the low frequency envelope of 100Hz, as shown in Figure 16(d). Despite the large FC charge variation under these extreme conditions, the proposed sensor performs well and follows closely the target voltages.

# V. EXPERIMENTAL VALIDATION

The objective here is to experimentally validate the operating principles of the proposed clamping circuit and assess the accuracy of the synchronous sampling and the resulting FC voltage measurements. For this purpose, we designed and developed the FC MLI described in the following sub-section.

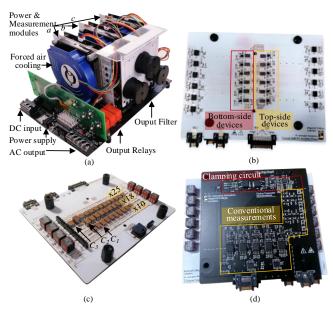

# A. Hardware Design

All experiments we performed using the 5-level, all-GaN FC inverter prototype, shown in Figure 17(a). The main printed circuit board (PCB) holds the DC-link, the DC and AC input and output measurement sensors, the microcontroller, and the output relays. Each of the DC-link capacitors,  $C_{DC+}$  and  $C_{DC}$ , is comprised by 12 parallel connected polypropylene film capacitors, with a total capacitance of  $12 \cdot 4.7 \mu F = 56.4 \mu F$ , which is very close to the simulation model. The power and

Figure 17. (a) All-GaN 3-phase MLI prototype used for the experimental validation. (b) Top and (c) bottom view of a single-phase power board. (d) FC measurement board containing the clamping circuit and conventional measurements.

measurement modules, as well as the output filter are mounted on separate boards for maximum flexibility on the design.

Each phase unit consists of two circuit boards: i) the power board, in white solder-mask, shown in Figure 17(b), that contains the GaN power devices, the gate drivers and the voltage and power isolators. The flying capacitors are mounted on the back side of this board, as depicted in Figure 17(c). As can be seen, each FC consists of several multi-layer ceramic capacitors (MLCC) connected in parallel to match the 10 µF value of the simulation model at the rated conditions. However, the number of paralleled MLCCs is determined by the voltage stress on each FC, given that MLCCs exhibit a sharp capacitance decline with the applied DC bias. Particularly for prototype capacitors used in our (C5750X6S2W225K250KA), the DC bias curve is provided in the manufacturer's characterization sheet [58], from which we calculate that 10, 18 and 25 MLCCs are needed for  $C_{x,l}$ ,  $C_{x,2}$ , and  $C_{x,3}$ , respectively.

Although the prototype can support up to 7-levels, two cells have been bypassed to investigate a 5-level inverter, for consistency with the rest of the paper. *ii*) The measurement board in black solder-mask is shown in Figure 17(d), that contains the proposed clamping circuit, marked with a red dashed line. For comparison purposes, this board also holds a conventional measurement system with separate voltage sensors for every FC, marked with yellow dashed line. For maximum heat extraction, a forced air cooling heatsink is placed in contact with the top side of all power devices and regulated by the microcontroller through a temperature feedback signal. A complete list of the components used in this experimental setup is shown in TABLE IV.

From Figure 17 (d) it is evident that the footprint of the clamping circuit is smaller than that of the traditional measurements circuit and, more importantly, it does not scale

TABLE IV LIST OF COMPONENTS OF THE 7-LEVEL INVERTER PROTOTYPE

| Main and              | l Filter Board                       | Power Board         |                                                                                                              |  |  |  |

|-----------------------|--------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| Component             | Part No                              | Component           | Part No                                                                                                      |  |  |  |

| DC-link<br>Capacitors | ECW-FD2W475KC<br>12p2s configuration | Flying — Capacitors | $\frac{5750X6S2W225K250KA}{C_{x,l}}$ $\frac{C_{x,2}}{C_{x,3}}$ $\frac{C_{x,3}}{10p1s}$ $\frac{18p1s}{25p1s}$ |  |  |  |

| microcontroller       | F28384D                              | GaN Devices         | EPC2034                                                                                                      |  |  |  |

| Current sensor        | MLX91221                             | Gate Driver         | UCC27611DRVT                                                                                                 |  |  |  |

| Voltage isolator      | ACPL-C87A                            | Digital<br>isolator | Si8610BC-B-IS                                                                                                |  |  |  |

| ADC module            | ADS7953                              | Power isolator      | MTU1S1205MC                                                                                                  |  |  |  |

| Output relays         | RZ03-1A4-D012                        | Heatsink            | ATS-UC-DFLOW-100                                                                                             |  |  |  |

| Filter Inductors      | 1140-271K-RC                         | $F_{sw}$            | 100 kHz                                                                                                      |  |  |  |

| Massurament Roard     |                                      |                     |                                                                                                              |  |  |  |

| Measurement Board      |              |                                 |           |  |  |  |  |

|------------------------|--------------|---------------------------------|-----------|--|--|--|--|

| Clampi                 | ing Circuit  | <b>Conventional Measurement</b> |           |  |  |  |  |

| Component              | Part No      | Component                       | Part No   |  |  |  |  |

| MOSFETs                | STD8N60DM2   | voltage<br>isolator             | ACPL-C87A |  |  |  |  |

| Instrumentation<br>Amp | AD8421ARMZ   | Operation<br>Amp                | TLC277    |  |  |  |  |

| Operation Amp          | OPA2189      |                                 |           |  |  |  |  |

| Zener Diodes           | KDZVTFTR20B  |                                 |           |  |  |  |  |

| $R_S$                  | $200 \Omega$ |                                 |           |  |  |  |  |

| $v_{DD}$               | 12V          |                                 |           |  |  |  |  |

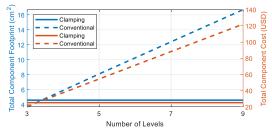

with the number of levels. This is also supported by Figure 18, which shows the cumulative component footprint (in blue traces), for a fair comparison of both circuits, for different number of levels. In practice, however, the resistive divider method in the conventional measurement approach requires even wider PCB area to account for the isolation zones (clearance and creepage) between the different voltage levels. The same figure also includes an indicative cost of the two approaches (red traces), considering the prices of individual component, as of January 2022. From this graph it can be concluded that the proposed approach is preferable when  $N \ge 5$ . For example, when N = 7, the clamping circuit occupies 2.7 times less space and costs 3.5 times less that the traditional measurement system.

## B. Experimental Results

Here we aim to capture the characteristic waveforms of the clamping circuit in balanced and unbalanced conditions, under different DC-link voltage levels.

First, the switching frequency was set at  $F_{sw} = 100$  kHz, which leads to a ZSS pulse-width of 2.5  $\mu$ s. The CSPS PWM technique was applied with carriers 3 and 4 switching position at their intersecting point, as shown in Figure 19. It should be noted that the implementation of this PWM strategy barely adds any computational cost to the microcontroller, since the

Figure 18. Cumulative component footprint and total component cost for the conventional and the proposed measurement systems when varying the number of levels

Figure 19. ZSS sequence for the CSPWM strategy in a 5-level inverter. The measurements window is represented by the gray trace, the samples by the white solid line and the  $v_{ADC}$  signal by the green waveform. The zoomed view highlights that the samples are taken shortly after the beginning of the pulses yet avoiding the transient overshoots.

direction swapping is done in a single command. The same figure also captures the measurement window around zero-crossing (in gray line) and the sample instances (in white). With the measurement window extending to 1% of the fundamental period on either side of the zero-crossing point, we get 160 samples in total, one every  $2.5\mu s$ , which corresponds to 20 complete ZSS sequences.

It is important to note that the acquisition action happens synchronously in every zero-crossing, starting always from the same ZSS, which is  $S_2$  in our system. This is achieved by having the microcontroller initiate the sampling action the first time this state is reached, given that the measurement window signal has been pulled high, indicating the beginning of a new zero-crossing event. Additionally, every sample is taken shortly after the start of the pulse, as can be seen from the zoomed view in Figure 19, to avoid the transient overshoots and to ensure that the ADC sample-and-hold process,  $t_{ADC} = 0.675 \,\mu\text{s}$ , fits well within the 2.5 $\mu$ s pulse. This fixed delay from the beginning of the pulse is tuned through the microcontroller.

Figure 20 shows the output waveform of the clamping circuit against the switching node voltage of phase a, and the output of the instrumentation amplifier, when the system was operated at  $v_{DC} = 300$ V. The top-right zoomed view highlights the clamping action that takes place when the switching node voltage exceeds the boundaries expressed in (22) and (25), and the bottom-right view reveals the smoother transition of the amplifier, as a result of its limited slew rate. It also includes the scaled and shifted

Figure 20. Waveforms at the different stages of the clamping circuit when  $v_{DC}$  = 300V. The inverter output is shown in blue line, the clamped voltage in red, and  $v_{AMP}$  corresponds to the brown curve. The zoomed view on the bottom-right includes the waveform fed to the ADC module, the reference, and maximum lines at 1.65V and 3.3V, respectively.

signal fed to the ADC module with a reference voltage of 1.65V and a maximum value of 3.3V.

To evaluate the performance of the proposed measurement system in static and dynamic conditions, we disabled the active balancing control, and we introduced a step-like asymmetry with the form of a resistor,  $R_{asym}$ , connected in parallel with  $C_{a,2}$  at  $t_0 = 0$ . This artificial asymmetry is an effective method to induce a voltage drop on all the FC of the same phase leg. Both 3-phase and single-phase inverter topologies were tested in a wide range of DC-link voltages.

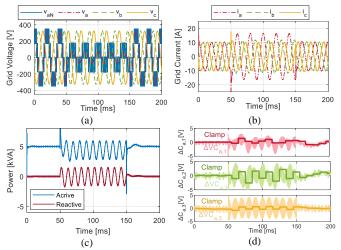

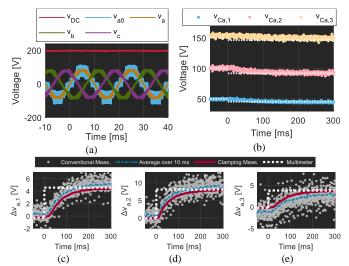

For the first experiment, we investigated a 3-phase inverter feeding a symmetrical resistive load,  $R_{load} = 210 \Omega$ , under  $v_{DC} = 200 \text{ V}$  and  $R_{asym} = 11.75 \text{ k}\Omega$ . Figure 21(a) shows the inverter input and output voltage waveforms under these conditions, while the FC voltage levels, measured by the traditional resistive divider, are illustrated in Figure 21(b). All capacitor voltages drop from their steady state level, with  $C_{a,2}$  exhibiting the highest drop. The white dotted lines in this graph correspond to the true-RMS voltages before and after the imbalance, measured via a digital multimeter and considered the benchmark in the following comparison.

The true advantage of the proposed system is highlighted in Figure 21(c-e), which presents the voltage difference  $\Delta v_{Ca,y}$ , extracted with 3 different measurement techniques:

- i) The gray markers represent the data taken from the traditional measurement system. The dashed line corresponds to the average value of these data, taken every 10 ms for a direct comparison with the clamping circuit

- *ii)* The red solid lines indicate the waveforms recorded from the proposed clamping method and

- *iii*) The white dashed lines represent the true-RMS reference levels, measured by a digital multimeter.

The measurements from the clamping circuit match perfectly the steady state voltage deviation, both before and after the imbalance. On the contrary, the conventional method exhibits

Figure 21. (a) Input and output voltage waveforms for the 5-level inverter when  $v_{DC}=200$ V. (b) FC voltages measured with the conventional voltage divider and digital multimeter values under step-wise asymmetry introduced on  $C_{a,2}$  at  $t_0=0$ . Comparison of the voltage variation the FC (c)  $\Delta v_{Ca,1}$ , (d)  $\Delta v_{Ca,2}$  and (e)  $\Delta v_{Ca,3}$ , between traditional voltage devider sensor and proposed clamping method.

Figure 22.(a) Input and output voltage waveforms for the 5-level inverter when  $v_{DC}=400$ V. (b) FC voltages measured with the conventional voltage divider and digital multimeter values under step-wise asymmetry introduced on  $C_{a,2}$  at  $t_0=0$ . Comparison of the voltage variation the FC (c)  $\Delta v_{Ca,1}$ , (d)  $\Delta v_{Ca,2}$  and (e)  $\Delta v_{Ca,3}$ , between traditional voltage devider sensor and proposed clamping method.

higher steady state error and wider standard deviation around its average value. More specifically, the clamping method exhibits 32 times smaller steady state error compared to the resistive divider technique (22.7 mV compared to 727 mV), and equally smaller standard deviation (57.3 mV as opposed to 818 mV). Note that these are average values over all three FC.

Please note that the settling time in Figure 21(c-e) depends on the FC and  $R_{asym}$  values and is not representative of the measurement system response. Additionally, these error values are not expected to deviate significantly for a higher number of levels, since all measurements are taken from the same node, while the maximum voltage range is determined by the clamping circuit. We also do not expect noticeable changes with the loading levels, as already shown in the simulations.

For the second experiment we increased the DC bus voltage to 400 V and configured a single-phase inverter feeding a resistive load  $R_{load} = 600 \Omega$ . The asymmetric resistor was set to  $R_{asym} = 47 \text{ k}\Omega$ . Contrary to the symmetrical 3-phase inverter, a single-phase topology introduces larger DC-link and FC voltage oscillations of double the fundamental frequency. Neither the oscilloscope waveforms (in Figure 22(a)) nor the traditional voltage divider measurements (Figure 22(b-e)) can capture these oscillations, since their peak-to-peak range is smaller than the standard deviation of the recorded data. However, the clamping measurement system can precisely capture the voltage variation of every FC, as shown in Figure 22(c-e), revealing the advantages of this method.

## VI. COMPARATIVE ANALYSIS

In this section, the performance of the developed clamping-based measurement system is compared against other FC voltage sensing methods found in recent literature. More specifically, the techniques under investigation are grouped into two categories: 1) the *Direct FC Sensing* and 2) the *AC side monitoring* systems, shown in TABLE V. It is noted that only

TABLE V COMPARISON OF DIFFERENT FC VOLTAGE SENSING METHODS

|                      | or Type<br>eference             | Error  | Freq<br>(kHz) |    | Footprin<br>t (cm²)       | Price (USD)                | Limitations                           |

|----------------------|---------------------------------|--------|---------------|----|---------------------------|----------------------------|---------------------------------------|

| irect FC<br>sensing  | LEM<br>LV25-P<br>[25] [26]      | ±0.8%  | DC            | 15 | 76.8                      | 837 -<br>1980              | Cost & Footprint                      |

| Direct FC<br>sensing | Voltage<br>divider<br>[7], [10] | ±2.8%  | DC            | 15 | 24.3                      | 163.2                      | Accuracy, Cost &<br>Footprint         |

| ring                 | [39]                            | ±0.2%  | (1)nr         | 3  | <sup>(2)</sup> <b>3.7</b> | <sup>(2)</sup> <b>70.9</b> | Speed, Noise<br>Sensitivity           |

| AC side monitoring   | [40], [43]                      | <2.6%  | 0.6-2         | 3  | nr                        | nr                         | Accuracy, Speed,<br>Noise Sensitivity |

| side 1               | [44]                            | nr     | 0.5           | 3  | nr                        | nr                         | Accuracy, Speed,<br>Noise Sensitivity |

| AC                   | This<br>work                    | ±0.01% | 100           | 3  | 13.8                      | 75.6                       | Samples per Fund. Period              |

$\overline{}^{(1)}$  nr = not reported.

(2) estimation based on the schematics and experimental setup pictures.

hardware-based solutions have been considered for this comparison; model-based approaches can be perceived as addons that can enhance any hardware solution. The criteria of the comparison are the measurement error, the frequency capability, the total component footprint, and cost, calculated for a 3-phase 5-level FC inverter application.

Unfortunately, most earlier works did not report the bandwidth of their AC measurement system. Therefore, we have included the switching frequency at which the inverter was operated, which gives us a rough estimation of the frequency range of their application. Let us also underline that the cost, footprint and steady state error for the voltage divider method are based on experimental results of this work, since such data are not reported in [7], [10].

The tabular data indicate that the proposed clamped-based solution exhibits the highest resolution at a low cost, similar to the approach in [39]. At the same time, it allows for high switching frequency applications, i.e., more than 50 times the capabilities of other AC-side monitoring systems. It is therefore evident that the proposed measurements system is a competitive solution, combining the advantages of both worlds.

# VII. CONCLUSION

In this paper we introduced a new AC-side monitoring system, based on a bidirectional voltage clamping circuit, for the precise extraction of the FC voltage levels in MLI. The proposed approach uses only a single sensor per phase, as opposed to dozens of sensors in the traditional FC monitoring methods, resulting in significantly lower cost, complexity, and circuit size, factors that do not scale with the number of levels. No isolation is required, since all 3-phase measurements have the same reference, which simplifies the topology even further. The new monitoring system exhibits high resolution (more than 30 times that of the resistive divider method), which helps overcome the noise sensitivity issue that is common in most AC-side voltage sensors. The clamping mechanism provides a larger measurement bandwidth (>200 kHz), allowing its application in high frequency GaN-based inverters. The proposed measurement system was combined with a reliable active balancing control, to address disturbances and

asymmetric loading. The theoretical analysis was supported by device-level and system-scale simulations and thorough experimental testing in a 3-phase, 5-level all-GaN inverter. Although the developed sensing system was designed and tailored for a FC inverter, the AC-side monitoring concept and the prototype clamping circuit can be adopted in other multilevel converter topologies.

#### REFERENCES

- [1] R. van Erp, R. Soleimanzadeh, L. Nela, G. Kampitsis, and E. Matioli, "Co-designing electronics with microfluidics for more sustainable cooling," *Nature*, vol. 585, no. 7824, pp. 211–216, Sep. 2020, doi: 10.1038/s41586-020-2666-1.

- [2] L. Nela, R. Van Erp, G. Kampitsis, H. K. Yildirim, J. Ma, and E. Matioli, "Ultra-compact, High-Frequency Power Integrated Circuits Based on GaN-on-Si Schottky Barrier Diodes," *IEEE Transactions on Power Electronics*, vol. 36, no. 2, pp. 1269–1273, Feb. 2021, doi: 10.1109/TPEL.2020.3008226.

- [3] L. Nela, G. Kampitsis, J. Ma, and E. Matioli, "Fast-Switching Tri-Anode Schottky Barrier Diodes for Monolithically Integrated GaN-on-Si Power Circuits," *IEEE Electron Device Letters*, vol. 41, no. 1, pp. 99–102, Jan. 2020, doi: 10.1109/LED.2019.2957700.

- [4] L. Nela, G. Kampitsis, H. K. Yildirim, R. Van Erp, J. Ma, and E. Matioli, "High-Frequency GaN-on-Si power integrated circuits based on Tri-Anode SBDs," in 2020 32nd International Symposium on Power Semiconductor Devices and ICs (ISPSD), Sep. 2020, pp. 517–520. doi: 10.1109/ISPSD46842.2020.9170092.

- [5] S. Manias, Power Electronics and Motor Drive Systems. Elsevier Science, 2016.

- [6] Z. Liao, Y. Lei, and R. C. N. Pilawa-Podgurski, "Analysis and Design of a High Power Density Flying-Capacitor Multilevel Boost Converter for High Step-Up Conversion," *IEEE Transactions on Power Electronics*, vol. 34, no. 5, pp. 4087–4099, May 2019, doi: 10.1109/TPEL.2018.2858184.

- [7] C. B. Barth et al., "Design and control of a GaN-based, 13-level, flying capacitor multilevel inverter," in 2016 IEEE 17th Workshop on Control and Modeling for Power Electronics (COMPEL), Jun. 2016, pp. 1–6. doi: 10.1109/COMPEL.2016.7556770.

- [8] Y. Lei et al., "A 2-kW Single-Phase Seven-Level Flying Capacitor Multilevel Inverter With an Active Energy Buffer," *IEEE Transactions* on Power Electronics, vol. 32, no. 11, pp. 8570–8581, Nov. 2017, doi: 10.1109/TPEL.2017.2650140.

- [9] Y. Lei, W.-C. Liu, and R. C. N. Pilawa-Podgurski, "An analytical method to evaluate flying capacitor multilevel converters and hybrid switchedcapacitor converters for large voltage conversion ratios," in 2015 IEEE 16th Workshop on Control and Modeling for Power Electronics (COMPEL), Jul. 2015, pp. 1–7. doi: 10.1109/COMPEL.2015.7236448.

- [10] S. Qin, Y. Lei, Z. Ye, D. Chou, and R. C. N. Pilawa-Podgurski, "A High-Power-Density Power Factor Correction Front End Based on Seven-Level Flying Capacitor Multilevel Converter," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 7, no. 3, pp. 1883–1898, Sep. 2019, doi: 10.1109/JESTPE.2018.2865597.

- [11] T. Modeer, C. B. Barth, N. Pallo, W. H. Chung, T. Foulkes, and R. C. N. Pilawa-Podgurski, "Design of a GaN-based, 9-level flying capacitor multilevel inverter with low inductance layout," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 2017, pp. 2582–2589. doi: 10.1109/APEC.2017.7931062.

- [12] R. Stela, "NATURAL CAPACITOR VOLTAGE BALANCE IN MULTILEVEL FLYING CAPACITOR CONVERTRS. A REVIEW OF RESEARCH ACHIEVEMENTS," Power Electronics and Drives, vol. 1(36), no. 2, pp. 5–33, 2016, doi: https://doi.org/10.5277/ped160201.

- [13] S. Thielemans, A. Ruderman, B. Reznikov, and J. Melkebeek, "Improved Natural Balancing With Modified Phase-Shifted PWM for Single-Leg Five-Level Flying-Capacitor Converters," *IEEE Transactions on Power Electronics*, vol. 27, no. 4, pp. 1658–1667, Apr. 2012, doi: 10.1109/TPEL.2011.2169993.

- [14] A. Ibrayeva, V. Ten, Y. L. Familiant, and A. Ruderman, "PWM Strategy for improved natural balancing of a four-level H-bridge Flying Capacitor Converter," in 2015 Intl Aegean Conference on Electrical Machines &

- Power Electronics (ACEMP), 2015 Intl Conference on Optimization of Electrical & Electronic Equipment (OPTIM) & 2015 Intl Symposium on Advanced Electromechanical Motion Systems (ELECTROMOTION), Sep. 2015, pp. 311–316. doi: 10.1109/OPTIM.2015.7426747.

- [15] A. M. Y. M. Ghias, J. Pou, G. J. Capella, P. Acuna, and V. G. Agelidis, "On Improving Phase-Shifted PWM for Flying Capacitor Multilevel Converters," *IEEE Transactions on Power Electronics*, vol. 31, no. 8, pp. 5384–5388, Aug. 2016, doi: 10.1109/TPEL.2016.2521803.

- [16] A. M. Y. M. Ghias, J. Pou, G. J. Capella, V. G. Agelidis, R. P. Aguilera, and T. Meynard, "Single-Carrier Phase-Disposition PWM Implementation for Multilevel Flying Capacitor Converters," *IEEE Transactions on Power Electronics*, vol. 30, no. 10, pp. 5376–5380, Oct. 2015, doi: 10.1109/TPEL.2015.2427201.

- [17] B. P. McGrath and D. G. Holmes, "Enhanced Voltage Balancing of a Flying Capacitor Multilevel Converter Using Phase Disposition (PD) Modulation," *IEEE Transactions on Power Electronics*, vol. 26, no. 7, pp. 1933–1942, Jul. 2011, doi: 10.1109/TPEL.2010.2097279.

- [18] B. P. McGrath, T. Meynard, G. Gateau, and D. G. Holmes, "Optimal Modulation of Flying Capacitor and Stacked Multicell Converters Using a State Machine Decoder," *IEEE Transactions on Power Electronics*, vol. 22, no. 2, pp. 508–516, Mar. 2007, doi: 10.1109/TPEL.2006.889932.

- [19] A. Shukla, A. Ghosh, and A. Joshi, "Natural Balancing of Flying Capacitor Voltages in Multicell Inverter Under PD Carrier-Based PWM," *IEEE Transactions on Power Electronics*, vol. 26, no. 6, pp. 1682–1693, Jun. 2011, doi: 10.1109/TPEL.2010.2089807.

- [20] B. P. McGrath and D. G. Holmes, "Analytical Determination of the Capacitor Voltage Balancing Dynamics for Three-Phase Flying Capacitor Converters," *IEEE Transactions on Industry Applications*, vol. 45, no. 4, pp. 1425–1433, Jul. 2009, doi: 10.1109/TIA.2009.2023480.

- [21] H. Chen, S. Tang, Z. Zeng, and J. Wang, "Flying Capacitor Voltages Estimation in Flying Capacitor Multilevel DC-DC Converters Based on Peak Inductor Current Detection and Output Voltage Measurement," in 2020 IEEE Energy Conversion Congress and Exposition (ECCE), Oct. 2020, pp. 5744–5750. doi: 10.1109/ECCE44975.2020.9235687.

- [22] C. Feng, J. Liang, and V. G. Agelidis, "Modified Phase-Shifted PWM Control for Flying Capacitor Multilevel Converters," *IEEE Transactions* on Power Electronics, vol. 22, no. 1, pp. 178–185, Jan. 2007, doi: 10.1109/TPEL.2006.886600.

- [23] J. Celikovic, R. Das, H.-P. Le, and D. Maksimovic, "Modeling of Capacitor Voltage Imbalance in Flying Capacitor Multilevel DC-DC Converters," in 2019 20th Workshop on Control and Modeling for Power Electronics (COMPEL), Jun. 2019, pp. 1–8. doi: 10.1109/COMPEL.2019.8769615.

- [24] P. B. Malidarreh, D. A. Khaburi, and J. Rodriguez, "Capacitor Voltage Imbalance Reduction in Flying Capacitor Modular Multilevel Converters by using Model Predictive Control," in 2020 11th Power Electronics, Drive Systems, and Technologies Conference (PEDSTC), Feb. 2020, pp. 1–4. doi: 10.1109/PEDSTC49159.2020.9088411.

- [25] A. M. Y. M. Ghias, J. Pou, M. Ciobotaru, and V. G. Agelidis, "Voltage-Balancing Method Using Phase-Shifted PWM for the Flying Capacitor Multilevel Converter," *IEEE Transactions on Power Electronics*, vol. 29, no. 9, pp. 4521–4531, Sep. 2014, doi: 10.1109/TPEL.2013.2285387.

- [26] A. Dekka, A. Ramezani, S. Ouni, and M. Narimani, "A New Five-Level Voltage Source Inverter: Modulation and Control," *IEEE Transactions on Industry Applications*, vol. 56, no. 5, pp. 5553–5564, Sep. 2020, doi: 10.1109/TIA.2020.3000712.