University Of London,

Imperial College Of Science And Technology,

Department Of Computing.

THE ANALYSIS AND DESIGN OF SWITCHING NETWORKS: FOR HIGHLY PARALLEL COMPUTER SYSTEMS

by

A.J. Field.

This thesis submitted in part fulfillment for the requirements of the degree of DoctorOf Philosophy, October 1984.

學而不思 思而 則 ムビン 不 學 貝」 心

子

曰

•

#### ABSTRACT

This thesis examines the application of multistage interconnection networks to highly parallel computer systems which may contain many thousands or tens of thousands of component processors. The cost and complexity of the network becomes prohibitively high when existing network design techniques are applied to very large-scale systems. A number of performance models for interconnection networks are derived. This analysis covers some interesting variations on conventional network designs as well as that of a new class of networks which are capable of exploiting locality of reference whilst still providing low-cost global communication. The general properties of this class of networks is described. The analysis of asynchronously controlled full crossbar switches with request blocking is also described. A new approach to network design is then presented. This approach enables the efficient bit-serial control of the network which naturally reduces the size and complexity of the network by allowing larger single-chip component switches to be constructed. The design of the 'XS1' prototype network switching chip, which incorporates these design techniques, is described. Network interfacing and performance are also Finally, network fault tolerance is discussed. We show how by examined. extending any interconnection network so that each attached component has multiple links into the network, a fault tolerant topology can be realised which does not require fault location in order to achieve fault avoidance. We describe a novel technique for concurrent error detection in bitserially controlled networks which does not require error detection codes to be transmitted through the network. A technique for dynamically replacing individual faulty switches in a fault tolerant network is also described.

#### Acknowledgements

I would like to take this opportunity to thank all the members of the ALICE research group who over the past three years have become not only respected colleagues but also great friends. My thanks go to Mike Reeve, Pete Harrison, Ian Moor and Victor Wu who have fed me with numerous ideas, Penguin biscuits and cups of dark roast coffee for the past three years, and to Roger Bailey, whose threats of physical violence made the task of writing up so much easier to come to terms with. A special "thank you" goes to Alison Surry who took all the words and somehow managed to get most of them typed out in the right order, to Duncan Haysom who in drawing the diagrams saved me many long hours of frustration, and to Graham Fletcher who turned the XS1 from paper to silicon in one go.

Special thanks also goes to the Science And Engineering Research Council Of Great Britain who have supported both myself and the ALICE project for the past three years.

Above all, however, I would like to thank my supervisor, John Darlington, and my close colleague, Martin Cripps, without whom this thesis would most certainly not have been completed. Their endless encouragement and undying enthusiasm is an inspiration to us all.

| Chapter 1: Introduction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| <ul><li>1.1. Exploiting Concurrency</li><li>1.2. Dynamic Communication Networks</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3<br>4                                                                                                   |

| Chapter 2: Network Operation And Analysis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                                                                                        |

| 2.1. General Properties Of Interconnection Networks 2.1.1. Topology 2.1.1.1. Discussion Of Topology 2.1.2. Irregular Topologies 2.1.3. Routing 2.1.4. Blocking 2.1.5. Switching Mode 2.2. Performance Analysis 2.2.1.NetworksWithNon-UniformLoad 2.2.1.1. Assumptions Of The Model 2.2.1.2. A Recurrence Equation For Generating T <sub>N</sub> 2.2.1.3. Sparse Networks 2.2.2. k-Channel Network Analysis 2.2.3.1. Lambda Network Characteristics 2.2.3.2. Analysis 2.2.3.2.1. Effects Of Locality 2.2.4. The Analysis Of Asynchronous Systems                                                                                                                                                                                                                                                                                       | 77101121415166179264368384478                                                                            |

| 2.2.4.1. The Analysis Of An Asynchronous Crossbar Matrix<br>2.2.4.2. Towards Asynchronous Multistage Network Analysis<br>Chapter 3: Self-Clocking Networks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55                                                                                                       |

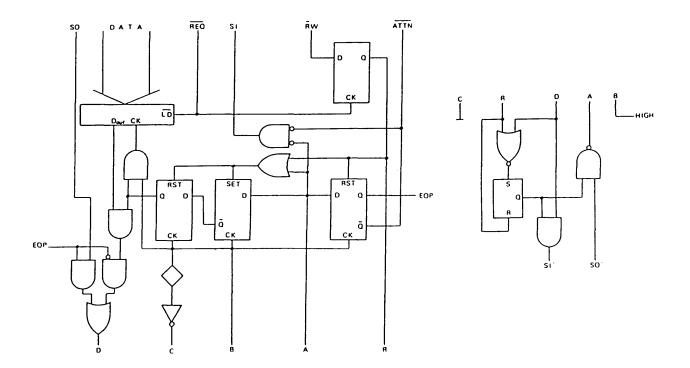

| <ul> <li>3.1. Design Techniques</li> <li>3.1.1. Serial Switching</li> <li>3.1.2. Self Clocking Networks</li> <li>3.2. The Design Of The XS1 Network Switching Device</li> <li>3.2.1. Description Of The XS1</li> <li>3.2.1.1. The D (Data) And C (Clock) Lines</li> <li>3.2.1.2. The R (Reset) Line</li> <li>3.2.1.3. The A (Address Valid) Line</li> <li>3.2.1.4. The B (Burst) Line</li> <li>3.2.2. The XS1 Routing Cycle</li> <li>3.2.3. XS1 Logic</li> <li>3.2.3.2. The Arbitration Unit, A</li> <li>3.2.3.3. The Pass (P) And Multiplexer (M) Units</li> <li>3.2.4. Serial Switching, Self Clocking And Structure Independence</li> <li>3.2.5.1. XS1 Level 0 Interface Description</li> <li>3.2.6.1. Timeouts</li> <li>3.2.7.1. Asynchronous Burst Clock Generation</li> <li>3.2.7.2. Tri-Level Logic Implementations</li> </ul> | 57<br>60<br>64<br>65<br>66<br>67<br>68<br>67<br>72<br>75<br>77<br>78<br>80<br>82<br>85<br>86<br>86<br>86 |

| Chapter 4: Fault Tolerance In Self Clocking Networks.   | 89  |

|---------------------------------------------------------|-----|

| 4.1. Fault Models                                       | 89  |

| 4.1.1. Permanent Faults                                 | 90  |

| 4.1.1.1. "Stuck-At" Faults                              | 90  |

| 4.1.1.2. Permanent Link Faults                          | 91  |

| 4.1.2. Transient Faults                                 | 91  |

| 4.1.2.1. Transient Switch Faults                        | 91  |

| 4.1.2.2. Transient Link Faults                          | 91  |

| 4.1.2.3. Synchronisation Failure                        | 92  |

| 4.2. Existing Fault Tolerant Schemes                    | 93  |

| 4.2.1. Self Testing Switches                            | 93  |

| 4.2.2. Extra-Stage Networks                             | 93  |

| 4.2.3. Multiple Plane Networks                          | 94  |

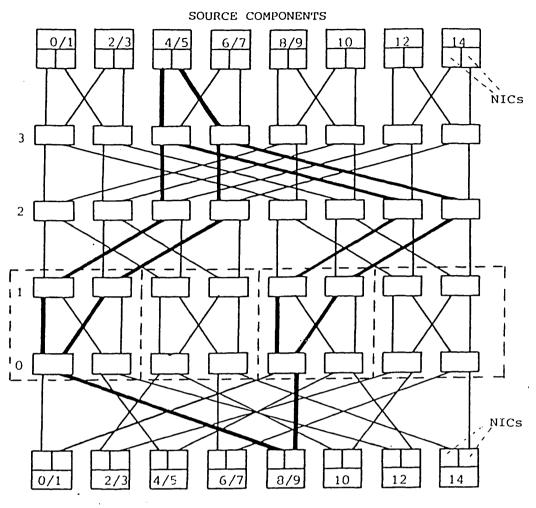

| 4.3. A Fault Tolerant Scheme For Self Clocking Networks | 95  |

| 4.3.1. Providing Multiple Paths                         | 97  |

| 4.3.1.1. Address Transformation                         | 97  |

| 4.3.1.2. Extending The Cube                             | 97  |

| 4.3.1.3. Irregular Topologies                           | 102 |

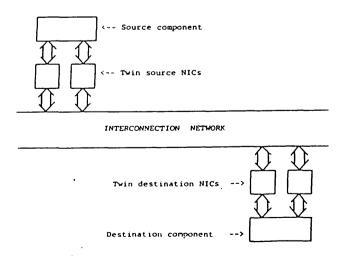

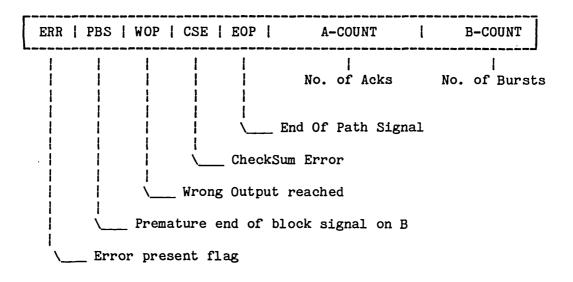

| 4.3.2. Error Detection And Fault Avoidance              | 103 |

| 4.3.2.1. Error Detection Mechanisms                     | 105 |

| 4.3.2.1.1. Path Building Failure                        | 105 |

| 4.3.2.1.2. Addressing Failure                           | 106 |

| 4.3.2.1.3. Data Transfer Error                          | 106 |

| 4.3.2.2. NIC Operation                                  | 107 |

| 4.3.2.3. Finding Fault-Free Paths                       | 111 |

| 4.3.2.4. Multiple Faults                                | 113 |

| 4.3.3. Coping With Multiple Faults                      | 114 |

| 4.3.3.1. Fault Location                                 | 114 |

| 4.3.3.2. Isolating Faulty Switches                      | 116 |

| 4.3.3.3. Fault Repair                                   | 120 |

| 4.4. Summary                                            | 121 |

|                                                         |     |

| <u>Chapter 5:</u> | Sumary | And | <u>Conclusions</u> |

|-------------------|--------|-----|--------------------|

|-------------------|--------|-----|--------------------|

| REFERENCES  |                                         | 128 |

|-------------|-----------------------------------------|-----|

| Appendix 1: | A Routing Algorithm For Lambda Networks | 132 |

| Appendix 2: | Asynchronous Network Simulator Commands | 139 |

## LIST OF FIGURES

| Fig.                            | Description                                                                                                                                                                                                                                       | Page                                                    |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

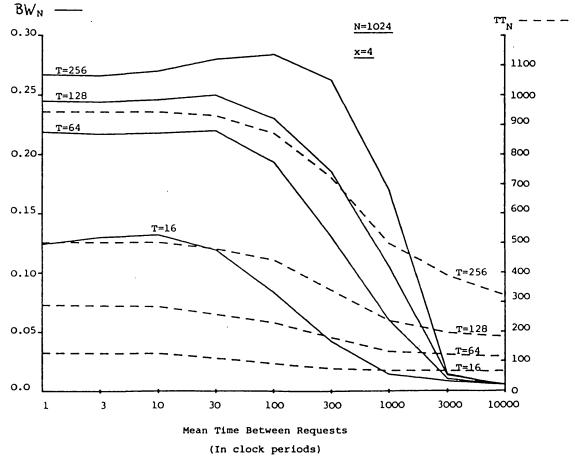

| 2-7<br>2-8<br>2-9               | Sparse Network Performance<br>A K-Channel Network Switch With Degree x<br>K-Channel Network Performance<br>A Lambda Network, Size=32, Degree=2<br>Lambda Switch Loading<br>Lambda Network Performance<br>Lambda Network Performance With Locality | 8<br>25<br>26<br>33<br>35<br>39<br>44<br>46<br>49<br>55 |

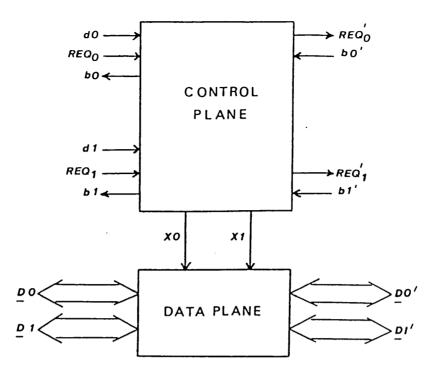

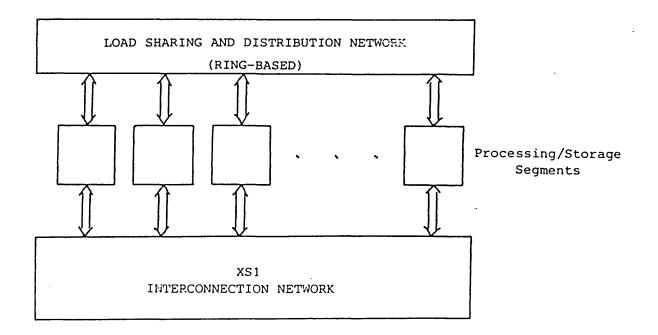

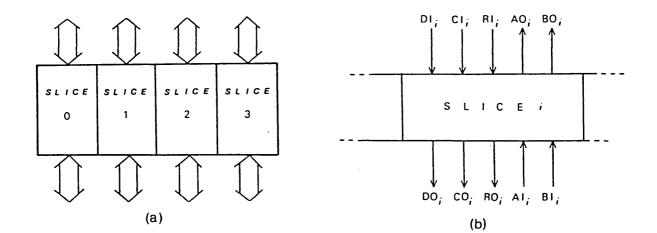

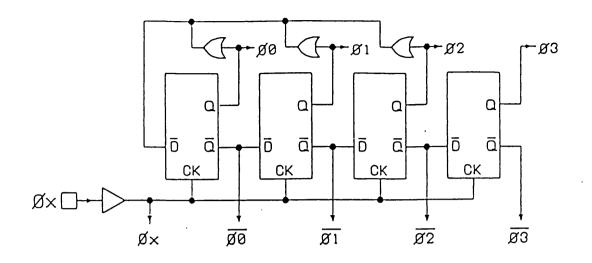

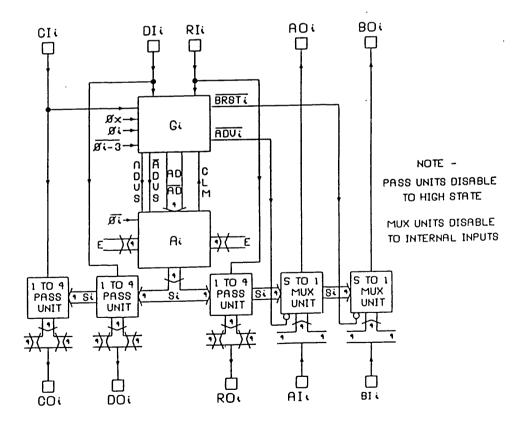

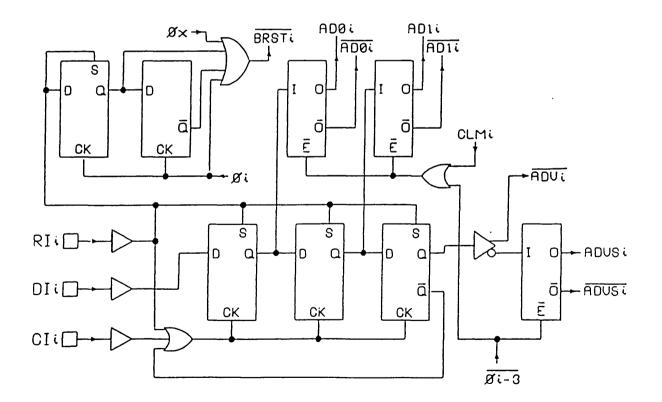

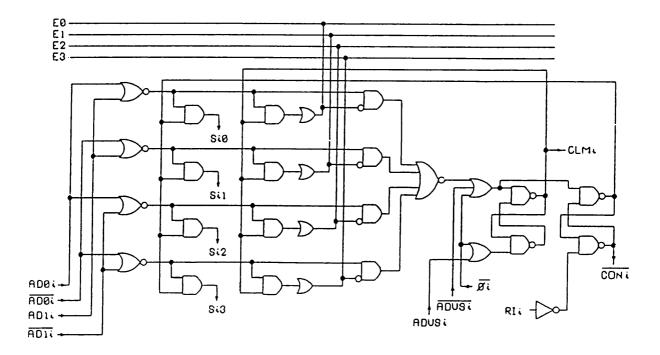

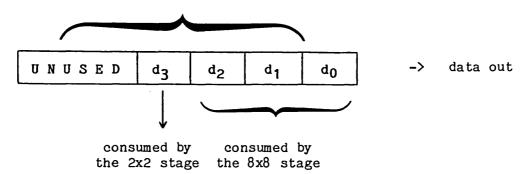

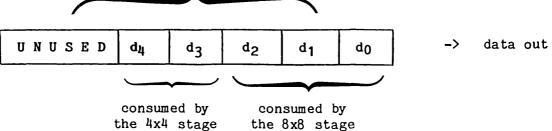

| 3-5<br>3-6<br>3-7<br>3-8<br>3-9 | The ALICE Machine Schematic<br>XS1 Schematic<br>Path Building<br>The Arbitration Clock Generator<br>XS1 Slice Schematic                                                                                                                           | 58<br>65<br>70<br>74<br>75<br>76<br>81<br>86            |

| 4-1<br>4-2<br>4-3               | Example Fault Tolerant Set-Up                                                                                                                                                                                                                     | 103<br>104<br>115                                       |

| A1-1                            | A Lambda Network Switch                                                                                                                                                                                                                           | 136                                                     |

# LIST OF NUMBERED EQUATIONS

| Eqn.   | <u>Defined</u> |

|--------|----------------|

| [2-1]  | 19             |

| [2-2]  | 20             |

| [2-3]  | 21             |

| [2-4]  | 21             |

| [2-5]  | 23             |

| [2-6]  | 30             |

| [2-7]  | 31             |

| [2-8]  | 45             |

| [2-9]  | 51             |

| [2-10] | 52             |

| [4-1]  | 105            |

# LIST OF TABLES

| A1-1 Lambda Network Control String | A1-1 | Lambda | Network | Control | String |

|------------------------------------|------|--------|---------|---------|--------|

|------------------------------------|------|--------|---------|---------|--------|

#### CHAPTER 1

#### Introduction

It is now widely acknowledged that concurrency in program evaluation provides the only means of significantly increasing processing speed.

Cooperation between the component processors of a parallel machine relies on inter-processor communication, and the design of communication systems, or communication <u>networks</u>, for multiprocessor architectures has been a subject of growing interest in recent years. This thesis examines the a class of communication networks in the context of <u>highly parallel</u> systems where communication among many hundreds, thousands, or even tens of thousands of processing components is required.

Feng [Fen82] categorises interprocessor communication into <u>static</u> and <u>dvnamic</u> types, the former corresponding to distributed, and generally loosely coupled systems where communication is only between adjacent processors which are arranged into a processor interconnection graph, and the latter corresponding to systems where a separate communication subsystem is employed to achieve processor coupling. The latter types of system are often, although not always, closely coupled, with the communication system providing each processing device with a 'multiport' view of a shared memory system.

Static communication networks are often employed where the structure of the problems being solved closely reflect the structure of the machine (i.e. the topology of the processor interconnection graph). Virtual tree machines [BuS81], which are very effecient at evaluating divide-and-conquer problems are good examples of such systems. Note that there is generally no global communication: subcomputations (together with their data) are

spawned from one processor to an adjacent processor in the graph and results are fed back via the same connection when evaluation is complete.

Dynamic communication networks have been proposed for various SIMD [Bar81, Lan76,LaS76,LaV82,Law75,Len78,NaS80,NaS82,Sie79,YeL81], MIMD [Dij81,JuD81, MAS81,McS80,MSi80,Pat79], dataflow [ADI83,GWG80] and reduction [DaR81, KeL79] machines. In these machines, each system component is connected to a separate communication network and communication between two arbitrary components is achieved by establishing either a physical or a virtual channel through the network between the two along which data can be transferred.

In these machines subcomputations gain access to a data structure not by being passed a copy of the structure, as is often the case in static networks, but by making a direct (or indirect) reference to a shared copy of the structure when the subcomputation is invoked. As a consequence of sharing data structures in this way, computation soon becomes 'detached' from the data on which they operate. The communication network provides the mechanisms for efficiently accessing shared (global) data items which may be located anywhere in the system, and for the general coordination of concurrent tasks by the passing of control information among the systems' components. The distribution of the processes or computations may also be facilitated by the network.

This thesis is concerned with the design and analysis of a class of dynamic interconnection networks, which are communication networks analogous to high speed telephone exchanges.

The particular applications considered are those systems which obtain high performance by exploiting very large degrees of parallelism and which have the property of <u>extensibility</u> whereby a guaranteed increase in performance can be achieved by simply incorporating more processors into the system.

These systems may contain tens or even tens of thousands of component processors depending on the computing power required.

A number of network designs have been suggested for use in SIMD and MIMD environments [Bar81,Bar82,LiW82,MAS81,Pat79,WLL82], but we argue that these designs are impractical and inappropriate for systems of any significant size. Networks based upon existing principles then become very large, complex, expensive, and inherently unreliable. This thesis examines a very different approach to network design and proposes techniques for both reducing network complexity and enhancing network reliability.

#### 1.1 Exploiting Concurrency

Considerable research has been done into the problem of exploiting concurrency but this has often led to frustration because of the inherently sequential nature of the programming languages used to formulate the problems being solved. Some language extensions have been introduced (for example, parallel DO, and Fork-and-Join in FORTRAN) to enable the programmer to make better use of the parallelism available in the machine, but this greatly complicates the task of programming - the user requiring a detailed knowledge of the machine in order to best exploit its concurrent capabilities.

Although a number of concurrent programming languages have been developed (for example Modula [Wir83] and Occam [IMS84]), one of the most promising solutions to this problem has evolved through the study of declarative (side-effect free) programming languages [Bur75,Hen80,DHT81]. Such languages possess a clean mathematical semantics which enhances program clarity and which significantly aids the task of program development and automatic transformation [BuD77,Dar81]. Additionally, these languages exhibit the property of referential transparency, one consequence of which is the potential for concurrent evaluation. These issues are eloquently

discussed by Backus in [Back78], and a number of machines designed to exploit this concurrency have been proposed, for example [BuS81,DaR81, KeL79,Mag79].

It is this class of so called 'declarative language support architectures' to which this thesis is particularly addressed, although the issues raised are applicable to all network-based systems employing very large numbers of component processors.

## 1.2. Dynamic Interconnection Networks.

A dynamic interconnection network is a communication system in which any network input link can be connected to any network output link by appropriately setting the switch, or switches, from which the network is constructed. This differs from static network where the links between two components are passive and cannot be reconfigured for direct connection to other components [Fen82].

The simple shared bus is one extreme form of dynamic network. This is effective provided the number of components attached to the bus is small. As the number increases the bus reaches a saturation point and bus bandwidth, and hence system performance, levels off [KiA78].

In terms of performance, the most effective dynamic communication system is the full crossbar matrix [LVA82, MeC80, MuM82] which may be viewed as a multiple bus system in which each of the connected components has its own unique communication bus. The full crossbar forms the opposite extreme of dynamic communication networks and has been used in several systems (for example the CDC Cyber 170 [Tho70] and Cmmp [FuH78] systems). Again, however, its use is limited, this time because of the very large  $(O(N^2))$ costs associated with its construction.

Single and multistage <u>interconnection networks</u> provide a cost-effective compromise between the extremes of the shared bus and the full crossbar matrix. These networks are composed of an interconnected array of switching devices each of which is effectively a small crossbar switch. By appropriately setting these switches, any network input link can be dynamically connected to any network output link.

A number of subclasses of network have evolved. These include the rearrangeable (non-blocking) Clos [Clo53] and Benes [Ben65] networks, the PM2I subclass which includes the Data Manipulator [Fen73], the ADM [McS80, McS81] and Gamma [PaR82] networks, the single-stage (perfect shuffle) networks [Sto71], and the so called 'N log N' multistage interconnection networks [DiJ82] which include, for example, the Omega [Law65], Baseline [WuF80], SW-Banyan [GoL73], indirect binary n-cube [Pea77] and Generalised n-cube [SiM81] networks.

It is this latter class of networks which are considered in this thesis and throughout the remainder of the thesis we shall use the term 'interconnection network' to refer solely to the 'N log N' class of networks although strictly the term is generic, covering the Benes, Clos, PM2I, full crossbar networks, and so on.

The remainder of the thesis is divided into three parts:

Chapter 2 describes the general characteristics of the 'N log N' class of dynamic interconnection networks which are of interest to the thesis. Network performance analysis is also studied and four interconnection network variations are examined and compared.

Chapter 3 describes two design techniques, 'self clocking' and 'serial switching', which are techniques aimed at reducing the cost and complexity of the interconnection network whilst maximising the network flexibility.

This chapter includes a description of a network implementation which has been designed and built as part of the ALICE reduction machine project [DaR81].

Chapter 4 examines the (much neglected) issues of fault tolerance and describes how this can be obtained in interconnection networks by introducing error detection mechanisms and by exploiting some of the topological properties of these networks to facilitate fault avoidance and fault repair.

Finally, the summary and conclusions of the thesis are laid out in Chapter 5.

#### CHAPTER 2

#### Network Operation And Analysis

Interconnection networks are a cost-effective means of providing arbitrary point to point communication in a multiprocessor or multicomputer environment, offering greater architectural simplicity and flexibility than the full crossbar matrix which they aim to simulate.

Section 2.1 of this chapter describes the general properties of interconnection networks with regards to their physical and operational characteristics. Section 2.2 is concerned with network analysis and examines the performance of four variations on conventional network implementations.

## 2.1. General Properties Of Interconnection Networks.

## 2.1.1 Topology

A <u>regular</u> interconnection network is rectangular array of interconnected full-crossbar switches of arbitrary, but fixed size. In the remainder of this thesis, the switch size - which we generally refer to as the switch <u>degree</u> - will be denoted by x.

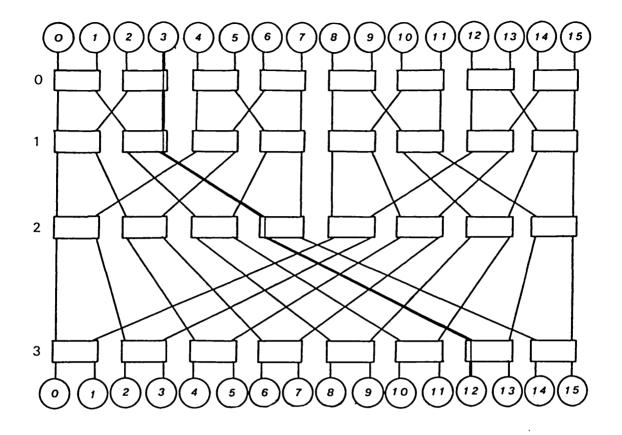

A regular interconnection network of <u>size</u> N and <u>degree</u> x consists of  $n=\log_x N$  stages of crossbar switches with N/x switches in each stage. The total number of switches in the network is consequently  $(N/x)\log_x N$ . Each switch in the network has x input ports and x output ports so that the total number of input and output ports in each stage of the network is equal to N. An example of a simple interconnection network of size 16 and degree 2 is shown in Figure 2-1.

Figure 2-1: An Interconnection Network, Size 16, Degree 2.

The <u>interconnection topology</u> describes the way in which the input and output ports of adjacent stages are connected. Note that there are no connections between the switches of a single stage. Three types of interconnection topology are frequently referred to in the literature; these we now define.

Let the n stages of the network be indexed from 0 to n-1 with stage 0 corresponding to the <u>input</u> side of the network. Now let the jth input link of stage s be labelled  $I_s(j)$ , j=0..N-1, s=0..n-1, and let the jth output link of stage s be correspondingly labelled  $O_s(j)$ , j=0..N-1, s=0..n-1.

The interconnection (or permutation) between adjacent stages, say s and

s+1, may be viewed as a function mapping each of the  $O_{s}(j)$  to exactly <u>one</u> of the  $I_{s+1}(j')$ ,  $s \in [0...n-2]$ ,  $j, j' \in [0...N-1]$ , i.e.

$$P(s) : O_{s}(j) \to I_{s+1}(j')$$

where P is the permutation function for stage s of the network.

We describe the permutation by specifying the relation between j and j' above for a given value of s for each of the three permutation functions. To do this we shall write j as a base x number, which, for a network with n stages will contain n digits. So let j be written:

$$j = \langle j_{n-1}, j_{n-2}, ..., j_1, j_0 \rangle$$

,  $j_k \in [0..x-1]$ , k=0..n-1

We can now express the three permutation functions as functions which transform the component digits of j:-

#### 1. The CUBE Permutation.

$$P(s) : O_{s}(\langle j_{n-1}, j_{n-2}, ..., j_{s+2}, j_{s+1}, j_{s}, ..., j_{1}, j_{0} \rangle) \rightarrow I_{s+1}(\langle j_{n-1}, j_{n-2}, ..., j_{s+2}, j_{0}, j_{s}, ..., j_{1}, j_{s+1} \rangle), \quad s=0...n-2$$

i.e. exchange digits 0 and (s+1) of j.

(This permutation is so called since the couplings between stages s and s+1 of the network are the same as the couplings in the (s+1)th dimension of an x-wide n dimensional hypercube [MSi80, Pea77].

#### 2. The Shuffle Permutation

$P(s) : O_{s}(\langle j_{n-1}, j_{n-2}, ..., j_{1}, j_{0} \rangle) \rightarrow$

$I_{s+1}(\langle j_{n-2},..,j_1,j_0,j_{n-1}\rangle), s=0..n-2$

i.e. left rotate the digits of j.

(This permutation is so called since the case x=2 produces a mapping analogous to that produced by shuffling, or interleaving, two halves of a card deck whose face values are the integers 0...N-1. This topology with x=2 forms the basis of Lawrie's omega network [Law75].)

#### 3. The Partial Shuffle Permutation

$$P(s) : 0_{s}(\langle j_{n-1},..,j_{s+2},j_{s+1},j_{s},..,j_{1},j_{0}\rangle) \rightarrow I_{s+1}(\langle j_{n-1},..,j_{s+2},j_{s},..,j_{1},j_{0},j_{s}+1\rangle), \quad s=0..n-2$$

i.e. perform the shuffle permutation on digits 0...s+1 of j.

(This permutation forms the basis of the baseline topology [WuF80] which has been used to demonstrate the topological equivalence of various N log N networks.)

For example, starting at input port 3 (0011) in the network of Figure 2-1 (which has a Partial Shuffle topology) we have that:

$0_0 < 0011 > -> I_1 < 0011 >$  $0_1 < 0011 > -> I_2 < 0110 >$  $0_2 < 0110 > -> I_3 < 1100 >.$

#### 2.1.1.1. Discussion of Topology

The three permutations defined above form the basis of all regular interconnection networks. A number of these networks use inverted forms of the above topologies, for example the Generalised Cube topology [SiM81] which is simply an inverted form of the indirect x-ary n-cube (which itself is a generalisation of the binary n-Cube of Pease [Pea77]). Note that the Cube permutation function as defined above requires an additional permutation on the output side of the network to 'realign' the port addresses so that they are contiguous at the network outputs. The same is true of an inverted shuffle topology, although the inverted baseline topology requires no output permutation, regardless of the orientation of the network.

An interesting property of the shuffle permutation is that the interconnection is independent of the stage number. Consequently, an extension to a shuffle interconnected network of size N requires the

existing interconnections to be rewired so as to retain the shuffle topology in the extended network. This limits its applications in reconfigurable systems. Also, since the interconnection is the same for all stages, the network may be compressed into a single stage topology in which the network outputs are fed back to the inputs. This configuration is termed a 'single stage' shuffle-exchange network [LaN76,WuF81], and functions by repeatedly circulating requests through the single stage until the required destination node has been reached. Various algorithms have been developed to run directly on a single stage shuffle processor array [Kuh80]. The use of these networks for more general interprocesor communication has been examined in [KDJ83].

## 2.1.2. Irregular Topologies

Of particular significance in the next chapter is the class of irregular network topologies which can be obtained by incorporating switches of varying size into a single network. Irregular networks are important when large switches are being used to construct a network. If only switches of degree x are being used then only networks of size  $x^n$ , n=1,2,... can be constructed. If intermediate sizes are required, then it must be possible to integrate stages of switches of degree y<x. Such a network then has no fixed degree; the term <u>hybrid</u> network will often be used to refer to such irregular configurations.

As a simple example, consider the problem of constructing a Cube-based network of size  $2x^n$  using n stages of switches of degree x and one stage of switches of degree 2.

The rules for interconnecting the n stages of switches of degree x are simply obtained from the regular permutation function for the Cube as was given above. Further extending this network by a factor of two requires adding an additional stage of switches of degree 2. In the regular Cube

network new stages are (ordinarily) added to the bottom (output) stage of the network. The permutation function required between the old output stage and the new degree-2 stage is obtained by viewing the original regular network as being of size  $2^r$  for some r. (An integer value of r will always exist since x is a power of two [Pat79].) The extension is then viewed as a normal extension to a network of degree 2, i.e. the required permutation function is simply that of the Cube, with x=2. Note that if the existing cube is inverted (yielding the <u>Generalised Cube</u> topology), then the extra stage will be added at the top of the network, but the permutation function will be the same.

A wide variety of irregular networks can be conceived. Networks composed of many different sized switches are possible and these can, in theory, occur anywhere in the network so long as the network can be consistently addressed.

An exhaustive categorisation of irregular topologies is impossible, suffice it to say that the ability to construct hybrid networks adds considerable flexibility to system design. A network of size  $2^n$  for any n, for example, may be constructed using a combination of switches of size 2, 4, 8, 16... and so on if required by the system. In the next chapter we propose a design methodology which enables arbitrarily complex hybrid systems to be built without destroying the functionality of the network as a whole.

## 2.1.3. Routing

The process of establishing a path through the network involves individually selecting or <u>addressing</u> exactly one switch in each stage of the network.

It is easy to see from Figure 2-1 that an interconnection network is a system of N interwoven 1:x demultiplexor trees (of fixed, or mixed degree),

and the path building process is similar to that used in conventional tree traversal. Only the required network output port address need be specified in order to establish a path from any source (network input port) to any destination (network output port).

Consider a regular network of size N and degree x. Let the source node address be:

$$S = \langle s_{n-1}, s_{n-2}, ..., s_1, s_0 \rangle \quad s_i \in [0...x-1], i=0...n-1$$

and the destination node address be:

$$D = \langle d_{n-1}, d_{n-2}, \dots, d_1, d_0 \rangle$$

$d_i \in [0 \dots x-1], i=0 \dots n-1$

A path from S to D is established by using  $d_i$  (or  $d_{n-i-1}$  depending on the network) to select stage i of the network. Since each switch in a regular network has x input and x output ports,  $d_i$  is sufficient to specify exactly one of the switches' output ports. It is easy to show that this rule correctly steers the request to its addresed destination node:-

Consider, for example, the <u>Generalised Cube</u> topology which is an inverted form of the Cube topology defined in 2.1.1 above in which  $d_{n-i-1}$  is ordinarily used to select stage i of the network, i=0...-1. In the Generalised Cube, the input (top) stage of the network is traditionally labelled stage n-1 and the output (bottom) stage of the network - stage 0. Using our notation, the permutation function, G, for stage s is given by:-

$$G(s) : O_{s}(\langle j_{n-1}, \dots, j_{s+1}, j_{s}, j_{s-1}, \dots, j_{1}, j_{0} \rangle) \rightarrow I_{s-1}(\langle j_{n-1}, \dots, j_{s+1}, j_{0}, j_{s-1}, \dots, j_{1}, j_{s} \rangle), s=1..n-1$$

After stage n-1 of the network has been selected (using  $d_{n-1}$ ), the request is steered to the stage n-1 output port labelled:

$$(s_{n-1}, s_{n-2}, \dots, s_1, d_{n-1})$$

From the G(n-1) permutation rule, this port is linked to the stage n-2 input port labelled:

$$(d_{n-1}, s_{n-2}, \dots, s_1, s_{n-1})$$

.

After stage (n-k) has been selected similarly, the request is steered to the stage n-(k+1) input port labelled:

$$d_{n-1}, d_{n-2}, \dots, d_{n-k}, s_{n-(k+1)}, \dots, s_1, s_{n-k}$$

Consequently, after stage 1 (=n-(n-1)) has been selected, the request arrives at input port

of stage 0 of the network. Thus supplying the last routing address,  $d_0$ , to the corresponding switch then steers the request to the network output port labelled

$$Q.E.D.$$

In an irregular network, the bit string representing the destination address is simply partitioned irregularly so that the length of each substring,  $d_i$ , used for addressing purposes may be different. In the case where each stage of the network contains switches of fixed degree but the stages themselves are of mixed degree, then the routing scheme may be viewed as being based on mixed radix addressing [BhA82]. A folded network of this sort reduces to an <u>alpha structure</u> as defined in [BhA82].

## 2.1.4. Blocking

The paths from a single source node to the set of all destination nodes of a network form a 1:N demultiplexor tree. Because the demultiplexor trees of all the available input nodes share common nodes in the interconnection graph it is possible that two requests originating from separate source nodes and addressed to separate destination nodes both require to use the same output port of one particular switch in the network. Because in a demultiplexor tree there is only one path between any input and output node, one of these requests must be denied and a blockage is said to have occurred. Until the successful request 'releases' this output port, the blocked request must either 'hang' or cancel. Path building may be held up in any stage in the network mas a result of blocking.

The degree of blocking experienced in a network is a key factor affecting network performance. This issue is raised in 2.2. below where we use probabilistic techniques to analyse the contention in a variety of interconnection network configurations.

## 2.1.5. Switching Mode

An interconnection network may operate in either a circuit switched or a packet switched mode of communication, and the arguments concerning both approaches are similar to those debated in the context of other communication systems. Basically, packet switching offers the advantages of reduced link contention since the packets themselves are buffered in successive stages of the network so that the links used to transmit the packet may be immediately released for further traffic. An excellent examination of packet switching techniques has been presented by Jump and Dias for both single [KDJ83] and multistage interconnection networks [JuD81, DiJ81].

In this thesis we concentrate on circuit switched interconnection networks in which a physical (rather than virtual) channel is established between the source and destination nodes. We do not wish to argue that this approach is generally superior since the most suitable mode is dependent very much on the application. Circuit switching yields faster access times [Bar81], allows for arbitrarily large volumes of data to be transferred in

a single transaction and also facilitates bidirectional (full duplex) communication between source and destination.

## 2.2. Performance Analysis

This section examines interconnection network performance for networks with varying physical and operational characteristics.

We examine four network models. The first considers an extension to the model given by Patel [Pat79] in which we derive equations for the throughput of a conventional switching network operating in a cyclical mode with non-uniform input load. The second model examines the effect of providing multiple channels on each port of the switching nodes of a conventional network. The third model covers the analysis of new class of interconnection structures called <u>Lambda networks</u>, which we define, and the fourth investigates the application of queueing theory to the analysis of asynchronous networks. The design of asynchronous networks is taken up in Chapter 3.

## 2.2.1. Networks with Non-Uniform Load

This analysis relates to networks which operate in a <u>cyclical</u> mode. A network cycle describes a time frame in which the entire network is synchronously routed through and data is transferred along those paths which have been established without incurring blockage [Pat79]. Consequently this analysis is particular to circuit-switched implementations.

The analysis serves two important functions:

For networks which naturally operate in a cyclical mode, for example [Bar81], it yields an accurate measure of the networks throughput.

2. It provides a valuable reference model by which different network configurations can be compared. The cyclical model is adopted in both the next two sections; a direct comparison of the performance of the various networks is then possible.

#### 2.2.1.1. Assumptions of the Model

The following model is a generalisation of that given in [Pat79] which covers the analysis of delta networks.

The environment considers networks which operate on a cyclic basis. For the time being we shall consider a regular network of size N and degree x in which  $N_i$  of the input ports and  $N_o$  of the output ports are actually connected to system components. n will be used to denote the number of stages in the network, i.e.  $n = \log_x N$ .

At the start of a network cycle, requests are synchronously presented to each of the networks' input ports. These requests are then passed through each of the  $\log_X N$  switching stages of the network simultaneously. Certain of the requests will be blocked at intermediate switches in the network. Those which are not blocked form physical channels betwen the input and output ports of the network. The network then enters a data transfer phase during which data is passed (possibly in both directions) across the network. At the end of data transfer, all paths are simultaneously released and the cycle repeats.

We lift the restriction imposed by Patel's model and consider a system in which the inputs may be unequally loaded by the components attached to the network. This enables the performance of certain types of heterogeneous systems to be predicted. In particular, the analysis subsumes both the original analysis given by Patel and that of **sparse** networks, in which only a subset of the input and output ports of the network are connected to system components.

Let the cycles be enumerated by  $C = \{0,1,...\}$  and let E(c,k) be the event: "there exists an arrival on channel k at the start of cycle c ( $c \in C$ ,  $0 \le k \le N-1$ )". The extended definition of Patel's model is then as follows:-

- E(c,k) and E(c',k') are assumed to be independent, c≠c', k≠k'. Note that this implies that blocked requests are 'lost', i.e. requests are assumed to be submitted to a port independently of any previous transactions on that port.

- 2. The probability that a request is submitted on input port k at the start of a cycle is  $P_k$ , k=0..N-1.

- 3. All output ports connected are equally likely to be addressed, that is no output ports are 'favoured' in preference to others.

Note that if only a subset of the output ports are connected to system components, then these are assumed to be evenly distributed across the outputs. That is, each switch in the last stage of the network is assumed to have the same number of connected ports. Note also that assumption 1 is not realistic since in practice blocked requests are almost certain to be resubmitted in the next cycle. However, simulation suggests that this assumption introduces only a small inaccuracy in the predicted performance of the network.

The performance measure we are concerned with here is normalised throughput,  $T_N$ , as defined in [JuD81]. This is the proportion of the output ports which are active during each cycle and is also accurate as a measure of the degree of blocking in the network. From the normalised throughput, the acceptance probability,  $P_A$ , [Pat79] can be easily obtained from:

$$P_{A} = \frac{N_{0} T_{N}}{\sum_{k=0}^{N-1} P_{k}}$$

and the actual bandwidth BW (in requests passed per second) from:

$$BW = \frac{N_0 T_N}{t_c}$$

where  $t_c$  is the network cycle time.

# 2.2.1.2 A Recurrence Equation for Generating T<sub>N</sub>

We begin by considering the top stage of switches (stage 0) and viewing each switch in isolation. Label the switches of the top stage of the network 0..(N/x)-1, and consider some switch w, w  $\epsilon$  [0..N/x-1]. Now label the input ports associated with that switch k, k+1 .. k+x-1. (Clearly, k=wx.) We wish now to derive the normalised throughput of this switch given that the input loads on the inputs to the switch are P<sub>k</sub>, P<sub>k+1</sub>,.., P<sub>k+x-1</sub>, as specified by the model. Define T<sub>N</sub>(s,w) as the normalised throughput of switch w of stage s. T<sub>N</sub>(n-1,w) then represents the normalised throughput of switch w in the output stage of the network.

Let R be a random variable denoting the number of requests present at switch w at the start of a given cycle. Then, we have:

$$\Pr{R=0} = \prod_{l=k}^{k+x-1} (1-P_l)$$

$$\Pr\{R=1\} = \sum_{\substack{l=k}}^{k+x-1} P_l \prod_{\substack{m=k \\ m \neq l}}^{k+x-1} (1-P_m)$$

$$= \prod_{l=k}^{k+x-1} (1-P_m) \sum_{l=k}^{k+x-1} \frac{P_l}{(1-P_l)}$$

and so on. Generally:

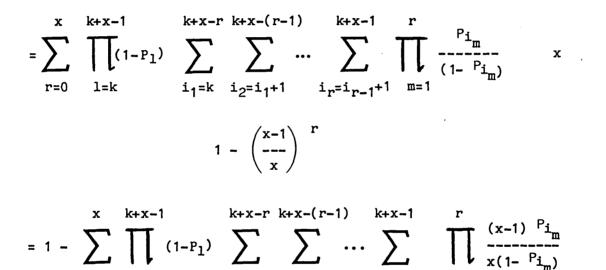

$$\Pr\{R=r\} = \prod_{l=k}^{k+x-1} (1-P_{l}) \sum_{i_{1}=k}^{k+x-r} \sum_{i_{2}=i_{1}+1}^{k+x-(r-1)} \cdots \sum_{i_{r}=i_{r-1}+1}^{k+x-1} \prod_{m=1}^{r} \frac{P_{i_{m}}}{(1-P_{i_{m}})} [2-1]$$

$T_N(0,w)$  can be interpreted as the <u>average</u> load on each output port of the switch. Let U(r) be the probability that a given output link of the switch contains a request given that r requests are present at the inputs to the switch. Then U(r) is given by:

$$U(r) = 1 - \left(\frac{x-1}{x}\right)^{r}$$

Thus, we have for  $T_N(0,w)$ :

$$T_{N}(0,w) = \sum_{r=0}^{x} Pr\{R=r\}.U(r)$$

In order to simplify this expression, we consider the following product term:-

$$D = (a_0 + b_0) \times (a_1 + b_1) \times \dots \times (a_{n-1} + b_{n-1})$$

This expands in a similar manner to the  $Pr\{R=r\}$  terms given above. In fact, the component of D which contains exactly r 'a' terms is given by:

$$c_{r} = \prod_{l=0}^{n-1} b_{l} \sum_{i_{1}=0}^{n-r} \sum_{i_{2}=i_{1}+1}^{n-(r-1)} \cdots \sum_{i_{r}=i_{r-1}+1}^{n-1} \prod_{m=1}^{r} -\frac{a_{i_{m}}}{b_{i_{m}}}$$

[2-3]

Thus D may be rewritten as:

$$D = \sum_{i=0}^{n} c_{i}$$

Therefore, by substituting  $a_{j}=(x-1)P_{j}/x$  and  $b_{j}=(1-p_{j})$ , j=0..x-1, we arrive at an equivalent equation for  $T_{N}(0,w)$  i.e.

$$T_{N}(0,w) = 1 - \prod_{j=k}^{k+x-1} \left( \frac{(x-1)p_{j}}{x} + (1-p_{j}) \right)$$

$$= 1 - \prod_{j=k}^{k+x-1} \left( 1 - \frac{p_{j}}{x} \right)$$

[2-4]

Now, if  $p_{j=p}$  for all j=k...x+k-1, then equation [2-4] becomes:

$$T_{N}(0,w) = 1 - \left(1 - \frac{p}{x}\right)^{x}$$

which is consistent with the result given in [JuD81].

The set of  $T_N(0,w)$ , w=0..(N/x)-1 characterises the normalised throughputs for each switch of the first stage of the network and these form the input load to the switches of the next stage (stage 1) of the network.

By using the values for the  $T_N(0,w)$  and by applying the process recursively, the equation for  $T_N(1,w)$  can be found. From the values of  $T_N(1,w)$  w=0..(N/x)-1, the values of the  $T_N(2,w)$  w=0..(N/x)-1 can be found, and so on. An interesting property of these networks is that:  $T_N(n-1,w) = T_N(n-1,w')$  for <u>all</u> w, w'=0..(N/x)-1.

Observe that although the inputs to the network were unevenly loaded, the normalised throughput of <u>all</u> the networks outputs is the same. This result, (which holds for all networks based on the topologies of 2.1.1.1 but <u>not</u> for all delta networks), stems from the partitioning properties of the three important permutation rules defined in 2.1.1.1:-

Consider stage 0 of the network. This stage partitions the rest of the network into x independent subnetworks [Sie80]. That is, stages 1..n-1 form x independent networks which have no switches in common. The outputs of each switch in stage 0 of the network are fed into the top stage of independent subnetworks. No two links from such a switch connect to the same subnetwork.

Consider now switch w in stage 1. This is linked to by exactly x disjoint switches in stage 0. Let the stage 0 switch connected to input port k of switch w be labelled  $w_k$ ', k=0..x-1. The w'\_k can be found from the permutation function of the network. Consider, for example, the Cube topology defined in 2.1.1.1. If w is written as a base x number,  $\langle w_{n-1}, w_{n-2}, ..., w_2, w_1 \rangle$ , then w'\_k is given by:

$$w'_{k} = \langle w_{n-1}, w_{n-2}, \dots, w_{2}, k \rangle, \quad k=0...x-1.$$

Now consider some  $w'_k$ ,  $k \in [0..x-1]$ . The complete set of stage 0 output ports associated with switch  $w'_k$  are those labelled  $\langle w_{n-1}, w_{n-2}, .., w_2, k, d \rangle$ d=0..x-1. These outputs are attached to the stage 1 switches labelled  $\langle w_{n-1}, w_{n-2}, .., w_2, d \rangle$ , d=0..x-1.

Consequently, the dth output port of <u>each</u> of the w'<sub>k</sub>, k=0..x-1, all 'meet' at the same switch in stage 1, that is, at switch  $\langle w_{n-1}, w_{n-2}, ..., w_2, d \rangle$ . Note that:

- 1. Each of the switches of stage 1 labelled  $\langle w_{n-1}, w_{n-2}, ..., w_2, d \rangle$ , d=0..x-1 lie in independent subnetworks formed by stages 1..n-1.

- 2. Each of the switches of stage 1 labelled  $\langle w_{n-1}, w_{n-2}, ..., w_2, d \rangle$ , d=0..x-1 have identical input loads, since their inputs originate from the same set of switches in stage 0.

Since the same argument applies to all switches in stage 1, it follows that each of the x subnetworks formed by stages 1...-1 have <u>identical</u> loading patterns i.e. for each stage 1 switch (forming a top-stage switch of exactly one subnetwork), with input loads,  $L_0,...,L_{X-1}$ , there exists exactly one corresponding switch in each of the other x-1 subnetworks with the same input loads,  $L_0,...,L_{X-1}$ . The above argument can now be applied (recursively) to each of the x subnetworks. Since each stage partitions the network into x independent subnetworks and since the network has a total of  $n=\log_X N$  stages, it follows that after the last stage has been traversed, the throughput of all switches in the last stage of the network is the same. Consequently,  $T_N(n-1,w)=T_N(n-1,w')$  for all w,w'=0...(N/x)-1.

Note that the equation for  $T_N$  is correct, providing each output port of the network is being used. Consider now the case where  $N_o < N$ , and where each switch in stage n-1 of the network has c of its outputs connected, so that  $N_o = (N/x)c$ . Following the same sequence of steps as was used to generate equation [2-4], the value of  $T_N$  is found to be:-

$$T_{N} = 1 - \prod_{j=0}^{x-1} \left( 1 - \frac{L_{j}}{c} \right)$$

[2-5]

where  $L_m$  is the input load to link m of each switch in the last stage. As a result of the uniform load sharing properties of these networks, the value of  $T_N$  is valid for all connected output ports of the network. The value of  $T_N$  may also be interpreted as the percentage load on each connected output link of the network. Thus the total network bandwidth and

acceptance probability may be expressed as was given in 2.2.1.1.

## 2.2.1.3. Sparse Networks

As was stated earlier, the above analysis subsumes both Patels' original delta network analysis and that of sparse network analysis in which only a subset of the network input/output ports are connected. The throughput of such networks can be obtained by setting the input load values of all unconnected input ports to zero, and by using equation [2-5] to determine the throughput of the last stage of switches, where only a subset of the output ports of each stage n-1 switch are connected. Note that for a single switching element of degree x in which only y of the inputs are used, the load presented to the switch when each of the y inputs are saturated (that is, have input loads of 1) is equivalent to a load of:-

$$\mathbf{x}\left(1-\left(1-\frac{1}{x}\right)^{\mathbf{y}/\mathbf{x}}\right)$$

on <u>each</u> of the x ports of an equivalent fully populated switch; <u>not</u> (y/x) as might be predicted. This (incorrect) assumption has been assumed made on at least one occasion in the literature.

,

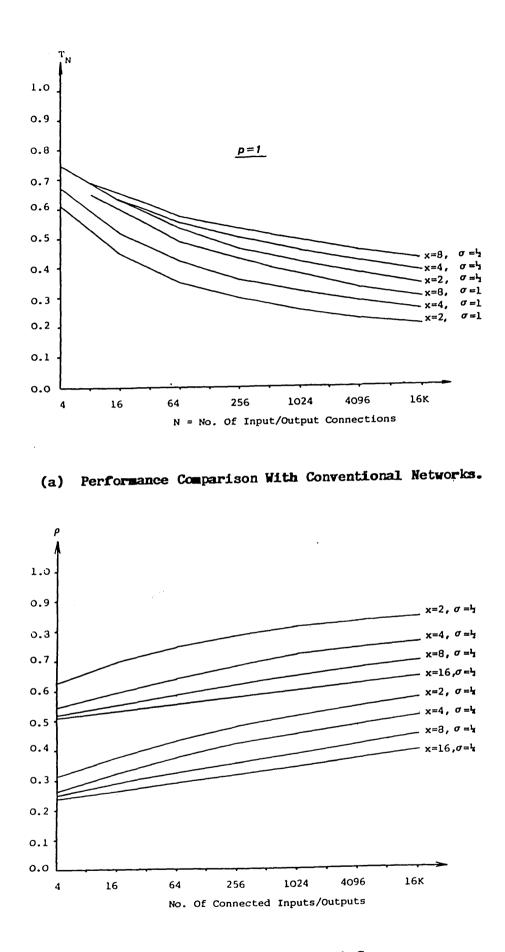

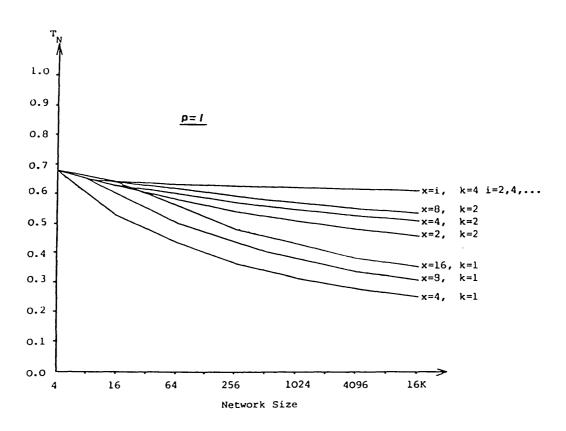

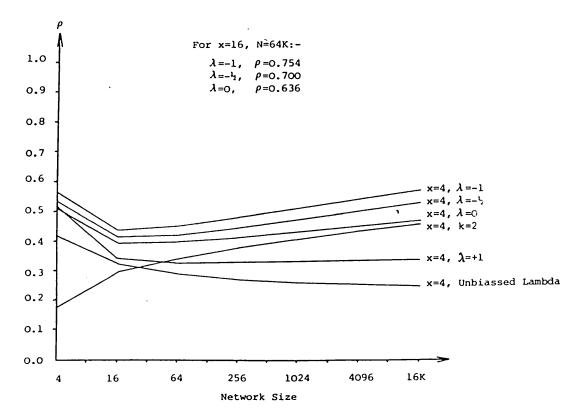

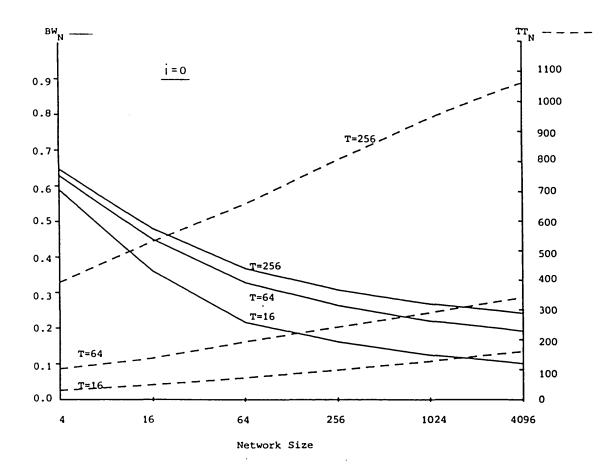

Sparse networks have been proposed as a means of reducing network contention [Bar81]. Figure 2-2(a) shows a comparison of conventional and sparsenetwork performances for varying network sizes<sup>1</sup> and switch degrees. In these curves each connected input is assumed to be saturated (i.e. p=1 for all connected inputs). The parameter,  $\sigma$ , denotes the ratio of connected inputs (and outputs) to network size. Thus  $\sigma$ =1 corresponds to a conventional (non-sparse) configuration. Figure 2-2(b) shows the relative performance/cost curves for the same sparse networks. The parameter,  $\rho$ , denotes the ratio of sparse network performance/cost to conventional network performance/cost. The cost is defined to be the

<sup>&</sup>lt;sup>1</sup> In the performance curves, N denotes the number of connected inputs and outputs in the network <u>not</u> the total number of network inputs/outputs.

(b) Relative Performance/Cost Curves.

Figure 2-2: Sparse Network Performance.

number of switches required to connect a given number of system components. Thus, ho is given by:

$$= O_{T_N(non-sparse)}^{T_N(sparse)}$$

Although sparseness reduces contention, these curves show that the performance gain does not outweigh the required cost increase of 1/O. Sparse networks are, however, easily implemented and require no additional hardware in either the switches or the network interfaces.

## 2.2.2 k-Channel Network Analysis

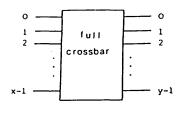

We now examine an interesting variation on traditional network topology and consider the analysis of networks in which each switch port has k channels, or links, associated with it instead of the usual one.

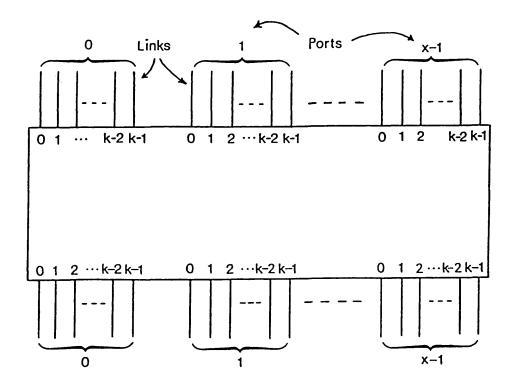

Figure 2-3 illustrates a single switching element of degree x in which each of the x input and output ports contains k links.

Figure 2-3: A k-Channel Network Switch With Degree x.

A k channel network operates in the same manner as a traditional network except that up to k requests can now be passed through a switch port simultaneously instead of only one. We wish to examine to what extent the additional channels reduce network contention and how the resulting performance compares with that of equivalent conventional networks.

There are two ways (not necessarily mutually exclusive) of attaching the system components to such a network:

- If the system components themselves have multiple communication ports, then the network can be made fully populated, with each component supplying k communication ports for network connection, thereby utilising all k.x<sup>n</sup> network input/output ports.

- 2. If the components have only one communication port, then a sparse connection scheme may be used on the input side of the network so that only one of the k available channels of that port is used, and a k:1 multiplexor used on the output side of the network to concentrate the k network port channels into the (single) destination component port. It is possible for each of the input ports to be connected to independent system components, but multiplexors must always be provided at the output ports.

In order to make a meaningful comparison of k-channel networks with conventional and sparse networks, we consider configurations in which only one of the k network input links associated with an input port is connected to a system component.

Again, we assume the cyclical model as described above where probability of a request being presented to a channel of an input port of the network at the start of a cycle is p for all channels. Since these channels are independent, we may immediately write the probability of there being r

requests at the input channels of a given top-stage switch at the start of a cycle as:

$$\begin{pmatrix} x \\ r \end{pmatrix} p^r (1-p)^{x-r}$$

Given that there are r requests at the inputs to a switch, we now wish to know the probability that an arbitrary output link is selected. To do this, we consider the problem in two parts. Firstly, we derive the probability of m of the r requests being directed to an arbitrary output port (a port here is a collection of k links), then from this we generate the individual output link utilisations.

Given that r requests are present at the inputs to the switch, the probability that exactly m are directed to an arbitrary output port is given by:

$$\binom{\mathbf{r}}{\mathbf{m}} \binom{1}{\mathbf{r}} \frac{1}{\mathbf{x}}^{\mathbf{m}} \binom{1}{1} - \frac{1}{\mathbf{x}}^{\mathbf{r}-\mathbf{m}}$$

Given that there are m requests at an output port, the mean utilisation of each of the output links associated with that port is defined to be:-

m k

since two requests cannot both be directed to the same output link.

For the sake of the model, we assume that a request proceeding to an output port, randomly selects one of the currently unused port channels (if one exists). If m>k then the utilisation of each output channel is 1. Consequently the equation for the mean output channel utilisation must consider two cases:  $m \leq k$  and m>k. Thus, we get for the mean utilisation, U:

$$U = \sum_{i=0}^{k-1} \Gamma(i) \left(\frac{i}{k}\right) + \sum_{j=k}^{x} \Gamma(j)$$

where:

$$\Gamma(n) = \sum_{r=0}^{x} {\binom{x}{r}} p^{r} (1-p)^{x-r} {\binom{r}{n}} {\binom{1}{x}}^{n} {\binom{1}{1-\frac{1}{x}}}^{r-n}$$

Now observe that:

$$\begin{pmatrix} x \\ r \end{pmatrix} \begin{pmatrix} r \\ n \end{pmatrix} = \frac{x!}{r!(x-r)!} \cdot \frac{r!}{n!(r-n)!} = \begin{pmatrix} x \\ n \end{pmatrix} \begin{pmatrix} x-n \\ x-r \end{pmatrix}$$

So that we have for  $\Gamma(n)$ :

$$\Gamma(n) = {\binom{x}{n}} {\binom{p}{-}}^n {\binom{p}{1-\frac{p}{x}}}^{x-n}$$

and consequently for U:

$$U = 1 - \sum_{i=0}^{k-1} {\binom{x}{i}} {\binom{p}{x}^{i}} \left(1 - \frac{p}{x}\right)^{x-i} \left(1 - \frac{i}{k}\right)$$

This analysis is correct for a single switch network. However, the equation for U above cannot be used recurrently as in the analysis of 2.2.1. The problem is that although the output ports of a given switch generate statistically independent input processes to the next stage, the channels within the port are not independent. The value of U formulated above is actually an <u>average</u> load taken over the whole port. We cannot, from this average alone, infer that each output link of a given port places a load of U on the next stage of the network independently. So, in forming a recurrence equation to solve for total networkthroughput, we must consider ports, not links within ports:

Thus, for a given switch, s, we define the following:

- R<sub>r</sub>: The probability that a total of r requests are present on the (kx) input links of s.

- 2.  $T_r$ : The probability that a total of r requests are present on the (k) links of an output port of s.

- 4.  $\mathcal{O}_r'$ : The probability that r requests are present on the (k) links of an arbitrary output port of s.

(Since the ports are independent, each input port will have the same value of  $\rho_r$  and each output port will have the same value of  $\rho_r$ '.

Considering, now, an arbitrary switch in which up to kx requests may be present at the switch inputs, we have:

$$T_{r} = \sum_{n=r}^{kx} R_{n} {\binom{n}{r}} {\binom{1}{r}}^{r} {\binom{1}{1-\frac{1}{x}}}^{n-r}$$

and,

$$\emptyset_{\mathbf{r}'} = \begin{cases}

T_{\mathbf{r}} & \mathbf{r} < \mathbf{k} \\

k-1 & [2-6] \\

1 & -\sum_{i=0}^{k-1} T_{i} & \mathbf{r} = \mathbf{k}

\end{cases}$$

We are now aiming to derive a recurrence equation for the  $\rho_r$ ' in terms of the  $\rho_r$  r=0..k-1.

$R_{i}$  is dependent on the way in which requests are distributed over the input links of the switch. Thus, define a vector:

$$\mathbf{n} = \langle n_0, n_1, ..., n_{x-1} \rangle$$

and let  $|\mathbf{n}| = \sum_{i=0}^{x-1} n_i$

where  $n_t$  denotes the number of requests present on port t of a switch, t=0..x-1.  $R_i$ , i=0..kx can then be expressed as:

$$R_{i} = \sum_{\substack{n \\ n_{j} \\ s.t. |n| = i}} \prod_{j=0}^{x-1} \emptyset_{n_{j}} i=0..kx$$

[2-7]

and the normalised throughput of the output multiplexer by :-

$T_N = 1 - \emptyset_0$

The required recurrence equation is then obtained from [2-6] by substituting equation [2-7] for  $R_i$ . Initially, since only one of the (k) links of a given input port is attached to a system component the  $\emptyset_i$  are given by:  $\emptyset_0=1-p$ ,  $\emptyset_1=p$ ,  $\emptyset_j=0$ , j=0..k.

The equation defining  $R_i$  (equation [2-7]), however, is very hard to simplify. The values of the  $R_i$  can be computed explicitly, although equation [2-7] should really be considered as a generating function.

For small values of x, it is relatively easy to generate an equational form for the recurrence equation. As an example, consider the simple case with x=k=2. For given values of  $\emptyset_0$ ,  $\emptyset_1$  and  $\emptyset_2$ , equation [2-7] gives us the following values for  $R_0...R_4$ :

$$R_{0} = \emptyset_{0}^{2}$$

$$R_{1} = 2 \emptyset_{0} \emptyset_{1}$$

$$R_{2} = 2 \emptyset_{0} \emptyset_{2} + \emptyset_{1}^{2}$$

$$R_{3} = 2 \emptyset_{2} \emptyset_{1}$$

$$R_{4} = \emptyset_{2}^{2}$$

We then have for the  $T_r$ , r=0..4:

$$T_r = \sum_{n=0}^{4} \frac{R_n}{2^n} \binom{n}{r}$$

which (as may be verified by the reader) gives the following recurrence equation for the  $\rho_i$ ':-

$$\begin{split} & \emptyset_0' = \emptyset_0 \ (1 - \frac{\vartheta_2}{2}) + \frac{\vartheta_1}{4} \ (1 - \vartheta_0) + \frac{\vartheta_2^2}{16} \\ & \emptyset_1' = \emptyset_0 \ (\emptyset_1 + \vartheta_2) + \frac{\vartheta_1}{2} \ (\emptyset_1 + \frac{3\vartheta_2}{2}) + \frac{\vartheta_2}{4} \end{split}$$

$$\emptyset_2' = 1 - (\emptyset_0' + \emptyset_1')$$

The normalised throughput of the network is obtained by repeatedly applying the above equations, setting  $\emptyset_0 = \emptyset_0'$ ,  $\emptyset_1 = \emptyset_1'$  and  $\emptyset_2 = \emptyset_2'$  after each iteration and repeating the process as many times as there are stages in the network.

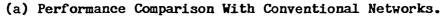

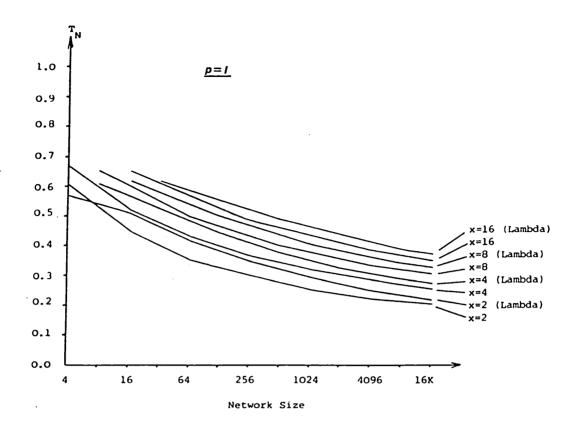

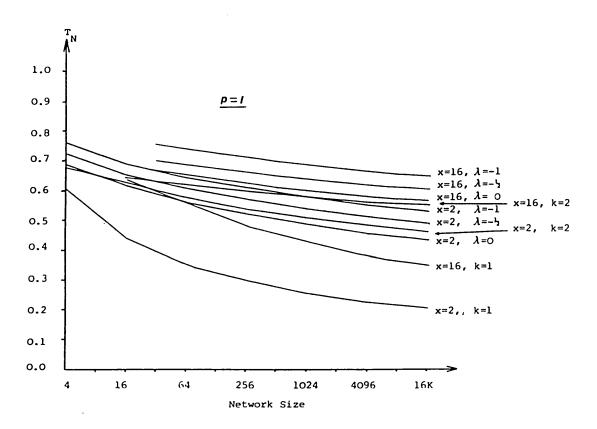

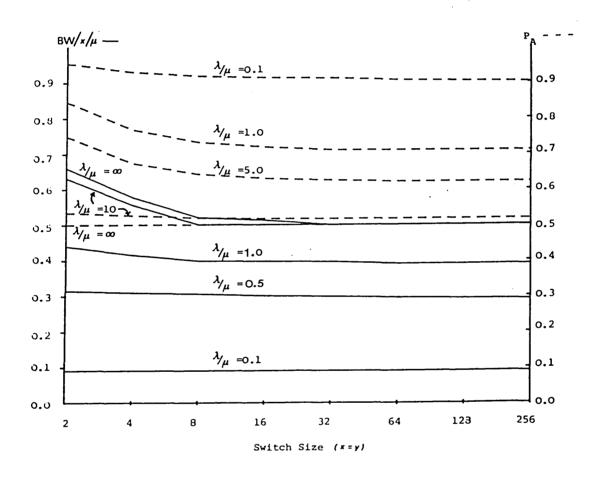

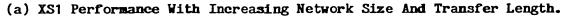

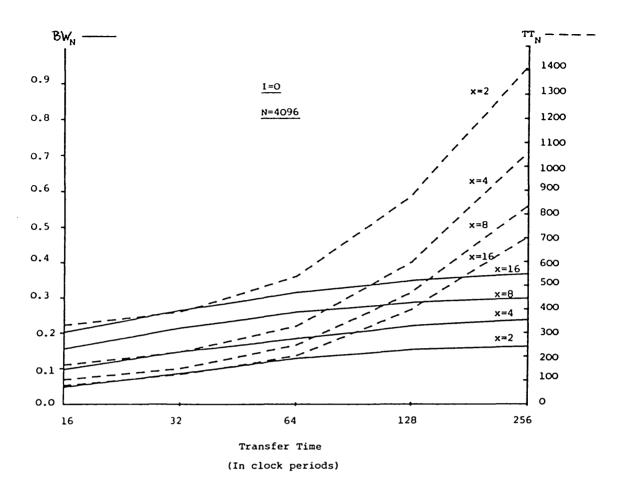

Figure 2-4(a) compares the throughputs of conventional and k-channel interconnection networks for varying network sizes (measured by the number of connected inputs) and switch degrees. These graphs assume that all connected inputs present a load of 1 (i.e. a request is submitted on every cycle).

In terms of raw performance, the k-channel configurations offer higher throughput than conventional networks, but they require larger switch packages because of the additional communication links associated with each port. A conventional switch of degree x thus requires approximately the same number of pins as a k-channel switch of degree x/k.

The effect of this is revealed in the relative performance/cost curves shown in Figure 2-4(b). In these curves the relative performance/cost metric,  $\rho$ , is given by:-

(b) Relative Performance/Cost Curves

Figure 2-4: K-Channel Network Performance.

$$\rho = \frac{\log_x N}{k \cdot \log_{x/k} N} \cdot \frac{T_N(k-channel)}{T_N(single channel)}$$

In Figure 2-4(b) the performance/cost figures for conventional networks of degree x are compared with those of k-channel networks with degree x/k for varying values of k>1.

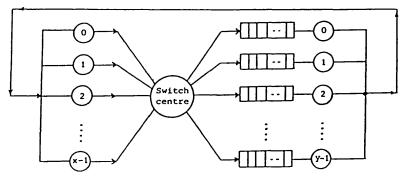

## 2.2.3. Lambda Network Analysis.

In a conventional interconnection network the input and output ports of the network occur at opposite extremes of the network. The 'distance', in terms of the number of switches traversed, between a source component attached to the input side of the network and a destination component attached to the output side of the network is the same for all source/destination pairs - i.e.  $\log_x N$ .

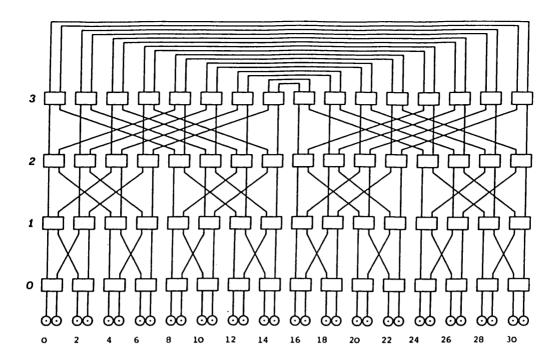

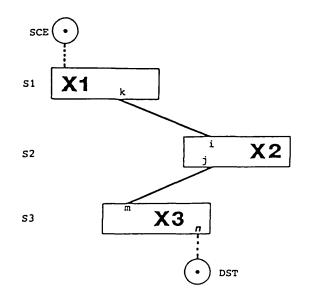

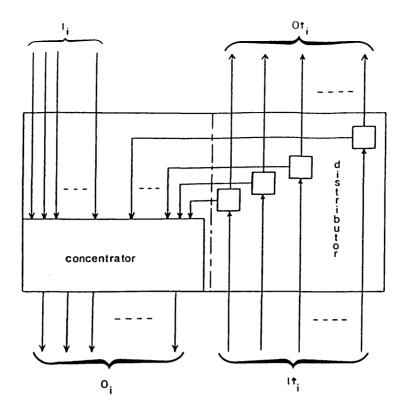

We now introduce <u>Lambda networks</u> which offer the benefits of global communication yet which also allow locality between communicating components to be exploited. Lambda networks are homomorphic (one-sided) networks which are similar in topology to conventional interconnection networks except that both the input and output links of the network occur on the same side of the network. Figure 2-5 shows an example of a Cubebased Lambda network of size 32 and degree 2.

In Figure 2-5, the system components are shown at the bottom of the diagram and each has both a link into and a link out of the network via the bottom stage of the network, although the input and output links could be attached to independent components. Requests submitted by the components are fed upwards until the addressed destination node can be reached from the

Figure 2-5: A Lambda Network, Size=32, Degree=2.

currently selected switch by turning round ('pivoting') and traversing the network in the opposite direction. The switches on the downward path are selected in the usual way i.e. the switch select addresses are derived from the destination node address. An algorithm for path building in a Lambda network is described in Appendix I.

Unlike conventional networks, it is possible for a request to reach its required destination by traversing less than the usual  $\log_X N$  switches. (In the extreme, if the source and destination addresses are the same then the network need not be accessed at all.) We now wish to know whether the ability to take these 'short cuts' through the network has any effect on the network performance for a network of given size and degree. Firstly, though, we describe some of the general characteristics of these networks which are important to the analysis given in 2.2.3.2 below.

### 2.2.3.1. Lambda Network Characteristics.

A <u>regular</u> Lambda network of size 2N and degree x consists of two identical and interconnected subnetworks located side by side each of which has one of the topologies specified in 2.1.1.1. There are thus  $n=\log_x N$  stages in the network. In a Lambda network, a channel between two switches, say S<sub>1</sub> and S<sub>2</sub>, consists of two independent links - one from S<sub>1</sub> to S<sub>2</sub> and the other from S<sub>2</sub> to S<sub>1</sub>.

The bottom stage of switches (stage 0) is designated the input/output side of the network which provides 2N network input links and 2N network output links. Each output link from the top stage (stage n-1) of one subnetwork is connected to exactly one input link of the other subnetwork. Note that the permutation here is arbitrary, a sufficient permutation rule being, for example:-

$0_{n-1}(j) \rightarrow I_{n-1}(2N-j-1), j=0..2N-1,$ where 0 and I have the same meaning as in 2.1.1. tagged with a '^' if the corresponding link is an upgoing link.

The <u>visibility</u> of switch w is defined to be the set of network outputs which can be reached by traversing a downward path from w. During path building from some source node, S, to some destination node,  $D \neq S$ , successive stages of the network are traversed, from S, in the upward direction until a switch, w, is reached from which D is visible. The request then pivots about w and traverses the downward path toward D. If stage n-1 is reached before D has become visible, then D must be connected to an output link in the other subnetwork comprising the Lambda network. The request is therefore passed over to the other subnetwork via the links at the top of the network. Because each subnetwork is equivalent to a conventional network when being traversed in the downward direction, the request can enter the subnetwork anywhere in the top stage (stage n-1). Thus the choice of permutation rule between the two subnetworks at the top

is arbitrary.

Observe that:-

- 1. A request only pivots <u>once</u>.

- 2. A request traversing  $I_{s}^{(j)}$  never traverses  $O_{s}^{(j)}$  since pivoting occurs as soon as the destination becomes visible.

But most significantly,

3. If a request is to be steered upwards from some switch, w, then the choice of which upgoing output link to take is <u>arbitrary</u>. i.e. all upgoing traversals are contention free.

This third point we now prove in the following theorem which relates to a Cube-based Lambda network. Similar results can also be derived for non cubic topologies.

**Theorem 2-1:** Let the stages of the network be labelled 0...n-1 with stage 0 associated with the input/output side of the network. Let the interconnection topology be that of the Cube i.e.

$0_{s}(\langle j_{n-1},..,j_{s+2},j_{s+1},j_{s},..,j_{1},j_{0}\rangle) \rightarrow$

$I_{s+1}(\langle j_{n-1},..., j_{s+2}, j_0, j_s, ..., j_1, j_{s+1} \rangle), s=0...n-2$

Let  $W_{s,j}$  be switch j in stage s,  $j \in [0..N-1]$ ,  $s \in [0..n-1]$ . Then: each switch in stage i, i=s+1..n-1 accessible from  $W_{s,j}$  has the same visibility.

**Proof:** Assume that we select  $0_{s}^{(a)}$ ,  $xj \leq a < x(j+1)$ , through which to steer the request. Let  $\langle a_{n-1}, .., a_{s+2}, a_{s+1}, a_{s}, .., a_{1}, a_{0} \rangle$  be the base-x expansion of a. From the definition of the Cube topology, the request is steered to  $I_{s+1}(a')$ , where  $a' = \langle a_{n-1}, .., a_{s+2}, a_{0}, a_{s}, .., a_{1}, a_{s+1} \rangle$ . The stage s+1switch associated with this input link is  $W_{s+1,a''}$  where  $a'' = \langle a_{n-1}, .., a_{s+2}, a_{0}, a_{s}, .., a_{1} \rangle$ . The downgoing output links of  $W_{s+1,a''}$ are thus the outputs  $0_{s+1,k}$  where k takes all values  $\langle a_{n-1}, .., a_{s+2}, a_{0}, a_{s}, .., a_{1}, Q \rangle$ , Q=0...x-1. Theselink to the  $I_{s}(k')$  where k' takes all values  $\langle a_{n-1}, .., a_{s+2}, Q, a_{s}, .., a_{1}, a_{0} \rangle$ , Q=0...x-1.

Applying the rule repeatedly for each stage down to stage 0, it is easy to see that the visibility of  $W_{s+1,a''}$  is the set of network outputs labelled  $\langle a_{n-1}, a_{n-2}, ..., a_{s+2}, Q_{s+1}, Q_s, ...Q_0 \rangle$ ,  $Q_i=0...x-1$ , i=0...s+1. Generally, the visibility of each switch of stage t, t=s+1...n-1, accessible from  $0_s^{(a)}(a)$ (of  $W_{s,j}$ ),  $xj \leq a < x(j+1)$  is given by  $\langle a_{n-1}, a_{n-2}, ..., a_{t+1}, Q_t, Q_{t-1}, ..., Q_1, Q_0 \rangle$ . Since  $a_{t+1}...a_{n-1}$  is the same for <u>each</u> of the upgoing outputs of  $W_{s,j}$  it follows that these visibilities are the same, i.e. the choice of which upgoing output link to take is arbitrary.

[]

Thus, a sufficient routing procedure is for all requests arriving on  $I_{s}^{(j)}$ not pivoting in stage s to be sent out on  $O_{s}^{(j)}$ . This is assumed in the analysis which follows.

## 2.2.3.2. Analysis.

In the analysis of Lambda networks we assume the same cyclical mode of operation as in 2.2.1 and 2.2.2 above. To simplify the analysis, we consider a uniform input load: at the start of a cycle, the probability that a request is presented to a network input is p for all inputs. For the time being we shall assume that the probability that a request on input i addresses output j, i, j=0..N-1 is the same for all j. The effects of locality of reference are considered in 2.2.3.2.1. below. Also, in order to correctly model the behaviour of Lambda networks, we assume that requests never traverse the same switch port twice. This implies that a request steered upwards from stage s to stage s+1 via port P is <u>not</u> directly routed from stage s+1 to stage s back through P. Thus, if the requests' source and destination addresses are the same, it is assumed that the network is not accessed at all.

In this analysis the principle performance measure is the normalised throughput,  $T_N$ , of the network, as above.

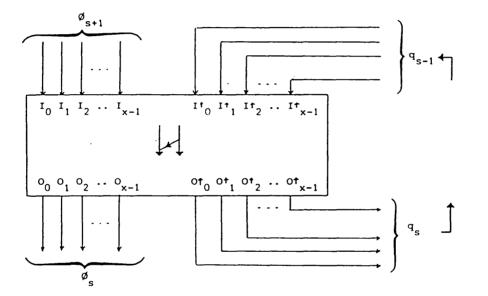

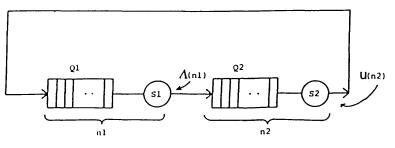

Figure 2-6 shows the layout of one component switch of a Lambda network of degree x. Here, the switch is shown with the input and output connections separated so that the direction of the flow of requests is from the top of the switch to the bottom.

In generating  $T_N$  we are concerned with the mean utilisation of the downward links at the bottom (i.e. input/output) stage of the network.

The mean utilisation of the downgoing output links of a switch in stage s (say  $\emptyset_s$ ) is dependent on:-

Figure 2-6: Lambda Switch Loading.

- 1. The utilisation of those switch inputs originating from a higher stage (stage s+1), i.e.  $P_{s+1}$ .

- 2. The utilisation of those switch inputs originating from a lower stage (stage s-1), say  $q_{s-1}$ .

In addition to the downgoing outputs of the switch (with mean utilisation  $\rho_s$ ), the switch also has outputs which are fed into switches in stage s+1.

Note that requests arriving at a switch from above will never be routed back up again. Consequently,  $q_s$  is independent of  $\rho_{s+1}$ .

It is convenient to separate the  $q_{s-1}$  terms into two components,  $q_s$  and  $r_s$  so as to simplify the expression for  $\emptyset_s$ .  $r_s$  represents the load imposed on the downgoing links of the switch by those requests which pivot at the switch and begin traversing the network downwards. Thus,

$$q_{s-1} = q_s + r_s, \quad s=1...n-1.$$

Consider now a switch in the bottom stage (stage 0) of the network. At the start of a cycle, the probability that the component attached to that switch generates a request is p, as defined by the model.

Now, with probability 1/N (assuming a random addressing distribution), the destination address will be equal to the source address and the request can bypass the network altogether.

Consequently, the  $r_0$  component is:-

$$r_0 = \frac{p(x-1)}{N}$$

and the q<sub>0</sub> component:-

$$q_0 = p \begin{pmatrix} x \\ 1 - - \\ N \end{pmatrix}$$

Note that  $r_0+q_0=p(1-(1/N))$  not p since we have excluded all requests whose source and destination addresses are the same.

Now, for each stage encountered going up into the network, the r loads will be multiplied x-fold since the visibility of stage s is x times that of stage s-1, s=1..n-1. Thus generally,

$$r_{s} = \frac{px^{s}(x-1)}{N}$$

Similarly, we get for q<sub>s</sub>:-

$$x^{s+1}$$

$q_s = p(1 - ----) s=0..n-1$

Note that  $r_s + q_s = q_{s-1}$  as can be easily verified.

One of the boundary conditions occurs at the top stage (stage n-1) of the network. Here, in a Lambda network, we expect the value of  $q_{n-1}$  to be p/2 since under the random addressing assumption, exactly half of all requests generated in one subnetwork will be ultimately routed to the other subnetwork. This is easily verified:-

$$q_{n-1} = p(1-x^n)$$

$-- N$

$= p(1 - ----)$

$= p(1 - ---)$

$= p(1 - ---)$

$= p(1 - ---)$

$= p/2$

Q.E.D.

Note that the  $q_{n-1}$  of one subnetwork form the  $\emptyset_n$  of the other subnetwork so that:-

$$\emptyset_n = q_{n-1} = -\frac{p}{2}$$

This is used as the starting point for the iteration.

From the values of  $r_s$  and  $\rho_{s+1}$  the throughput of each stage s switch can be found. However, we cannot simply apply equation [2-4] to the problem. This is because a request which pivots in stage s (thereby contributing to the  $r_s$  component) cannot be steered back through the link from which it came. Consequently, requests arriving at the switch from below are not evenly distributed among the outputs of the switch. This is not true of requests which have pivoted somewhere higher in the network, (i.e. the  $\rho_{s+1}$ )

so we shall consider, for the time being, just the contribution to  $\emptyset_s$  made by  $r_s$ .

Consider a single switch in stage s and consider only those requests which pivot about the switch and let  $\emptyset_s'$  be the contribution made to  $\emptyset_s$  by such requests.

If there are m pivoting requests present at the switch inputs then: 1.  $Pr\{a \text{ pivoting request is present on the kth upgoing input}\} = m/x$

2. Pr{output port k contains request} = 1 -  $\begin{pmatrix} x-2 \\ --- \\ x-1 \end{pmatrix}^m$

Hence:-

•

3. Pr{output k accessed} =

$$\binom{m}{x} \left(1 - \binom{x-2}{x-1} \stackrel{m-1}{x} + \binom{1}{x} - \frac{m}{x}\right) \left(1 - \binom{x-2}{x-1} \stackrel{m}{x}\right)$$

=  $1 - \binom{x-2}{x-1} \stackrel{m}{x} \left(1 + \frac{m}{x-2} \right)$

Therefore, we get :-

$\emptyset_{s}' = \Pr\{a \text{ request exists at an arbitrary output}\}$

$$= \sum_{m=0}^{x} {\binom{x}{m}} (r_{s})^{m} (1-r_{s})^{x-m} \left(1 - {\binom{x-2}{--}}^{m} {\binom{1+\frac{m}{x}}{x-2}}\right)$$

$$= 1 - \sum_{m=0}^{x} {\binom{x}{m}} (r_{s})^{m} (1 - r_{s})^{x - m} {\binom{x - 2}{- - \frac{x}{x - 1}}}^{m}$$

$$- \sum_{m=0}^{x} {\binom{x}{m}} (r_{s})^{m} (1 - r_{s})^{x - m} {\binom{x - 2}{- - \frac{x}{x - 1}}}^{m} \cdot \frac{m}{x(x - 2)}$$

$$= 1 - {\binom{1 - \frac{r_{s}}{- - \frac{x}{x - 1}}}^{x} - \frac{1}{\frac{1}{x(x - 2)}} \cdot \sum_{m=0}^{x} {\binom{x}{m}} {\binom{r_{s}(x - 2)}{- - \frac{x}{x - 1}}}^{m} \cdot m \cdot (1 - r_{s})^{x - m}$$

Now,

$$\binom{x}{m} = \frac{m x!}{m! (x-m)!} = \frac{x (x-1)!}{(x-m)! (m-1)!} = x \binom{x-1}{m-1}$$

Substituting, we get for  $\emptyset_{s}$ ',

$$\theta_{s}' = 1 - \left(1 - \frac{r_{s}}{x-1}\right)^{x} - \frac{1}{x-2} \cdot \sum_{m=1}^{x} {\binom{x-1}{m-1} \binom{r_{s}(x-2)}{x-1}}^{m} \cdot (1 - r_{s})^{x-m}$$

$$= 1 - \left(1 - \frac{r_{s}}{x-1}\right)^{x-1}$$

This is, perhaps, intuitive since for pivoting requests, only x-1 of the switch output ports are 'candidates' for that request.

Since the requests contributing to  $\emptyset_{s+1}$  are independent from those contributing to  $r_s$ , equation [2-4] can now be applied, which yields:-

with the boundary cases:-