Imperial College London Department of Electrical and Electronic Engineering

# Communication Optimization in Iterative Numerical Algorithms: An Algorithm-Architecture Interaction

Abid Rafique

January 2014

Supervised by George A. Constantinides and Nachiket Kapre

Submitted in part fulfilment of the requirements for the degree of Doctor of Philosophy in Electrical and Electronic Engineering of Imperial College London and the Diploma of Imperial College London

### Declaration

I herewith certify that all material in this dissertation that is not my own work has been properly acknowledged.

Abid Rafique

I would like to dedicate this thesis to my beloved mother (late)

### **Copyright Declaration**

The copyright of this thesis rests with the author and is made available under a Creative Commons Attribution Non-Commercial No Derivatives licence. Researchers are free to copy, distribute or transmit the thesis on the condition that they attribute it, that they do not use it for commercial purposes and that they do not alter, transform or build upon it. For any reuse or redistribution, researchers must make clear to others the licence terms of this work.

### Abstract

Trading communication with redundant computation can increase the silicon efficiency of common hardware accelerators like FPGA and GPU in accelerating sparse iterative numerical algorithms. While iterative numerical algorithms are extensively used in solving large-scale sparse linear system of equations and eigenvalue problems, they are challenging to accelerate as they spend most of their time in communication-bound operations, like sparse matrix-vector multiply (SpMV) and vector-vector operations. Communication is used in a general sense to mean moving the matrix and the vectors within the custom memory hierarchy of the FPGA and between processors in the GPU; the cost of which is much higher than performing the actual computation due to technological reasons. Additionally, the dependency between the operations hinders overlapping computation with communication. As a result, although GPU and FPGA are offering large peak floating-point performance, their sustained performance is nonetheless very low due to high communication costs leading to poor silicon efficiency.

In this thesis, we provide a systematic study to minimize the communication cost thereby increase the silicon efficiency. For small-to-medium datasets, we exploit large on-chip memory of the FPGA to load the matrix only once and then use explicit blocking to perform all iterations at the communication cost of a single iteration. For large sparse datasets, it is now a well-known idea to unroll k iterations using a matrix powers kernel which replaces SpMV and two additional kernels, TSQR and BGS, which replace vector-vector operations. While this approach can provide a  $\Theta(k)$  reduction in the communication cost, the extent of the unrolling depends on the growth in redundant computation, the underlying architecture and the memory model. In this work, we show how to select the unroll factor k in an architecture-agnostic manner to provide communication-computation tradeoff on FPGA and GPU. To this end, we exploit inverse-memory hierarchy of the GPUs to map matrix power kernel and present a new algorithm for the FPGAs which matches with their strength to reduce redundant computation to allow large k and hence higher speedups. We provide predictive models of the matrix powers kernel to understand the communication-computation tradeoff on GPU and FPGA. We highlight extremely low efficiency of the GPU in TSQR due to off-chip sharing of data across different building blocks and show how we can use on-chip memory of the FPGA to eliminate this off-chip access and hence achieve better efficiency. Finally, we demonstrate how to compose all the kernels by using a unified architecture and exploit on-chip memory of the FPGA to share data across these kernels.

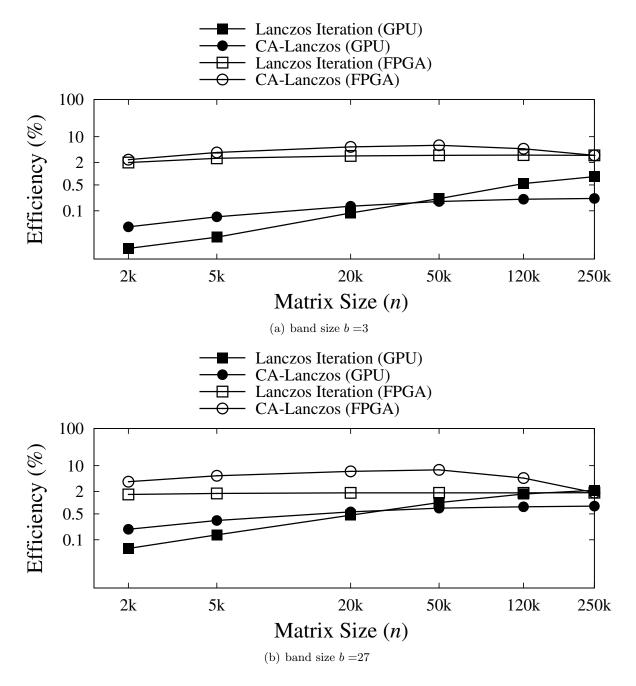

Using the Lanczos Iteration as a case study to solve symmetric extremal eigenvalue problem, we show that the efficiency of FPGAs can be increased from 1.8% to 38% for small-to-medium scale dense matrices whereas up to 7.8% for large-scale structured banded matrices. We show that although GPU shows better efficiency for certain kernels like the matrix powers kernel, the overall efficiency is even lower due to increase in communication cost while sharing

data across different kernels through off-chip memory. As the Lanczos Iteration is at the heart of all modern iterative numerical algorithms, our results are applicable to a broad class of iterative numerical algorithms.

## Acknowledgement

I would like to begin thanking my supervisor Dr. George A. Constantinides. I am grateful to him for his complete support, motivation and encouragement throughout my PhD. He has continuously guided me, and at the same time gave me enough freedom to explore my own research direction. I must acknowledge his clarity of thought and intellect to polish my ideas during our meetings. I am particularly thankful to him for keeping me focused and help me writing my thesis in a timely manner. Lastly, I am also grateful to him for providing me enough travel opportunities to present my work in reputed conferences.

I would like to acknowledge my co-supervisor, Dr. Nachiket Kapre. He has not only helped me in research but also sharpen my presentation skills. I am thankful to him for the time he spent in multiple iterations of the papers.

I consider myself very fortunate to have two great supervisors. I would be indebted to them for their guidance and supervision. They helped me learn key skills necessary for independent research that will be helpful for the rest of my life.

I had the company of many brilliant colleagues at Imperial College with whom I had interesting and fruitful discussions. I would particularly thank to Dr. David Boland, Dr. Juan Jerez, Dr. Samual Bayliss, Dr. Shakil Ahmed, Dr. Ammar Hassan and Dr. Andrea Suardi. I would particularly thank Michael Anderson and Mark Hoemmen at PARLab, UC Berkeley who took time to revise some of my work and provided feedback that helped me in improving the overall quality.

My time at Imperial College would not have been the same without my friends. They kept me cheerful and encourage during the hard times working towards my PhD. I would like to thank particularly Qazi Rashid Hamid, Usman Adeel, Muhammad Usman and Hafiz-Ul-Asad.

On a personal note, I would like to express gratitude to my family and in particular my mother who is no more in this world to share these moments. She had been a continuous source of inspiration and great love.

Finally, I would like to acknowledge my wife, Nazia, and the greatest gift of God, *i.e.* my daughter Fatima. I am thankful to them for the love and patience they have shown throughout my PhD.

# Contents

| 1        | Intr | oduction                                                                                                                | <b>22</b> |

|----------|------|-------------------------------------------------------------------------------------------------------------------------|-----------|

|          | 1.1  | Case Study: Lanczos Iteration for Solving Symmetric Extremal Eigenvalue Problem                                         | 24        |

|          | 1.2  | Thesis Organization                                                                                                     | 25        |

|          | 1.3  | Statement of Originality                                                                                                | 27        |

|          | 1.4  | Publications                                                                                                            | 28        |

| <b>2</b> | App  | olied Numerical Linear Algebra                                                                                          | 29        |

|          | 2.1  | Standard Problems                                                                                                       | 29        |

|          | 2.2  | Problem Structure                                                                                                       | 30        |

|          |      | 2.2.1 Dense                                                                                                             | 30        |

|          |      | 2.2.2 Sparse                                                                                                            | 30        |

|          |      | 2.2.3 Structured Sparse                                                                                                 | 31        |

|          | 2.3  | Numerical Methods                                                                                                       | 32        |

|          |      | 2.3.1 Direct Methods                                                                                                    | 32        |

|          |      | 2.3.2 Iterative Methods                                                                                                 | 33        |

|          | 2.4  | Thesis Scope                                                                                                            | 34        |

|          | 2.5  | Symmetric Extremal Eigenvalue Problem                                                                                   | 35        |

|          |      | 2.5.1 Applications $\ldots$                                                                                             | 36        |

|          |      | 2.5.2 Iterative Methods for Symmetric Extremal Eigenvalue Problem                                                       | 37        |

|          | 2.6  | Computational Kernels of the Lanczos Iteration                                                                          | 39        |

|          | 2.7  | Communication and performance issues                                                                                    | 40        |

|          |      | 2.7.1 Communication is Data Movement                                                                                    | 40        |

|          |      | 2.7.2 Modelling Performance                                                                                             | 40        |

|          |      | 2.7.3 Communication is expensive                                                                                        | 41        |

|          | 2.8  | Communication in the Lanczos Iteration                                                                                  | 42        |

|          |      | 2.8.1 Sparse matrix-vector multiply                                                                                     | 42        |

|          |      | 2.8.2 $axpy$ and dot products $\ldots$ | 44        |

|          | 2.9  | Avoiding Communication in the Lanczos Iteration                                                                         | 44        |

|          |      | 2.9.1 Block Lanczos                                                                                                     | 45        |

|          |      | 2.9.2 Communication-Avoiding Lanczos                                                                                    | 46        |

|          | 2.10 | Computational Kernels of CA-Lanczos                                                                                     | 49        |

|          |      | 2.10.1 Matrix Powers Kernel                                                                                             | 49        |

|          |      | 2.10.2 QR Factorization $\ldots$                                                                                        | 52        |

|          |      | 2.10.3 Block Gram Schmidt Orthogonalization                                                                             | 55        |

|          | 2.11 | Summary and Conclusion                                                                                                  | 55        |

| 3        | Cor | mputing Platforms                                                       | 57        |

|----------|-----|-------------------------------------------------------------------------|-----------|

|          | 3.1 | Single-Core Microprocessor                                              | 57        |

|          |     | 3.1.1 Pipeline Parallelism                                              | 57        |

|          |     | 3.1.2 Out of order execution                                            | 58        |

|          |     | 3.1.3 Data-level Parallelism                                            | 58        |

|          |     | 3.1.4 Thread-level Parallelism                                          | 59        |

|          |     | 3.1.5 Communication                                                     | 59        |

|          | 3.2 | Multi-Core                                                              | 61        |

|          | 3.3 | Many-Core                                                               | 62        |

|          |     | 3.3.1 Graphical Processing Unit                                         | 62        |

|          |     | 3.3.2 Intel Xeon Phi                                                    | 64        |

|          | 3.4 | Custom Computing–Field Programmable Gate Arrays                         | 65        |

|          | 3.5 | Architectural Comparison                                                | 66        |

| 4        |     | biding Communication in Iterative Numerical Algorithms for Small-to-    |           |

|          | Me  |                                                                         | <b>68</b> |

|          | 4.1 |                                                                         | 69        |

|          |     | 4.1.1 Multiple Minimum Eigenvalue Problems in Interior-Point Method for |           |

|          |     |                                                                         | 69        |

|          |     |                                                                         | 69        |

|          | 4.2 |                                                                         | 70        |

|          |     | 1 0                                                                     | 71        |

|          |     |                                                                         | 72        |

|          | 4.3 |                                                                         | 72        |

|          | 4.4 |                                                                         | 73        |

|          |     |                                                                         | 73        |

|          |     | 4.4.2 FPGAs vs. GPU                                                     | 74        |

|          |     | 4.4.3 Parallelism Potential                                             | 74        |

|          |     |                                                                         | 76        |

|          |     |                                                                         | 77        |

|          |     |                                                                         | 77        |

|          | 4.5 |                                                                         | 78        |

|          | 4.6 |                                                                         | 80        |

|          |     |                                                                         | 80        |

|          |     |                                                                         | 81        |

|          |     |                                                                         | 82        |

|          |     | v                                                                       | 83        |

|          | 4.7 | Summary                                                                 | 83        |

| <b>5</b> | Ma  | trix Powers Kernel                                                      | 85        |

|          | 5.1 | Algorithms for Matrix Powers Kernel                                     | 87        |

|          | 5.2 | Related Work                                                            | 88        |

|   | 5.3   | Matrix Powers Kernel on a GPU                                                    |

|---|-------|----------------------------------------------------------------------------------|

|   |       | 5.3.1 GPU Architecture                                                           |

|   |       | 5.3.2 Partitioning Strategy–One Partition Per Thread Block                       |

|   |       | 5.3.3 GPU Optimizations                                                          |

|   |       | 5.3.4 Kernels                                                                    |

|   |       | 5.3.5 Modelling Performance                                                      |

|   |       | 5.3.6 Performance Optimization                                                   |

|   | 5.4   | Mapping Matrix Powers Kernel to FPGA                                             |

|   |       | 5.4.1 Proposed Hybrid Matrix Powers Kernel                                       |

|   |       | 5.4.2 Custom Hardware Design                                                     |

|   |       | 5.4.3 Modelling Performance                                                      |

|   |       | 5.4.4 Resource-Constrained Methodology                                           |

|   | 5.5   | Evaluation Methodology                                                           |

|   | 5.6   | Results                                                                          |

|   |       | 5.6.1 Sensitivity to Algorithmic Parameters                                      |

|   |       | 5.6.2 Performance Comparison                                                     |

|   | 5.7   | Architectural Insight                                                            |

|   |       | 5.7.1 Sensitivity to GPU Architectural Parameters                                |

|   |       | 5.7.2 Sensitivity to FPGA Architectural Parameters                               |

|   | 5.8   | Summary                                                                          |

| C | T- 11 | -Skinny OR Factorization 110                                                     |

| 6 | 6.1   | -Skinny QR Factorization         110           Background         112            |

|   | 0.1   | 6.1.1 Tall-Skinny QR                                                             |

|   |       | 6.1.1       Tan-Skinny QR       112         6.1.2       Householder QR       114 |

|   | 6.2   | Related Work         114                                                         |

|   | 6.3   | Proposed Architecture                                                            |

|   | 0.5   | 6.3.1       Parallelism                                                          |

|   |       | 6.3.2 Work vs. Critical Latency                                                  |

|   |       | 6.3.3 Parallel Architecture for Householder QR                                   |

|   |       | 6.3.4 Pipeline Parallelism for Mapping TSQR                                      |

|   |       | 6.3.5 I/O Considerations                                                         |

|   | 6.4   | Evaluation Methodology                                                           |

|   | 6.5   | Results                                                                          |

|   | 0.0   | 6.5.1 FPGA Performance Evaluation                                                |

|   |       | 6.5.2 Comparison with GPU                                                        |

|   |       | 6.5.3 Comparison with Multi-Cores and Related FPGA Work                          |

|   | 6.6   | Summary                                                                          |

|   | 0.0   |                                                                                  |

| 7 |       | nmunication Optimization in Iterative Numerical Algorithms for Large-            |

|   |       | le Problems 128                                                                  |

|   | 7.1   | Basic Linear Algebra Kernels in CA-Lanczos                                       |

|   |       | 7.1.1 Matrix Powers Kernel                                                       |

|   |     | 7.1.2  | Block Gram-Schmidt Orthogonalization                                                                                                         |

|---|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 7.1.3  | QR Factorization                                                                                                                             |

|   | 7.2 | Relate | d Work                                                                                                                                       |

|   |     | 7.2.1  | Communication Optimization                                                                                                                   |

|   |     | 7.2.2  | Composition                                                                                                                                  |

|   | 7.3 | Minim  | izing Communication For GPU                                                                                                                  |

|   |     | 7.3.1  | Lanczos Iteration on GPU                                                                                                                     |

|   |     | 7.3.2  | CA-Lanczos on GPU                                                                                                                            |

|   |     | 7.3.3  | Performance Analysis                                                                                                                         |

|   | 7.4 | Minim  | izing Communication For FPGAs                                                                                                                |

|   |     | 7.4.1  | On-chip Memory Driven Data Partitioning                                                                                                      |

|   |     | 7.4.2  | Time-Multiplexed FPGA Implementation of CA-Lanczos $\ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                  |

|   |     | 7.4.3  | Compute Schedule                                                                                                                             |

|   |     | 7.4.4  | Performance Model                                                                                                                            |

|   |     | 7.4.5  | Resource-Constrained Framework                                                                                                               |

|   | 7.5 | Experi | imental Setup                                                                                                                                |

|   | 7.6 | Evalua | ation $\ldots \ldots \ldots$ |

|   |     | 7.6.1  | Impact of $k$ on FPGA Performance                                                                                                            |

|   |     | 7.6.2  | Performance Comparison with GPU                                                                                                              |

|   | 7.7 | Summ   | ary                                                                                                                                          |

| 8 | Con | clusio | n 148                                                                                                                                        |

|   | 8.1 | Future | e Work                                                                                                                                       |

|   |     | 8.1.1  | Large Sparse Problems                                                                                                                        |

|   |     | 8.1.2  | Low Power Applied Linear Algebra                                                                                                             |

|   |     | 8.1.3  | Parameterizable Tall-Skinny QR Factorization                                                                                                 |

|   |     | 8.1.4  | Fixed-Point QR Factorization                                                                                                                 |

# List of Figures

| 1.1          | FPGA and GPU problem setting for solving small-to-medium scale problems.                                                                                              |    |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|              | Step is not actually performed for both architectures                                                                                                                 | 26 |

| 1.2          | FPGA and GPU problem setting for solving large-scale problems. Step is not                                                                                            |    |

|              | actually performed for both architectures                                                                                                                             | 27 |

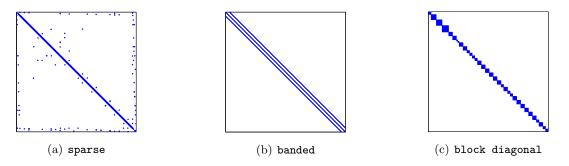

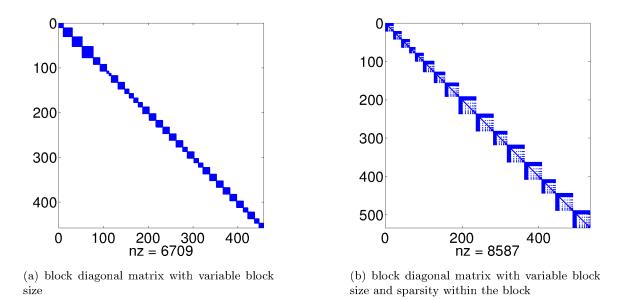

| 2.1          | Structured Sparse Matrices                                                                                                                                            | 31 |

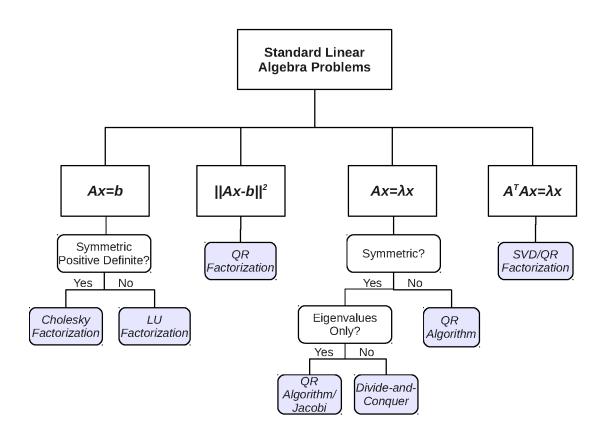

| 2.2          | A taxonomy of direct methods for solving standard linear algebra problems. A                                                                                          |    |

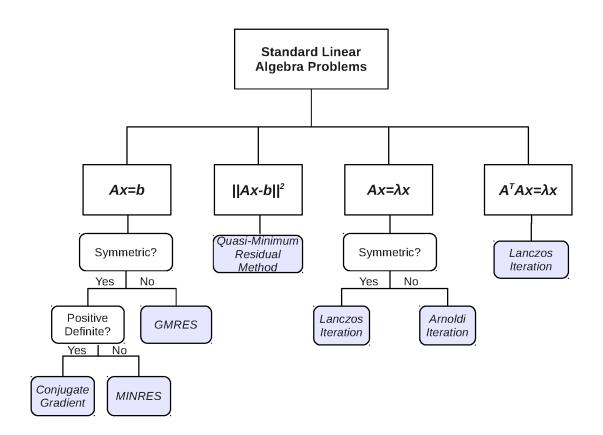

| 2.3          | positive definite matrix is the one where all the eigenvalues are greater than zero.<br>A taxonomy of iterative methods for solving standard linear algebra problems. | 33 |

|              | A positive definite matrix is the one whose all eigenvalues are greater than zero.                                                                                    | 35 |

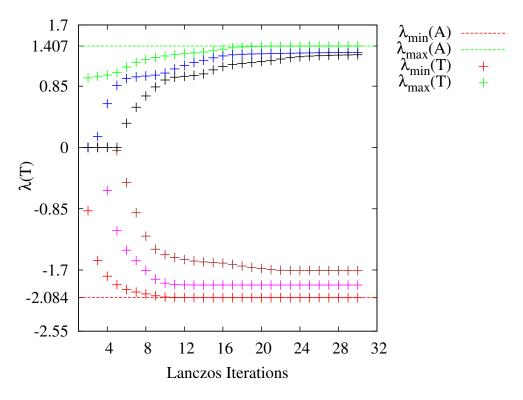

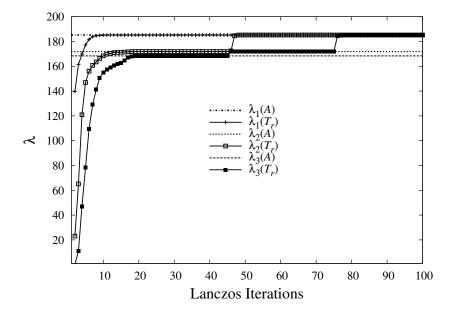

| 2.4          | Lanczos Convergence                                                                                                                                                   | 39 |

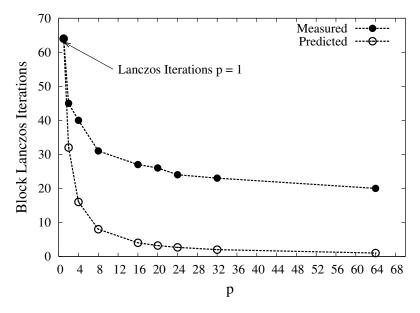

| 2.5          | Iterations vs. $p$ for extremal eigenvalue computation with accuracy $10^{-3}$ . The                                                                                  |    |

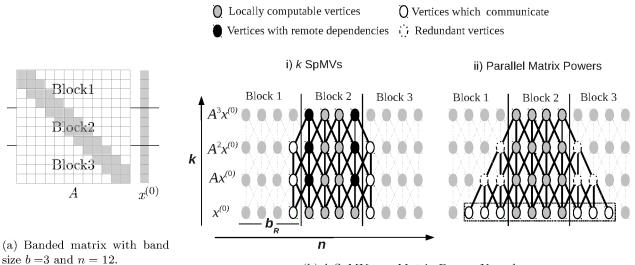

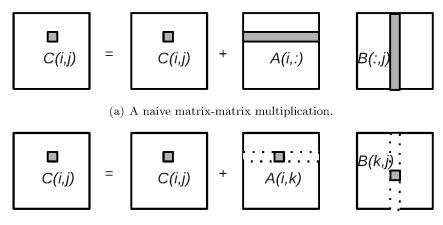

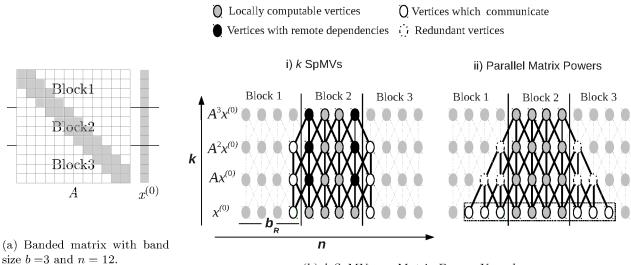

| 2.6          | predicted value is calculated theoretically and not with any model $k$ SpMVs vs. parallel matrix powers kernel for a matrix with size $n = 12$ , band                 | 46 |

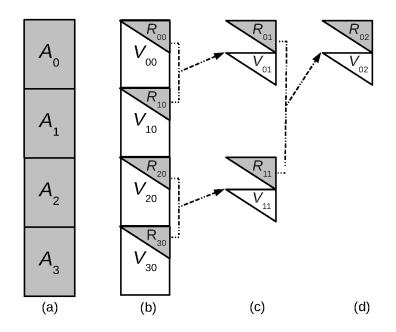

|              | size $b = 3$ , number of levels $k = 3$ and number of blocks $N_q = 3$                                                                                                | 50 |

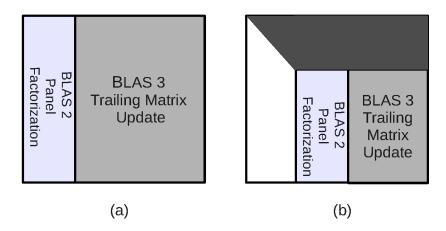

| 2.7          | Computations within Blocked Householder QR.                                                                                                                           | 53 |

| 2.8          | Tall-Skinny QR                                                                                                                                                        | 54 |

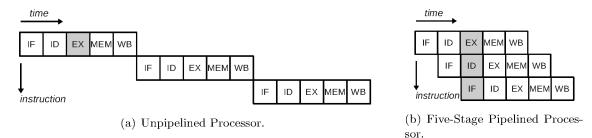

| 3.1          | Pipeline Parallelism.                                                                                                                                                 | 58 |

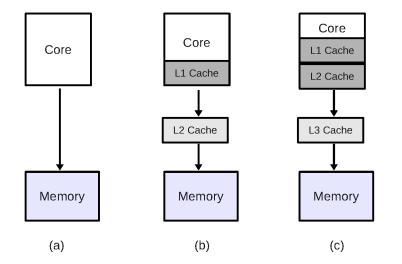

| 3.2          | Memory Hierarchy in Single-Core Microprocessors (a) Un-Cached (b) L1 (on-                                                                                             |    |

|              | chip) and L2 (off-chip) Cache (c) L1 and L2 (on-chip), L3 (off-chip) Cache                                                                                            | 59 |

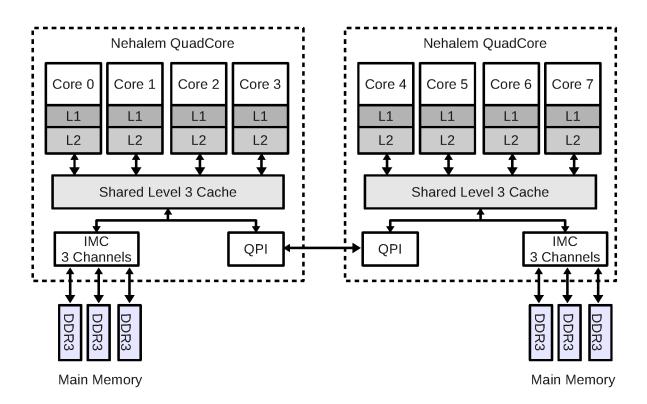

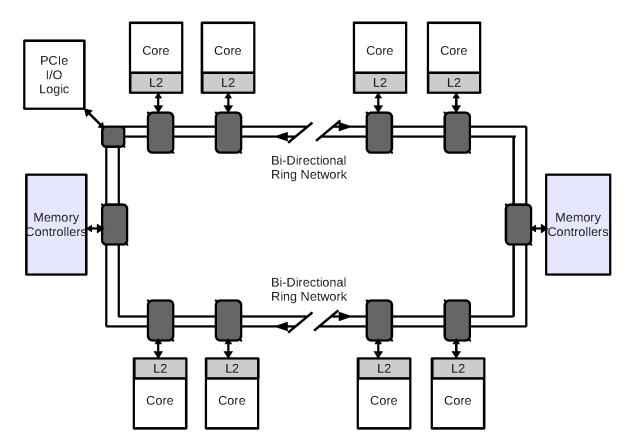

| $3.3 \\ 3.4$ | Linear algebra with cache blocking                                                                                                                                    | 61 |

|              | memory controller and Quick Processor Interconnect respectively.                                                                                                      | 62 |

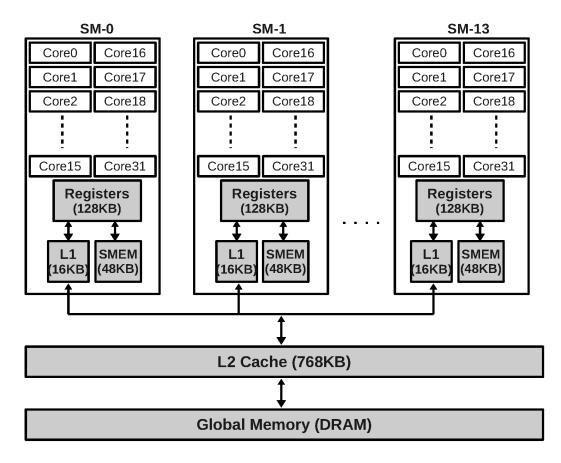

| 3.5          | Nvidia C2050 Fermi Architecture [71]. SM stands for streaming multiprocessor.                                                                                         | 63 |

| 3.6          | Intel Xeon Phi Coprocessor KNC Card SE10P.                                                                                                                            | 64 |

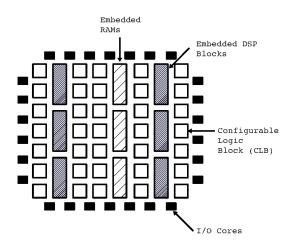

| 3.7          | Partial FPGA schematic illustrating its architecture containing CLBs as small programmable ROMs, embedded RAMs in the region of 18k bit, DSP blocks as                |    |

|              | dedicated multiply/add circuitry. The routing fabric is not shown                                                                                                     | 66 |

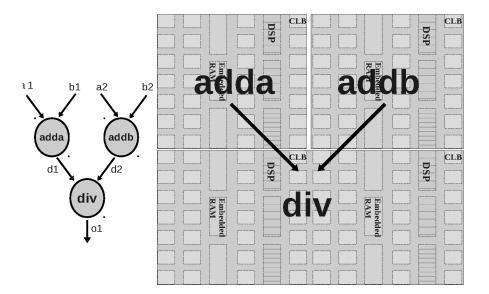

| 3.8          | Spatial Computation using FPGAs.                                                                                                                                      | 66 |

| 4.1          | Sparse Symmetric Matrices                                                                                                                                             | 70 |

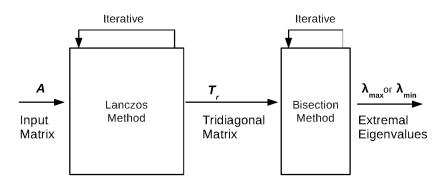

| 4.2          | Symmetric Extremal Eigenvalue Computation.                                                                                                                            | 70 |

| 4.3          | The Lanczos Iteration convergence to the maximum eigenvalue of $A$                                                                                                    | 71 |

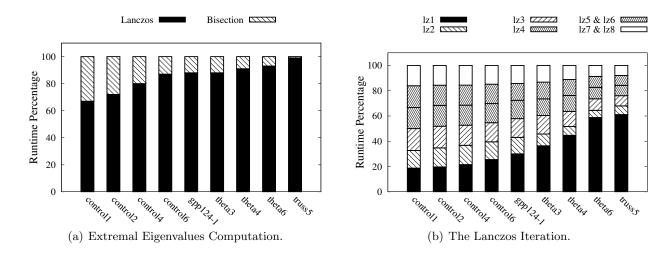

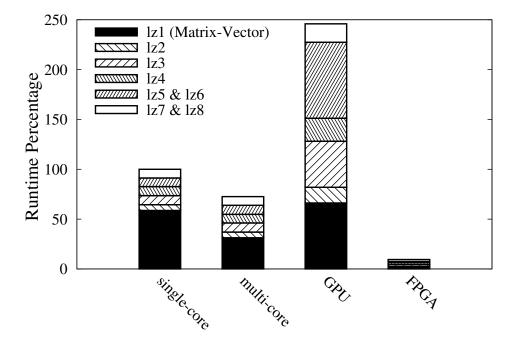

| 4.4          | Sequential Runtime Analysis.                                                                                                                                          | 72 |

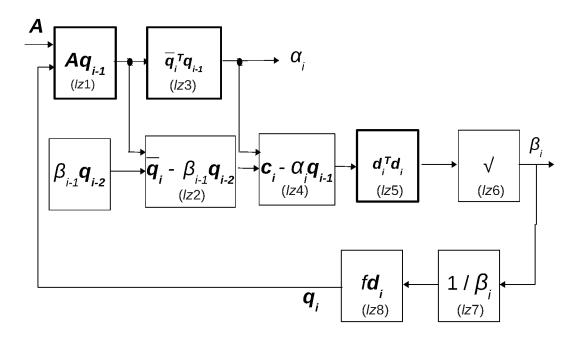

| 4.5          | Data flow graph of the Lanczos Iteration.                                                                                                                             | 75 |

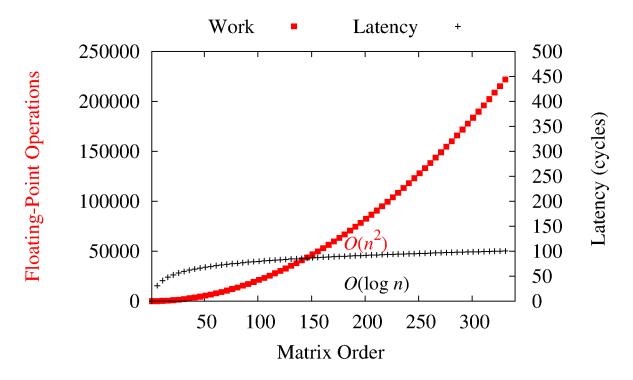

| 4.6  | Work vs. Latency                                                                        | 75  |

|------|-----------------------------------------------------------------------------------------|-----|

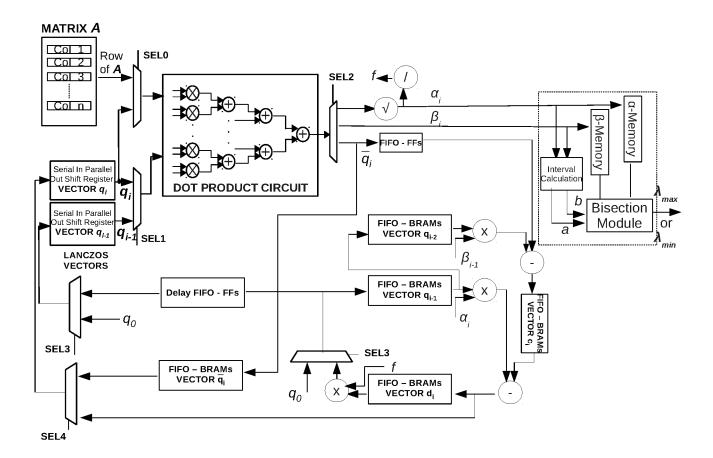

| 4.7  | Partial schematic for the implementation of the Lanczos Iteration and the bisec-        |     |

|      | tion method displaying main components including a dot product circuit module,          |     |

|      | FIFOs for storing Lanczos vectors $(q_{i-1}, q_{i-2})$ banked memory arrangement for    |     |

|      | matrix A, two memories for storing $\alpha_i$ and $\beta_i$ and a Bisection Module      | 76  |

| 4.8  | Asymptotic analysis of maximum number of problems.                                      | 78  |

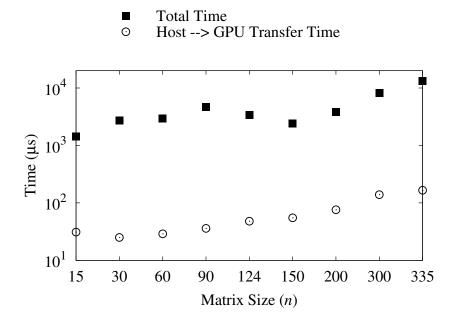

| 4.9  | Total time vs. data transfer from host to GPU (Nvidia C2050 Fermi) with data            |     |

|      | averaged over 20 runs. The input matrix $A$ (from benchmarks in Table 4.2) is           |     |

|      | transferred only once and the Lanczos Iteration is run until we get an error less       |     |

|      | than $10^{-5}$ in the maximum eigenvalue.                                               | 79  |

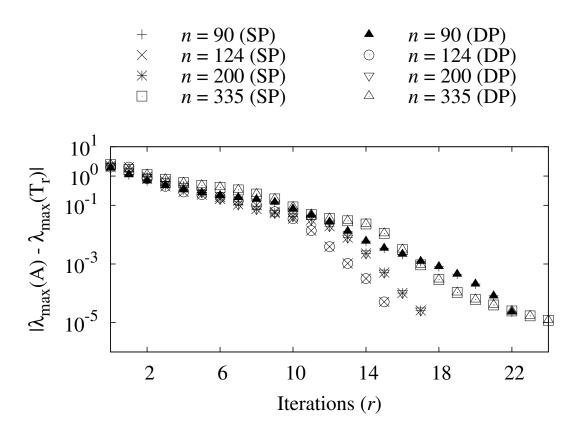

| 4.10 | Single-precision (SP) vs. Double-precision (DP) on Nvidia C2050 Fermi. The              |     |

|      | input matrix $A$ is transferred only once and the Lanczos Iteration is run until we     |     |

|      | get an error less than $10^{-5}$ in the maximum eigenvalue                              | 80  |

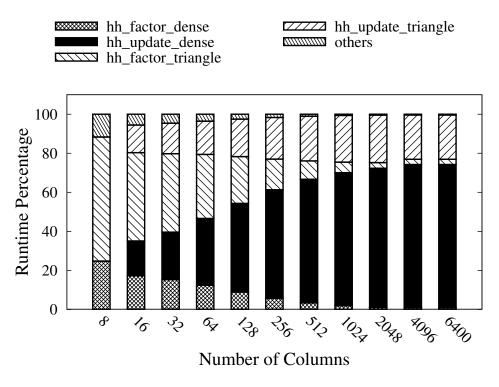

| 4.11 | Runtime Breakdown (truss5).                                                             | 82  |

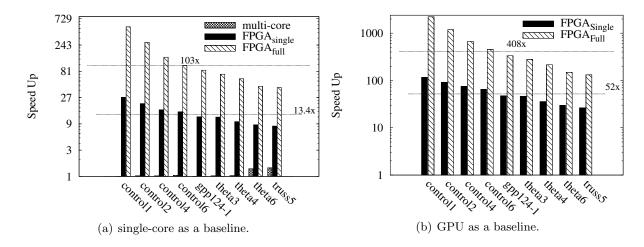

| 4.12 | Performance Comparison ('single' is for 1 problem on FPGA, 'full' is for P prob-        |     |

|      | lems on FPGA).                                                                          | 83  |

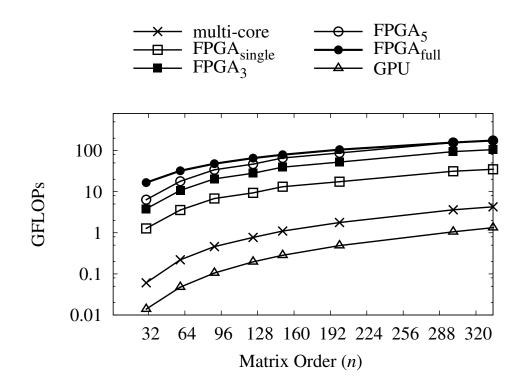

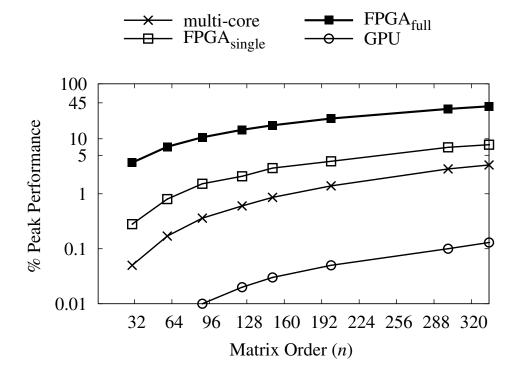

| 4.13 | Raw Performance Comparison ('single' is for 1, 'full' is for P problems)                | 84  |

| 4.14 | Efficiency Comparison ('single' is for 1, 'full' is for P problems)                     | 84  |

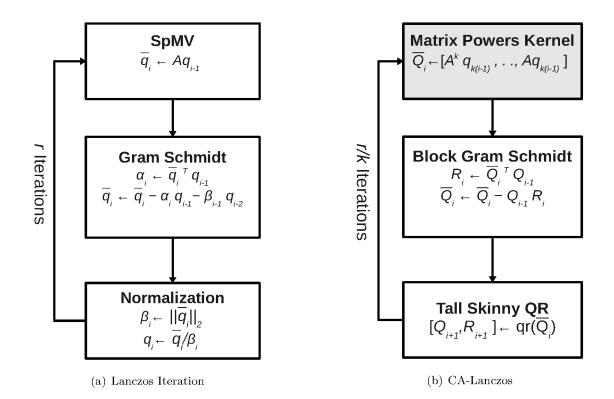

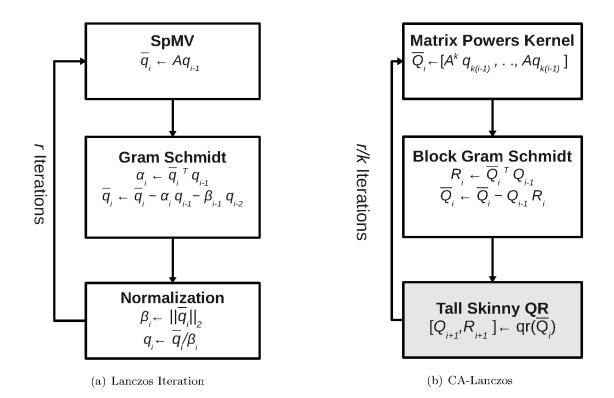

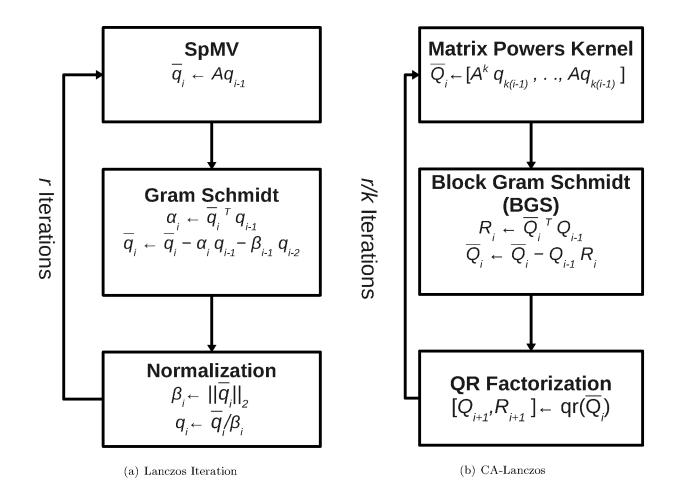

| 5.1  | Lanczos Iteration vs. Communication-Avoiding Lanczos (CALanczos) with em-               |     |

|      | phasis on the Matrix Powers Kernel                                                      | 86  |

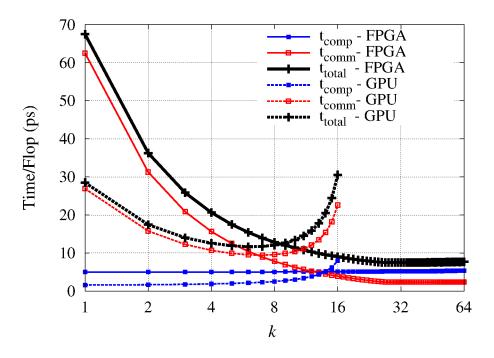

| 5.2  | Computation-communication tradeoff for a banded matrix with band size 27 and            |     |

|      | $n=1{\rm M}$ on a Virtex<br>6-SX475T FPGA and C2050 Fermi GPU                           | 86  |

| 5.3  | k SpMVs vs. parallel matrix powers kernel for a matrix with size $n = 12$ , band        |     |

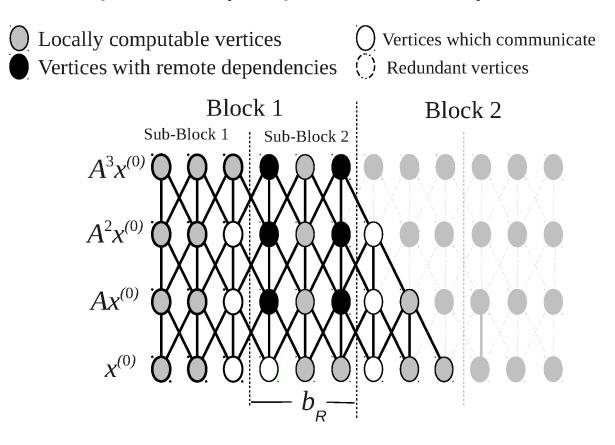

|      | size $b = 3$ , number of levels $k = 3$ and number of blocks $N_q = 3$                  | 88  |

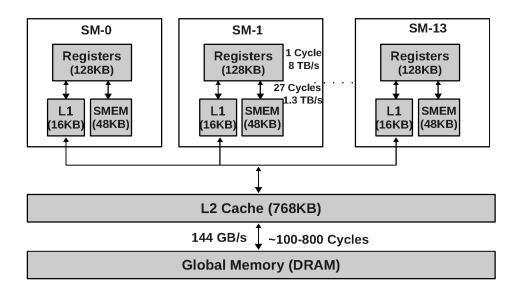

| 5.4  | GPU Architecture (Nvidia C2050 Fermi).                                                  | 90  |

| 5.5  | GPU Optimizations ( $b = 9, N_T = 512, k = 8$ )                                         | 92  |

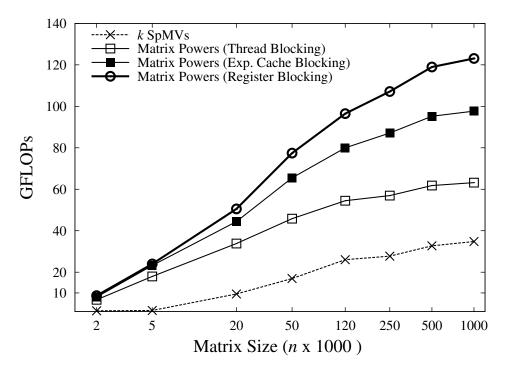

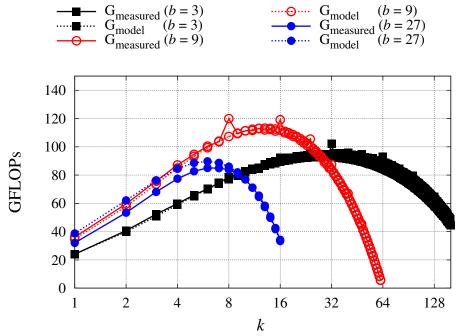

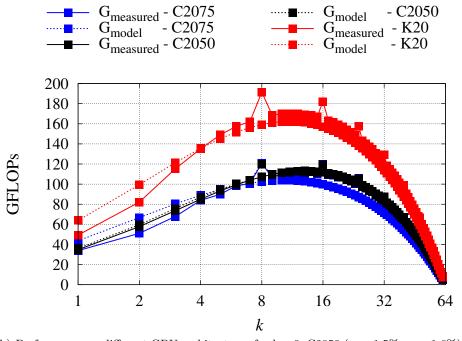

| 5.6  | Matrix powers kernel performance (GFLOPs vs. $k$ ), modelled vs. measured for           |     |

|      | n = 1M                                                                                  | 95  |

| 5.7  | Proposed hybrid matrix powers graph for $n = 12, k = 3, b = 3$ and number of            |     |

|      | blocks $N_q = 2$                                                                        | 97  |

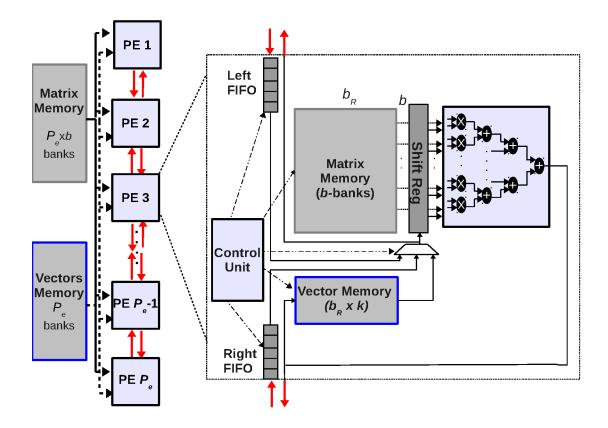

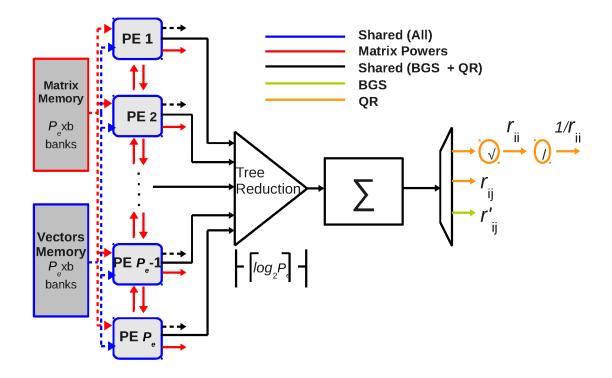

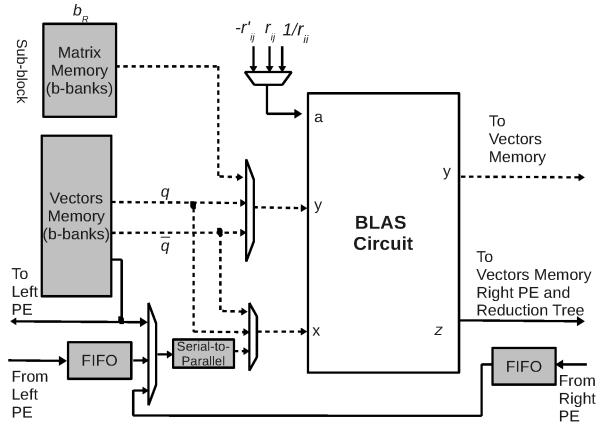

| 5.8  | FPGA Data-path for Matrix Powers Kernel.                                                | 98  |

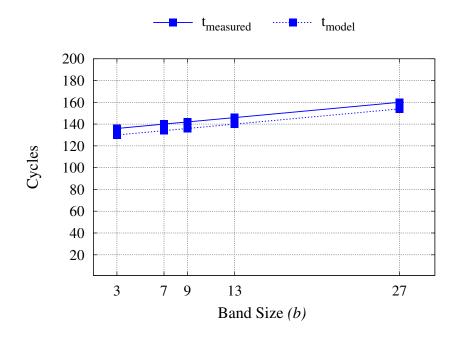

| 5.9  | FPGA performance, modelled vs. measured (Modelsim), here $b_R$ is equal to 128.         | 101 |

| 5.10 | Algorithmic Sensitivity– GPU performance as a function of algorithmic param-            |     |

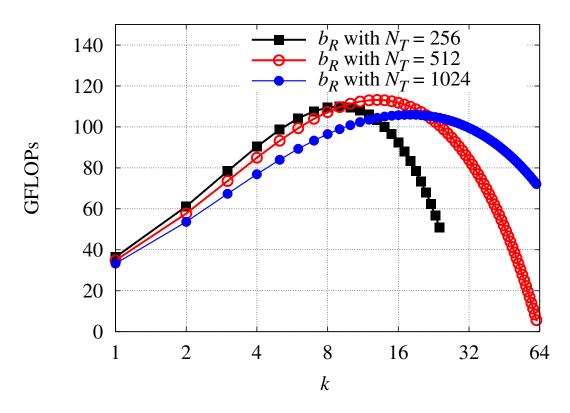

|      | eter k for different values of $b_R$ for a matrix with band size $b = 9$ and $n = 1$ M. |     |

|      |                                                                                         | 103 |

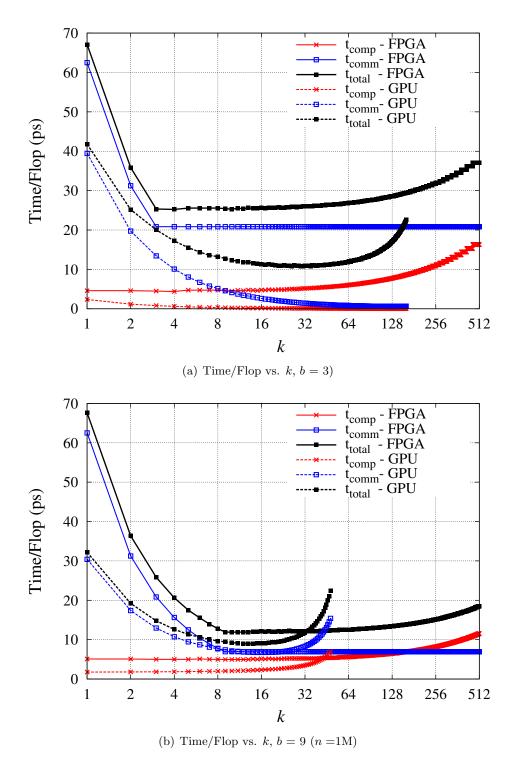

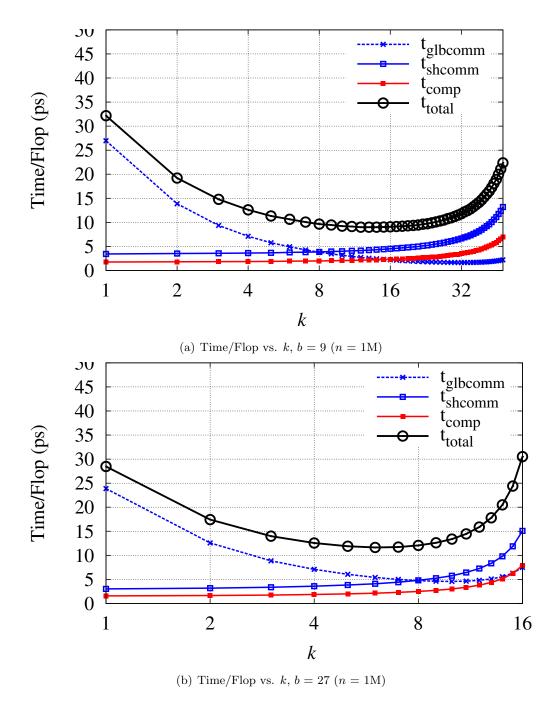

| 5.11 | Algorithmic Sensitivity for FPGA and GPU $(n = 1M)$                                     | 104 |

| 5.12 | Analyzing performance limiting factors of matrix powers kernel on C2050 GPU             | 105 |

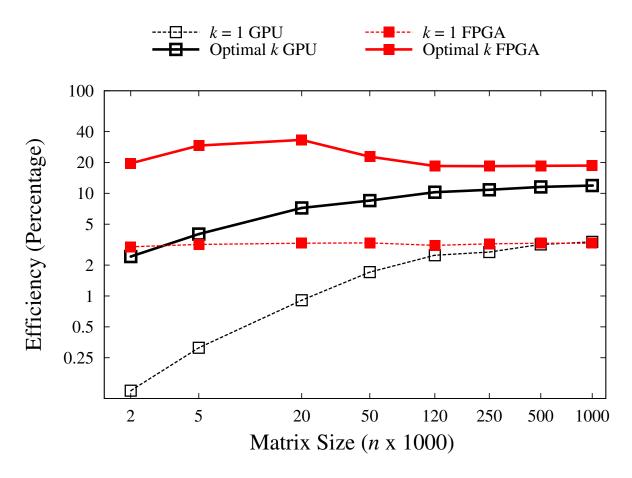

| 5.13 | Efficiency of FPGA and GPU as a percentage of peak single-precision floating-           |     |

|      | point performance $(b = 9)$                                                             | 106 |

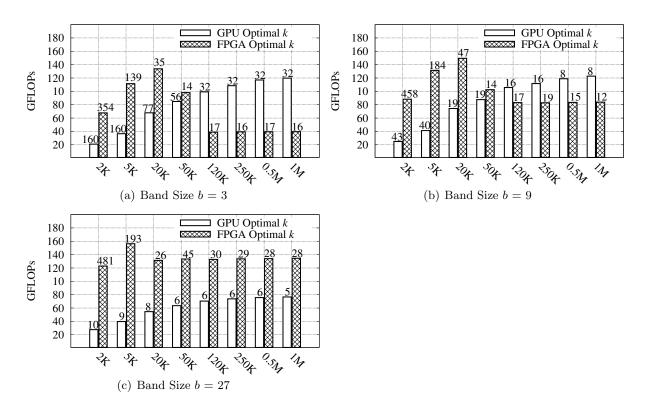

| 5.14 | Matrix Powers Performance Comparison vs. Matrix Size. The optimal values of             |     |

|      | k are mentioned on the top of the bar for both FPGA and GPU                             | 108 |

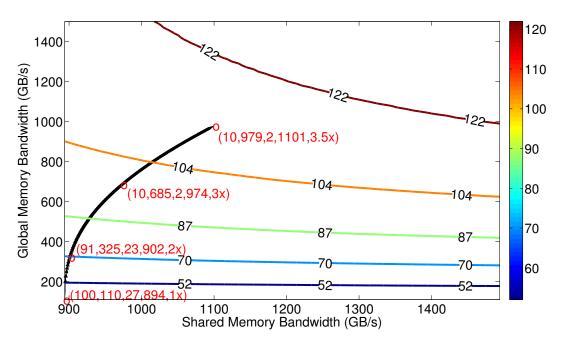

| 5.15        | Architectural Sensitivity– GPU performance contours in GFLOPs as a function<br>of global memory bandwidth ( $\beta_{glb}$ ) and shared memory bandwidth ( $\beta_{sh}$ ) for                       |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | band size $b = 9$ and $n = 1$ M. Specific points (in red) on the steepest ascent                                                                                                                   |

|             | curve (in black) are shown representing $(\alpha_{glb}, \beta_{glb}, \alpha_{sh}, \beta_{sh}, \frac{L_{base}}{L_{pred}})$ where $L_{base}$ is                                                      |

|             | the performance obtained on C2050 GPU. $\alpha_{glb}$ and $\alpha_{sh}$ are in cycles whereas $\beta_{glb}$                                                                                        |

| <b>F</b> 10 | and $\beta_{sh}$ are in GB/s                                                                                                                                                                       |

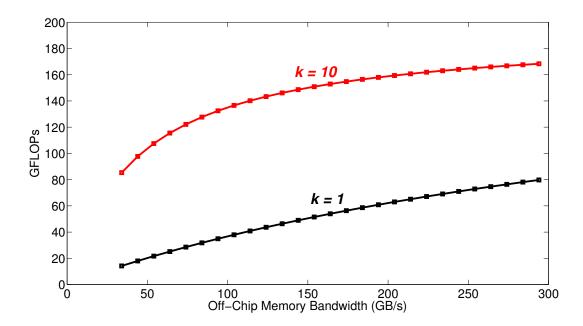

| 5.10        | Architectural Sensitivity– FPGA performance in GFLOPs as a function of off-                                                                                                                        |

|             | chip memory bandwidth $(\beta_{glb})$ for band size $b = 9$ and $n = 1$ M. The starting                                                                                                            |

|             | point of the curves is a Virtex6-SX475T architecture with an off-chip bandwidth                                                                                                                    |

|             | of 34 GB/s                                                                                                                                                                                         |

| 6.1         | Lanczos Iteration vs. Communication-Avoiding Lanczos (CALanczos) with em-                                                                                                                          |

|             | phasis on QR factorization of a tall-skinny matrix $(A \in \mathbb{R}^{n1 \times n1}, \overline{Q_i} \in \mathbb{R}^{n1 \times k},$                                                                |

|             | $R_i \in \mathbb{R}^{k \times k}, q_i \in \mathbb{R}^{n1 \times 1}, n1 \gg k) \dots $        |

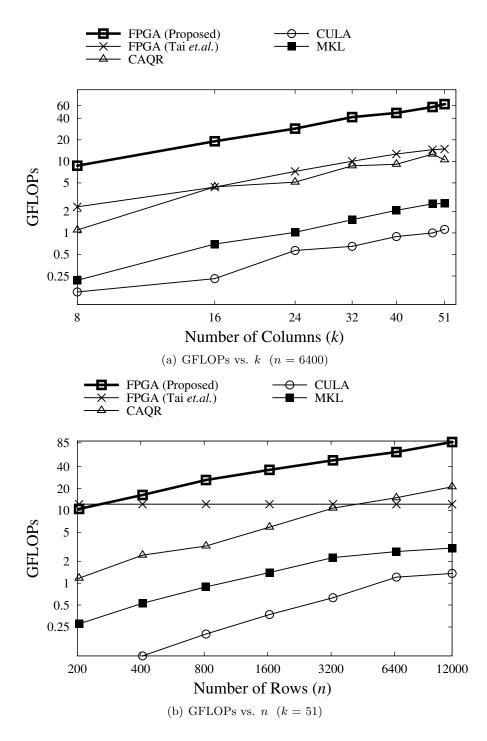

| 6.2         | Performance Scaling Trends for double-precision QR Factorization (No. of rows                                                                                                                      |

|             | n = 6400) 112                                                                                                                                                                                      |

| 6.3         | Performance Scaling Trends for double-precision QR Factorization (No. of columns                                                                                                                   |

|             | k = 51)                                                                                                                                                                                            |

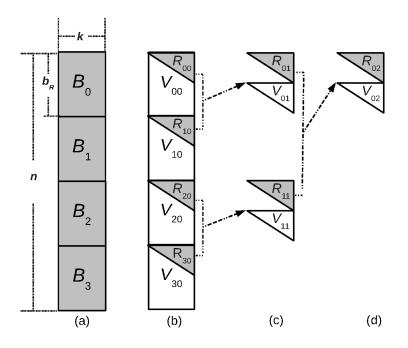

| 6.4         | Tall-Skinny QR Facotorization [33], $B = \overline{Q_i}$ , (a) local QR stage. (b, c & d) merge                                                                                                    |

|             | stage                                                                                                                                                                                              |

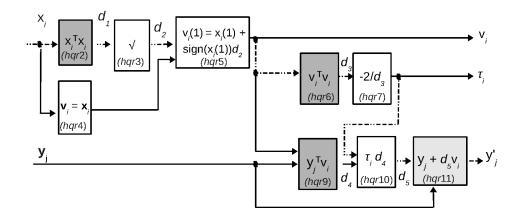

| 6.5         | Householder QR DFG showing the dark grey blocks for $ddot$ and the light grey                                                                                                                      |

|             | block for $axpy$ . The critical path of the Householder QR is shown as the blocks                                                                                                                  |

|             | connected using dotted arrows                                                                                                                                                                      |

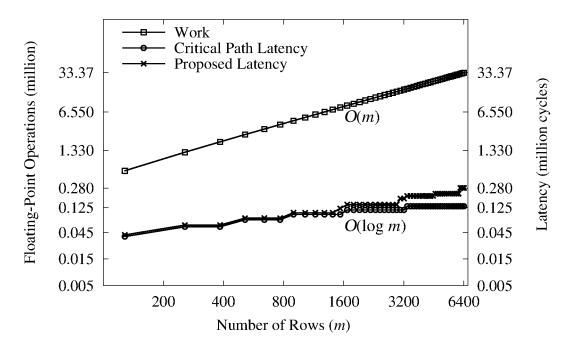

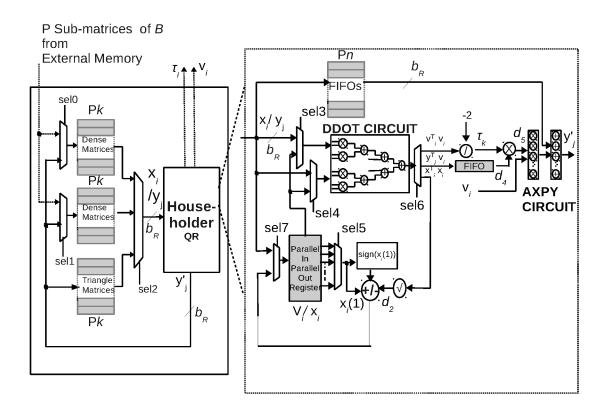

| 6.6         | Work vs. Critical Latency $(k = 51)$                                                                                                                                                               |

| 6.7         | Parallel Architecture for TSQR, Dense Matrices memory stores $B_i$ s whereas Tri-                                                                                                                  |

|             | angle Matrices memory stores intermediate $R$ factors                                                                                                                                              |

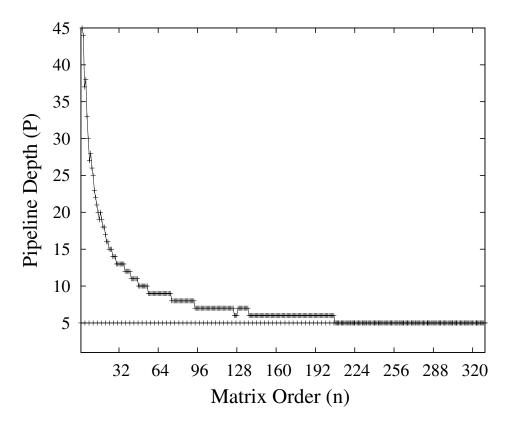

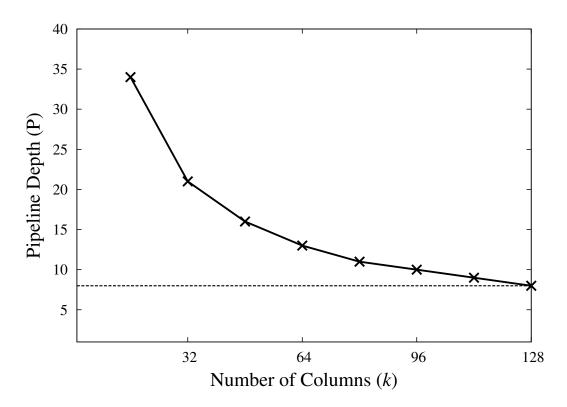

| 6.8         | Pipeline depth of proposed FPGA design                                                                                                                                                             |

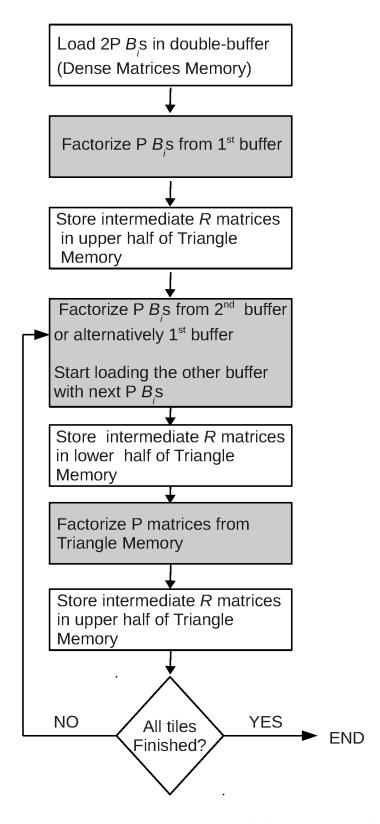

| 6.9         | Mapping of TSQR, $B_i s \in \mathbb{R}^{2k \times k}$ whereas $R \in \mathbb{R}^{k \times k}$                                                                                                      |

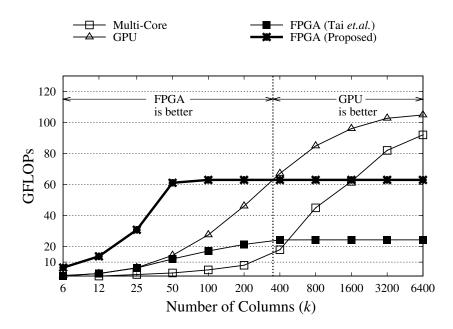

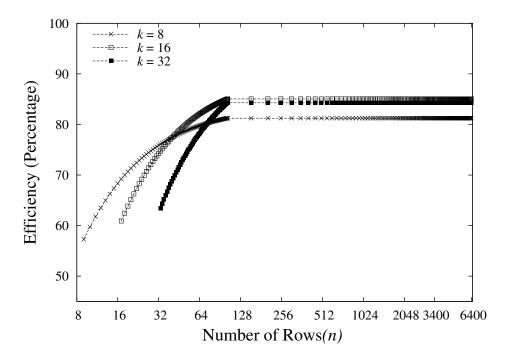

| 6.10        | Efficiency of proposed FPGA design as percentage of its peak performance $124$                                                                                                                     |

| 6.11        | GPU Performance Analysis (Number of Rows = 6400)                                                                                                                                                   |

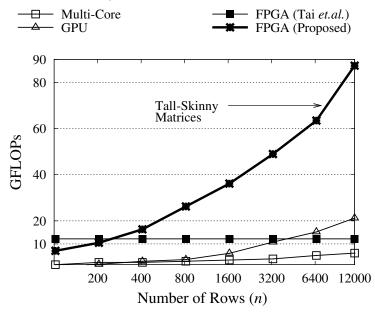

| 6.12        | Performance Comparison with Multi-Cores (Intel MKL), GPUs (CULA, CAQR),                                                                                                                            |

|             | and best FPGA work                                                                                                                                                                                 |

| 7.1         | Lanczos Iteration vs. Communication-Avoiding Lanczos (CA-Lanczos) ( $A \in$                                                                                                                        |

| 1.1         | $\mathbb{R}^{n \times n}, \overline{Q_i} \in \mathbb{R}^{n \times (k+1)}, Q_i \in \mathbb{R}^{n \times k} R_i \in \mathbb{R}^{k \times k}, q_i \in \mathbb{R}^{n \times 1}, n \gg k).  \dots  129$ |

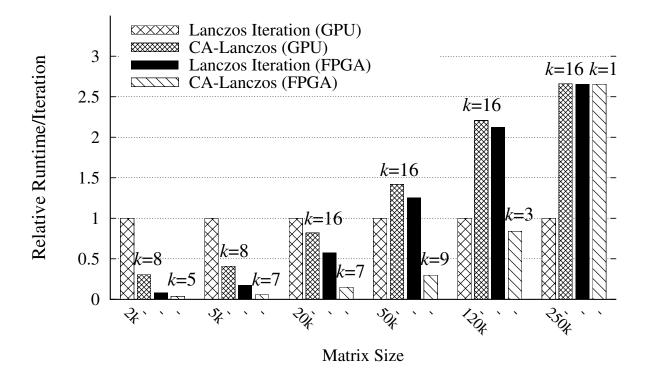

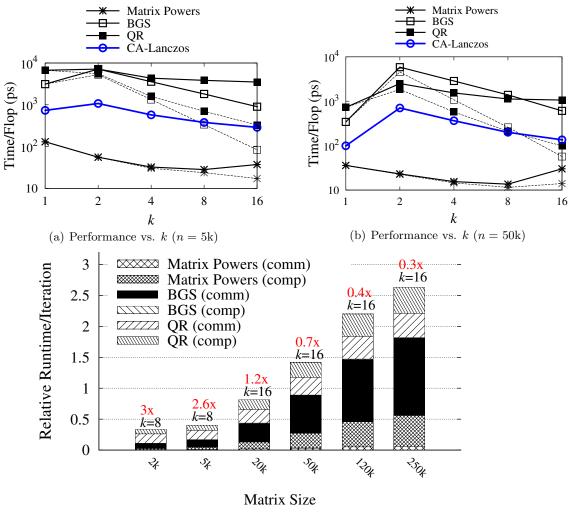

| 7.2         | Single-Precision performance comparison of Communication-Avoiding Lanczos                                                                                                                          |

| 1.2         | (CA-Lanczos) on GPU (Nvidia C2050 Fermi) and FPGA (Virtex6-SX475T) in                                                                                                                              |

|             | terms of time/iteration. The input matrices are banded with a band size $b = 27$ .                                                                                                                 |

|             | k is an algorithmic parameter whose optimal value is shown at the top of each                                                                                                                      |

|             | bar for CA-Lanczos                                                                                                                                                                                 |

|             |                                                                                                                                                                                                    |

| 7.3  | CA-Lanczos performance analysis on Nvidia C2050. In Figure 7.3(a) and 7.3(b),                                                                |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0  |                                                                                                                                              |

|      | we show how the algorithmic parameter $k$ is co-tuned for all the kernels. The                                                               |

|      | speedup over the Lanczos Iteration $(k = 1)$ is shown at the top of the bar in                                                               |

|      | Figure 7.3(c) for a range of matrices with band size $b = 27$ . The dashed lines in                                                          |

|      | Figure 7.3(a) and 7.3(b) represent the cost for doing useful operations only 135                                                             |

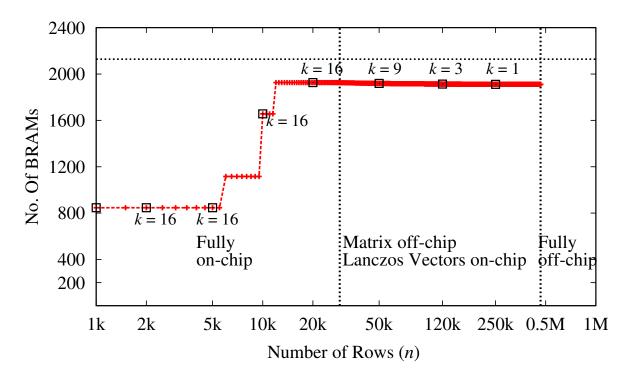

| 7.4  | Three distinct scenarios for CA-Lanczos on Virtex<br>6-SX475T (2128 18Kb BRAMs) $$                                                           |

|      | for problems with band size $b = 27$ . The maximum possible value of k is shown                                                              |

|      | for some matrix sizes. $\ldots \ldots 136$ |

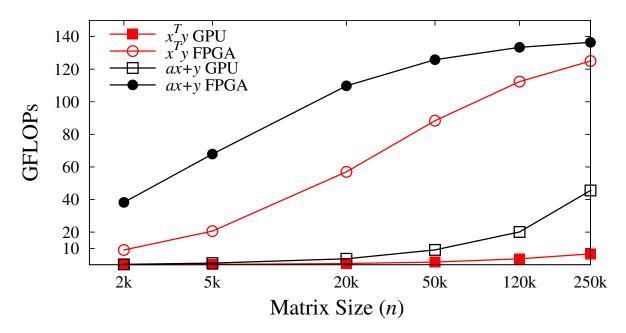

| 7.5  | $x^T y$ and $ax + y$ on GPU and FPGA                                                                                                         |

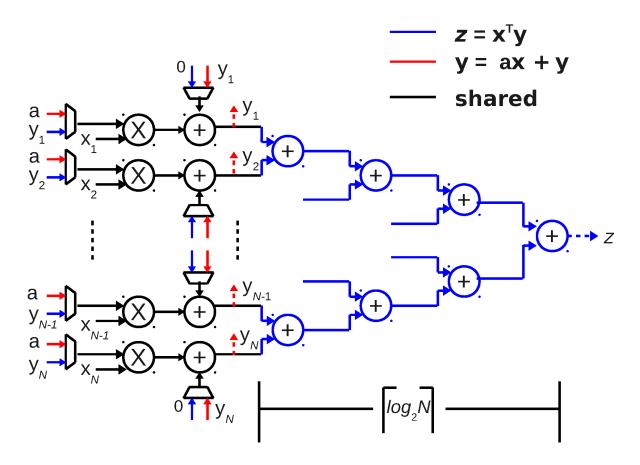

| 7.6  | A BLAS Circuit for $z \leftarrow x^T y$ and $y \leftarrow ax + y$ where $x, y \in \mathbb{R}^N$ . The dotted arrow                           |

|      | links show outputs                                                                                                                           |

| 7.7  | A time-multiplexed architecture for CA-Lanczos. The dotted lines show vector                                                                 |

|      | links of length $b$ whereas solid line represents scalars                                                                                    |

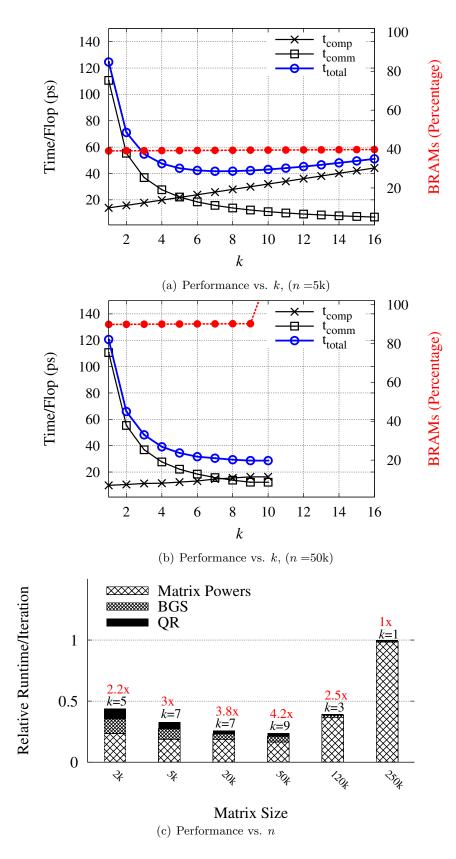

| 7.8  | CA-Lanczos performance analysis on FPGA. The value of $k$ is selected using the                                                              |

|      | resource-constrained framework in Figure 7.8(a) and Figure 7.8(b). The speedup                                                               |

|      | over the Lanczos method $(k = 1)$ on FPGA is shown in Figure 7.8(c) for a range                                                              |

|      | of matrices with the band size $b = 27$                                                                                                      |

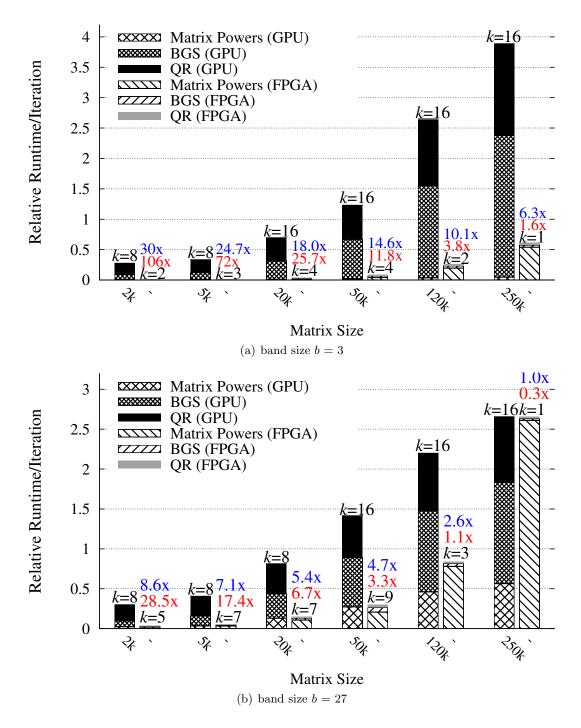

| 7.9  | Performance Comparison of CA-Lanczos on GPU (left bar) and FPGA (right                                                                       |

|      | bar). The optimal value of $k$ is shown at the top of the bars. The speedup factor                                                           |

|      | of FPGAs over GPU is also shown in red for standard Lanczos method on GPU                                                                    |

|      | and in blue for CA-Lanczos on GPU                                                                                                            |

| 7.10 | Silicon efficiency of FPGA and GPU for iterative numerical algorithms 146                                                                    |

# List of Tables

| 1.1 | Silicon Efficiency of FPGA and GPU for Iterative Numerical Algorithms (FPGA clock frequency is not reported in [87])                    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

| 3.1 | Architectural Features of FPGA and GPU (FPGA clock frequency is not reported in [87])                                                   |

| 4.1 | Experimental Setup (FPGA clock frequency is not reported in [87] for peak single-                                                       |

|     | precision GFLOPs)                                                                                                                       |

| 4.2 | Benchmarks                                                                                                                              |

| 4.3 | Comparison of FPGA-based Symmetric Eigenvalues Computation 81                                                                           |

| 5.1 | Single-Precision Parallel Matrix Powers Kernel Parallel Mapping on C2050 GPU                                                            |

|     | (n = 1M, b = 9, k = 8)                                                                                                                  |

| 5.2 | Model Parameters for GPU Performance                                                                                                    |

| 5.3 | GPU Analytical Model for Single-Precision Matrix Powers Performance 94                                                                  |

| 5.4 | Hybrid Matrix Powers Kernel Mapping on Virtex<br>6-SX475T FPGA ( $n$ =1M, $b$ =9,                                                       |

|     | $k = 10). \qquad \dots \qquad $ |

| 5.5 | Model Parameters for FPGA                                                                                                               |

| 5.6 | FPGA Analytical Model for Single-Precision Matrix Powers Performance 101                                                                |

| 5.7 | Matrix powers kernel performance comparison (Range is for $n = 2k - 1M$ ) 106                                                           |

| 6.1 | Comparison of QR Factorization (double-precision).                                                                                      |

|     | (Square: 6400×6400, Tall-Skinny (TS): 6400×51, FPGA clock frequency is 315                                                              |

|     | MHz for our design whereas clock frequency used for peak GFLOPs is not re-                                                              |

|     | ported in [87])                                                                                                                         |

| 6.2 | Householder QR floating-point units.                                                                                                    |

| 6.3 | Experimental Setup (FPGA clock frequency used for peak GFLOPs is not re-                                                                |

|     | ported in $[87]$ )                                                                                                                      |

| 6.4 | Type of Memory and its peak bandwidth for GPU and proposed FPGA design                                                                  |

|     | in different stages of TSQR                                                                                                             |

| 6.5 | Limiting Factors for Tall-Skinny Matrices (6400 $\times$ 51) on GPU. A warp comprises                                                   |

|     | 32 threads and there are 48 active warps per cycle for an occupancy of 1. $\dots$ 125                                                   |

| 7.1 | Basic Linear Algebra Blocks for CA-Lanczos                                                                                              |

| 7.2 | Floating-Point Units for CA-Lanczos.                                                                                                    |

| 7.3 | CA-Lanczos FPGA Analytical Performance Model                                                                                            |

| 7.4 | FPGA Resource Utilization (Estimated)                                                                                                   |

### List of Acronyms

**GPU** Graphical Processing Unit **FPGA** Field Programmable Gate Array **BLAS** Basic Linear Algebra Sub-Routine **MINRES** Minimum Residual Method **GMRES** Generalized Minimum Residual Method **CG** Conjugate Gradient **SVD** Singular Value Decomposition **SIMD** Single Instruction Multiple Data **SIMT** Single Instruction Multiple Threads **SM** Symmetric Multiprocessor **SDP** Semi-definite Programming **GFLOPs** Giga Floating-Point Operations Per Second **CSR** Compressed Sparse Row **CSC** Compressed Sparse Column **CDS** Compressed Diagonal Storage **SpMV** Sparse Matrix-Vector Multiply **SpMM** Sparse Matrix-Multiple Vector Multiply **PDE** Partial Differential Equation **ODE** Ordinary Differential Equation **ED** Energy Detection **MED** Maximum Eigenvalue Detection **DRAM** Dynamic Random Access Memory **NUMA** Non-uniform Random Access Memory **CA** Communication-Avoiding MGS Modified Gram-Schmidt LAPACK Linear Algebra Package

TSQR Tall-Skinny QR

$\textbf{BGS} \ Block \ Gram-Schmidt$

**IPC** Instructions Per Cycle

**MKL** Math Kernel Library

**CUBLAS** CUDA Basic Linear Algebra Subroutine

**ACML** AMD Core Math Library

$\boldsymbol{\mathsf{DAG}}$  Directed Acyclic Graph

$\ensuremath{\mathsf{ILP}}$  Instruction Level Parallelism

LUT Look Up Table

**FF** Flip Flop

- $\ensuremath{\mathsf{DSP}}$ Digital Signal Processor

- $\textbf{CLB} \ Configurable \ Logic \ Block$

- ${\boldsymbol{\mathsf{BW}}}$ Bandwidth

- **FP** Floating-Point

- I/O Input Output

- **BRAM** Block Random Access Memory

- **PE** Processing Element

- $\ensuremath{\mathsf{FIFO}}$  First In First Out

- $\ensuremath{\mathsf{MCMC}}$  Monte Carlo Markov Chain

## Nomenclature

- $\alpha$  memory or network latency

- $\alpha_g$  latency of global memory (in cycles)

- $\alpha_{sh}$  latency of shared memory (in cycles)

- $\alpha_{sync}$  latency of synchronization between threads (in cycles)

- $\beta$  inverse memory or network bandwidth

- $\beta_q$  inverse global memory bandwidth (in cycles)

- $\beta_{sh}$  inverse shared memory bandwidth (in cycles)

- $\gamma$  time per floating-point operation

- $\gamma_A$  latency of floating-point adder (in cycles)

- $\gamma_M$  latency of floating-point multiplier (in cycles)

- $\lambda_i$  ith eigenvalue

- $\lambda_{max}$  maximum eigenvalue

- $\lambda_{min}$  minimum eigenvalue

- $A \succeq 0\,$  positive semi-definite, i.e minimum eigenvalue is greater than equal to zero

- A upper case matrix

- $A^T$  transpose of a matrix A

- $A_{ij}$  the element of the matrix A at row i and column j

b band size

- $b_R$  number of rows in each partition while partitioning the input matrix A

- $I_n$  an identity matrix of size  $n \times n$

- k algorithmic parameter to trade communication with computation in communicationavoiding iterative algorithms

- L total latency of the matrix powers kernel (in cycles)

- $L_q$  latency of a single thread block in matrix powers kernel (in cycles)

$l_{compute}$  compute latency per thread block (in cycles)

$l_{condition}$  latency for evaluating conditional statements per thread block (in cycles)

$lA_{glb2reg}$  latency per thread block in data transfer, global memory —> register file (in cycles)  $lx_{glb2sh}$  data transfer latency per thread block, shared memory —> register file (in cycles)  $lx_{reg2glb}$  data transfer latency per thread block, register file —> global memory (in cycles)  $lx_{reg2sh}$  data transfer latency per thread block, register file —> shared memory (in cycles)

- m number of rows

- n number of columns

- $N_q$  number of partitions

$N_T$  number of threads

$N_{tiles}$  number of sub-matrices in tall-skinny QR factorization

*nnz* number of non-zero elements in a sparse matrix

*P* number of problems

- *p* block size in Block Krylov methods

- $P_e$  total number of processing elements

- Q a square  $n \times n$  orthogonal matrix *i.e.*  $Q^T Q = I_n$

- q partition number

- $Q_r$  a tall-skinny orthogonal matrix of size  $m \times r$  *i.e.*  $Q_r^T Q_r = I_r$

- R upper triangular matrix

r number of iterations

- t cost per iteration (in seconds)

- $T_r$  a tri-diagonal matrix of size  $r \times r$

- $t_r$  cost for r iteration (in seconds)

- $t_{comm}$  communication cost (in seconds)

$t_{comp}$  computation cost (in seconds)

$v_i$  householder reflector

x lower case – vector

$x_{i}^{i}$  jth element of vector  $x^{i}$

$G_{measured}$  measured performance (in GFLOPs)  $G_{modelled}$  modelled performance (in GFLOPs)  $t_{measured}$  measured time (in cycles or seconds)  $t_{modelled}$  modelled time (in cycles or seconds)

## 1 Introduction

The main motivation of this thesis is to answer the question: how to optimize communication in iterative numerical algorithms in order to improve silicon efficiency of common hardware accelerators like Field Programmable Gate Arrays (FPGAs) and Graphics Processing Unit (GPU)? The cost of a numerical algorithm comprises two factors (1) the *computation* cost of performing floating-point operations and (2) the *communication* cost of moving data within the memory hierarchy in the sequential case and or between processors in the parallel case. The communication cost includes both latency and bandwidth. Usually the communication cost is much higher than the computation cost, and there is a wide gap between these costs, e.g. the DRAM latency and bandwidth is improving by 5.5% and 23% respectively whereas the cost per floating-point operation decreases by 59% per year [41]. Iterative numerical algorithms belong to the class of communication-intensive algorithms and are widely used to solve large-scale sparse linear systems of equations Ax = b and eigenvalue problems  $Ax = \lambda x$  [33]. These algorithms are challenging to accelerate as they spend most of the time in communication-bound computations, like sparse matrix-vector multiply (SpMV) and vector-vector operations (dot products and vector additions). Additionally, the data dependencies between these operations hinder overlaping communication with computation. No matter how much parallelism can be exploited to accelerate SpMV, the performance of the iterative numerical algorithms is bounded by the available off-chip memory bandwidth, e.g. with 2 flops per 4 bytes (single-precision) in SpMV, the maximum theoretical performance is 71 GFLOPs on an Nvidia C2050 GPU and 17 GFLOPs on a Virtex6 FPGA. This results in less than 7% and 4% efficiency of GPU and FPGA respectively as shown in Table 1.1.

| clock frequency is not reported in [87]). |       |                    |              |                    |

|-------------------------------------------|-------|--------------------|--------------|--------------------|

| Device                                    | Tech. | Peak GFLOPs        | Memory BW    | Silicon Efficiency |

|                                           | (nm)  | (single-precision) | (Off-Chip)   | (Upper bound)      |

| <b>Virtex6</b><br>(SX475T)                | 40    | 450 [87]           | 34 GB/s [87] | 4%                 |

| Nvidia C2050                              | 40    | 1030               | 144  GB/s    | 7%                 |

| (Fermi)                                   |       |                    |              |                    |

Table 1.1: Silicon Efficiency of FPGA and GPU for Iterative Numerical Algorithms (FPGA clock frequency is not reported in [87]).

FPGAs have long been used as an alternative to microprocessors for computing tasks which do not involve floating-point computation [79] [13] [45]. With increasing silicon densities due to Moore's Law, FPGAs have seen much high peak floating-point performance. Similarly, GPUs have recently been used as another hardware accelerator in high performance scientific computing delivering a higher peak floating-point performance compared to FPGAs as shown in Table 1.1. Many important applications from science and engineering spend time solving linear systems of equations or eigenvalue problems, therefore, the question is how much of peak floating-point performance of GPU and FPGAs can be sustained while accelerating the iterative numerical algorithms?

Before discussing different approaches to improve efficiency of these hardware accelerators, we describe runtime of a single iteration of the numerical algorithm in terms of communication and computation costs by Equation (1.1)

$$t_{comm} = \#msg \times \alpha + msize \times \beta.$$

$$t_{comp} = flops \times \gamma.$$

$$t = t_{comm} + t_{comp}.$$

(1.1)

We consider communication happens in the form of messages, which can be words from slow memory to fast memory or between different processors. Overall runtime is the sum of three factors, memory latency ( $\alpha$ ), inverse memory bandwidth ( $\beta$ ) and time per flop ( $\gamma$ ). For r iterations of the iterative numerical algorithm, SpMV is launched r times to build a representation of the Krylov subspace span( $x, Ax, A^2x, ..., A^rx$ ) [34]. The total cost for r iterations is then given by

$$t_r = r \times t_{comm} + r \times t_{comp}. \tag{1.2}$$

Due to technology scaling, computational performance is increasing at a dramatic rate (flops/sec improves by 59% each year) whereas communication performance is also improving but at a much lower rate (DRAM latency improves by 5.5% and bandwidth improves by 23% each year) [41]. To minimize communication cost, knowing that the matrix A stays constant, an obvious approach is to store the matrix in the on-chip memory [31] [61] and then reuse it for r iterations. The communication cost is effectively reduced by a factor of r as shown in Equation (1.3).

$$t'_r = t_{comm} + r \times t_{comp}. \tag{1.3}$$

However, for large matrices which do not fit on-chip, the matrix needs to be moved r times within the memory hierarchy making it both a latency-bound as well as bandwidth-bound problem [65]. In order to bridge the gap between computation and communication performance, the communication-avoiding iterative solver [48] is recently proposed, which is an algorithmic approach to trade communication with redundant computation. As the same matrix is used over and over to generate a new vector in each iteration, the SpMV kernel is replaced with a *matrix powers kernel* which unrolls k iterations to generate k vectors in a single sweep. The key idea is to partition the matrix into blocks and performs k SpMVs on blocks without fetching the block again in the sequential case and performing redundant computation to avoid communication with other processors in the parallel case [48]. As a result, for a given accuracy, the number of iterations is reduced by k. This reduces the communication cost by k but at the expense of f(k) growth in redundant computation.

$$t_r'' = \frac{r}{k} \times t_{comm} + r \times t_{comp} + \frac{r}{k} \times f(k).$$

(1.4)

The maximum value of k to which we can unroll depends on the underlying architecture, its memory model and computation to communication ratio for a given problem. Therefore, we need to pick this parameter k carefully for different architectures as well as varying problem sizes. Besides replacing k SpMVs with the matrix powers kernel, the vector-vector operations in a standard iterative solver are also replaced with new kernels like Block Gram-Schmidt Orthogonalization Orthogonalization (BGS) and QR factorization [48]. The addition of these kernels not only introduces extra computation but also poses a composition challenge involving more communication cost while sharing data across these kernels. There are three main challenges associated with this communication-avoiding approach on parallel architectures

- how to keep the redundant computation as low as possible in each kernel to minimize the computation cost?

- how to compose different kernels to minimize the communication cost in sharing data across these kernels?

- how to select the optimal value of the algorithmic parameter k which minimizes overall runtime by providing a tradeoff between computation and communication cost?

In this thesis, we attempt to address these challenges in a systematic way to minimize communication cost and thereby increasing the silicon efficiency of FPGAs in accelerating iterative numerical algorithms. To this end, we present an algorithm for the matrix powers kernel that matches with the strengths of the FPGA to avoid redundant computation. We make use of the large on-chip memory of the FPGAs to share data across different kernels and highlight that such sharing is not possible using the present GPU architecture. In order to trade communication with computation, we provide a resource-constrained methodology to select the algorithmic parameter k. The end result is a recipe to generate custom hardware by picking the algorithmic parameter k in an automatic fashion to minimize overall cost and thereby increase silicon efficiency. We compare our results with GPU and show that for a range of problem sizes, the FPGA outperforms the GPU.

### 1.1 Case Study: Lanczos Iteration for Solving Symmetric Extremal Eigenvalue Problem

The choice of iterative numerical algorithm depends on the characteristics of the matrix A, e.g. for solving Ax = b, the Conjugate Gradient [39] is used if A is positive definite, often the Minimum Residual Method (MINRES) is used for indefinite but symmetric matrices. A recipe is given in [16] and [12] to choose the particular algorithm for solving linear system of equations and eigenvalue problem respectively. However, at the heart of each iterative numerical algorithm is a Lanczos Iteration [39] and the results obtained for the Lanczos Iteration are generally applicable to all iterative numerical algorithms. We use Lanczos Iteration to solve symmetric

extremal eigenvalue problem, *i.e.* finding only the maximum and minimum eigenvalue of the symmetric matrix A. In various applications including semidefinite optimization programs [94] and eigen-based channel sensing [104], we need to solve multiple of these problems and therefore it is highly desirable to accelerate these iterative numerical algorithms.

### 1.2 Thesis Organization

Chapter 2 introduces the reader to the four main problems in applied numerical linear algebra including solution to the linear systems of equation and eigenvalue problem. It discusses different structures involved in these problems. Chapter 2 also classifies the numerical methods as direct and iterative methods, which are used to solve dense and sparse problems respectively. Iterative numerical algorithms are discussed in general and the Lanczos Iteration in particular. The chapter also highlights the communication-bound kernels in the Lanczos Iteration. It then discusses different approaches used for accelerating communication-bound kernels and highlights the limitations in terms of increased communication cost particularly for large-scale problems. Finally, it talks about the communication-avoiding variant of the Lanczos Iteration, the Communication-Avoiding Lanczos, its building blocks and the challenges it poses for algorithm designers as well as hardware architects. We also introduce structurally sparse banded matrices which are of great interest both for their applications and their use as benchmark for architecture evaluation.

Chapter 3 discusses various computing platforms including multi-cores, many-cores (GPUs, Intel Xeon Phi Co-processor) and custom computing architectures like FPGAs. We compare their architectural features including peak floating-point performance, on-chip memory bandwidth, on-chip memory capacity and off-chip memory bandwidth. We finally highlight the low silicon efficiency of these architectures in accelerating the communication-bound iterative numerical algorithms.

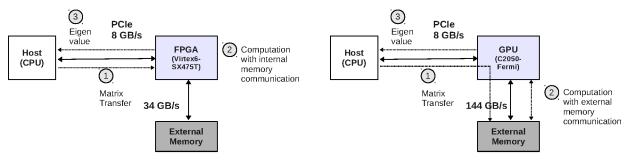

Chapter 4 talks about hardware acceleration of Lanczos Iteration working on small-to-medium size data sets. We use explicit cache-blocking to minimize communication cost as shown in Equation (1.3). We design a single-precision hardware architecture for the Lanczos Iteration similar to [61] to minimize computation cost and thereby reduce overall runtime. We show how we can increase the silicon efficiency by exploiting pipeline parallelism and solving multiple independent symmetric extremal eigenvalue problems. We finally compare the results with GPU and show that FPGAs have better silicon efficiency due to explicit cache-blocking and pipeline parallelism. The problem setting for Chapter 4 is shown in Figure 1.1. In case of the FPGAs, we assume that the matrices are transferred from host memory to the internal memory of the FPGA, where they are blocked and are reused for all iterations. For GPUs, due to small on-chip memory, the matrices are transferred from host memory to the external memory, from where they are fetched in each Lanczos iteration. At the end, the eigenvalue is transferred back to the host.

Chapter 4 talks about hardware acceleration of Lanczos Iteration working on small-to-medium size data sets. We use explicit cache-blocking to minimize communication cost as shown in Equa-

tion (1.3). We design a single-precision hardware architecture for the Lanczos Iteration similar to [61] to minimize computation cost and thereby reduce overall runtime. We show how we can increase the silicon efficiency by exploiting pipeline parallelism and solving multiple independent symmetric extremal eigenvalue problems. We finally compare the results with GPU and show that FPGAs have better silicon efficiency due to explicit cache-blocking and pipeline parallelism. The problem setting for Chapter 4 is shown in Figure 1.1. In case of the FPGAs, we assume that the matrices are transferred from host memory to the internal memory of the FPGA, where they are blocked and are reused for all iterations. For GPUs, due to small on-chip memory, the matrices are transferred from host memory to the external memory, from where they are fetched in each Lanczos iteration. At the end, the eigenvalue is transferred back to the host.

(a) FPGA Problem Setting

(b) GPU Problem Setting

Figure 1.1: FPGA and GPU problem setting for solving small-to-medium scale problems. Step is not actually performed for both architectures

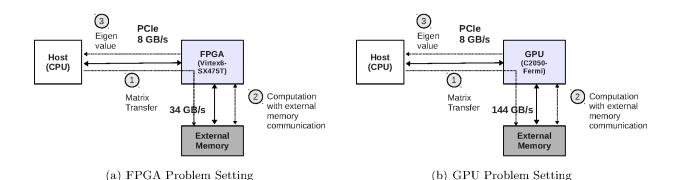

Chapter 5 is where we talk about accelerating the Lanczos Iteration for solving the largescale symmetric extremal eigenvalue problem. We specifically discuss the matrix powers kernel, a fundamental block of Communication-Avoiding Lanczos, which performs k SpMVs at the communication cost of single SpMV. We show how such an approach can minimize overall runtime on both GPUs and FPGAs by trading communication with redundant computation as shown in Equation (1.4). We present an algorithm for the matrix powers kernel that matches with the strengths of FPGAs to avoid redundant computation. We show how we can increase silicon efficiency of FPGAs and GPUs by carefully selecting the algorithmic parameter k. We also introduce our predictive model which shows how this algorithmic approach can increase efficiency which otherwise requires significant increase in memory bandwidth and latency. The problem setting for Chapter 5 and future chapters is shown in Figure 1.2. Both for FPGA and GPU, the matrices are first transferred to the external memory where they are partitioned in blocks. These blocks are then fetched to perform k iterations of the Communication-Avoiding Lanczos. The final eigenvalue is then transferred back to the host.

Chapter 6 is where we introduce tall-skinny QR factorization (TSQR), another important kernel of Communication-Avoiding Lanczos. We show that the efficiency of the GPU is less than 1% for factorizing extremely tall and skinny matrices that not only arise in these iterative algorithms but many other real applications like stationary video background subtraction [8].

Figure 1.2: FPGA and GPU problem setting for solving large-scale problems. Step is not actually performed for both architectures

We observe that low efficiency is due to off-chip sharing of data across different kernels. We judiciously share data across these kernels using on-chip memory of the FPGAs and thereby eliminate off-chip communication which is unavoidable in case of GPU. We also introduce a custom architecture and show how we can increase silicon efficiency by exploiting pipeline parallelism to factorize multiple small matrices which arise in tall-skinny QR. We compare our results with state of the art QR routines on a GPU [8] and show the range of matrix sizes where FPGAs perform better than GPU.

Chapter 7 is where we compose all the kernels of Communication-Avoiding Lanczos and show how we can make use of architectural features of FPGAs to minimize communication in iterative solvers. We highlight GPU limitations in composition of kernels primarily due to off-chip sharing of data across these kernels. We show how the algorithmic parameter k needs to be co-tuned for all the kernels. We finally conclude that a tight interaction between algorithm and architecture is required to enhance the silicon efficiency of FPGAs in accelerating iterative numerical algorithms.

Chapter 8 concludes our work and also provides potential areas for further research.

### 1.3 Statement of Originality

The four main original contributions of this thesis are each contained within each separate chapter. We provide details in the introduction chapter of these papers, however, we briefly summarize them here:

- A high-throughput architecture to accelerate multiple symmetric extremal eigenvalue problems. We show how we can use explicit cache-blocking and pipeline parallelism to increase silicon efficiency of FPGAs. We also provide comparison with GPU and show significant performance improvements. (Chapter 4, [77])

- A matrix powers kernel specifically targeting FPGAs in order to avoid redundant computation. A predictive model of GPU and FPGA to show how a tight algorithm-architecture interaction is required to enhance performance which otherwise requires significant increase in off-chip memory bandwidth and latency. (Chapter 5, [75])

- A custom architecture for enhancing performance of tall-skinny QR factorization. We show how we can make use of on-chip memory of FPGA to share data across different blocks which is only possible through off-chip shared memory in case of GPUs.(Chapter 6, [76])

- Application composition and communication optimization in iterative solvers using FP-GAs.(Chapter 7, [78])

### 1.4 Publications

The following publications have been written during the course of this thesis:

- Abid Rafique, Nachiket Kapre, and George A. Constantinides, A high throughput FPGA-Based implementation of the Lanczos Method for the symmetric extremal eigenvalue problem. In Reconfigurable Computing: Architectures, Tools and Applications, pages 239–250. Springer, 2012.

- Abid Rafique, Nachiket Kapre, and George A. Constantinides, Enhancing performance of Tall-Skinny QR factorization using FPGAs. In Proceedings of the 22nd IEEE International Conference on Field Programmable Logic and Applications (FPL), pages 443–450, 2012.

- Abid Rafique, Nachiket Kapre, and George A. Constantinides, Application composition and communication optimization in iterative solvers using FPGAs. In Proceedings of the 21st IEEE International Conference on Field-Programmable Custom Computing Machines (FCCM), 2013.

- Abid Rafique, George A. Constantinides and Nachiket Kapre, Communication Optimization of Iterative Sparse Matrix-Vector Multiply on GPUs and FPGAs. accepted in IEEE Transactions on Parallel and Distributed Systems, 2014.

## 2 Applied Numerical Linear Algebra

In this chapter, we introduce basic problems of linear algebra. We introduce different matrix structures together with the numerical methods used to solve problems involving a particular structure. The scope of the thesis is also defined in this chapter. A major focus of this chapter is to identify communication as a basic problem in iterative numerical algorithms, which are used for solving sparse linear algebra problems. We discuss different approaches to minimize this communication on parallel and sequential architectures. Additionally, we also discuss related research questions that arise when these approaches are used for minimizing communication in iterative numerical algorithms on modern computing platforms like FPGA and GPU.

### 2.1 Standard Problems

There are four standard problems of numerical linear algebra, which often arise in engineering and scientific computations.

- Linear systems of equations: Given an  $n \times n$  non-singular matrix A and an  $n \times 1$  vector b, solve Ax = b to compute the  $n \times 1$  unknown vector x. This problem arises in all fields of science and engineering: biology, chemistry, applied mathematics, finance, mechanical, civil and electrical engineering, etc. The most common source is the numerical solution of differential equations which arise in mathematical models of many engineering and physical systems. The numerical methods for solving such equations involve discretization of the system by finite element or finite difference methods. This discretization process leads to a linear system Ax = b which is repeatedly solved to find an approximate solution to the differential equations. One such application is SPICE circuit simulation where Ax = b is solved repeatedly to find solution of non-linear differential equations. Here A is the matrix comprising conductances, b is the vector containing the known currents and voltage quantities and x contains the unknown branch currents and voltage quantities. Other application areas include mathematical optimization solvers [5], computational fluid dynamics [47] and finance [85].