UNIVERSITY OF LONDON

FACULTY OF ENGINEERING

High Speed Accurate Quantization of Voltage Signals.

A Thesis presented for

the Degree of Doctor of Philosophy

by

Réal Viateur L'Archevêque

Department of Electrical Engineering,

Imperial College of Science and Technology,

(City and Guilds College),

Exhibition Road,

London, S.W.7.

November 1964.

### ABSTRACT

A quantizer is described, the present prototype of which is capable of performing 6000 analogue-to-digital conversions per second with a precision of ±0.5% of full scale. The apparatus was built to investigate a new type of potentially adaptive circuit usable in the design of highly flexible laboratory equipment; it illustrates a principle by which a high speed self-adjusting voltage reference can follow the variations of an input signal within one quantization interval.

A detailed analysis is presented of problems arising in the use of tunnel diodes in long chains to generate accurately defined staircase waveforms intended to serve as a stepping reference in the quantizer. It is shown that as many as 2000 voltage levels could be defined in this way with a combination of six chains; a tolerance of ±11% on the driving pulse amplitude is acceptable for chains containing ten tunnel diodes, provided that the rise time of these pulses is longer than some 20 nanoseconds. The chains can be operated continuously at repetition rates up to ten million pulses per second. A complete voltage reference, using four chains and defining 200 levels, is shown to offer a high speed of operation and a very low thermal drift owing to a temperature compensation effect between the chains.

The switching action of a tunnel diode is described qualitatively and a relaxation oscillator is analysed using a linear approximation of the tunnel diode characteristic. From this analysis, a general method is developed for the design of various tunnel diode-transistor hybrid switching circuits; it gives a timing precision better than ±5% for operating frequencies up to about 20Mc/s. Application of the method to the design of one-tunnel diode flip flops, monopulsers, relaxation oscillators and an adjustable voltage level discriminator is illustrated.

It is maintained that the technique, which is applied successfully throughout the quantizer, provides a simple though powerful tool for the design of tunnel diode switching circuits. Complete specifications for the prototype of the quantizer built in the laboratory, are included and it is argued that the remarkable flexibility inherent in the technique employed should encourage further investigations along these lines in view of a possible extension to a new class of circuits with a significant degree of adaptability.

### ACKNOWLEDGMENTS

The author wishes to express his gratitude to his supervisor, Dr. B.McA. Sayers, for encouragement and advice during this work. Thanks are also due to H.D. Barber of the Materials Laboratory for helpful discussions on tunnel diodes and transistors.

The financial support provided by the Athlone Fellowships Managing Committee, the Government of the Province of Quebec, Canada, and the National Research Council of Canada, is gratefully acknowledged.

Finally, the author pays tribute to his wife for her help in typing the first draft of the thesis and for her patient support.

# INDEX

|                   |                             |                 | page |

|-------------------|-----------------------------|-----------------|------|

| Title             |                             | • • • •         | . 1  |

| Abstract          | • • • •                     | • • • •         | 2    |

| Acknowledgments   | • • • .•                    | ••••            | 4    |

| Introduction      | ••••                        | ••••            | 13   |

| CHAPTER 1. INTRO  | ODUCTION TO THE PUR         | POSE AND DESIGN |      |

| OF AI             | N ANALOGUE-TO-DIGIT         | AL CONVERTER    | 15   |

| 1.1. A Note on E  | lectronic Computers         | ••••            | 15   |

| 1.2. Needs for Ar | nal <b>og</b> ue-to-Digital | Converters      | 16   |

| 1.3. Survey of Li | iterature on A-D Co         | nverters        | 17   |

| 1.3.1. Class      | sification of Volta         | ge-to-Digital   |      |

| Conv              | verters                     | ••••            | 17   |

| 1.3.2. Gener      | ral Remarks                 | ••••            | 18   |

| 1.4. Proposed Ana | alogue-to-Digital C         | onverter        | 21   |

| 1.4.1. Speci      | fications                   | • • • •         | 21   |

| 1.4.2. Propo      | sed Solution                | • • • •         | 24   |

| 1.4.3. Compa      | arison with Delta Mo        | odulation       | 27   |

| 1.4.4. Basic      | Requirements for            | the Reference   |      |

| Unit              | <b>5.</b>                   | ••••            | 29   |

| PART I DESIGN OF  | THE HIGH SPEED STE          | PPING REFERENCE | 32   |

| CHAPTER 2. DESIG  | N OF A BUILDING BLO         | OCK             | 32   |

| 2.1. Preliminary  | Remarks                     | • • • •         | 32   |

| 2.2. The Tunnel D | iode                        | • • • •         | 33   |

|      |        |           |            |                     |                   |          | O          |

|------|--------|-----------|------------|---------------------|-------------------|----------|------------|

|      |        |           |            |                     |                   |          | page       |

|      | 2.2.1. | The Tunn  | el Diode a | as a Ci             | rcuit Elem        | ent      | 35         |

|      | 2.2.2. | Basic Ci  | rcuit      |                     | • • • •           |          | 41         |

| 2.3. | The Tu | nnel Diod | e Chain    |                     | • • • •           |          | 43         |

|      | 2.3.1. | Switchin  | g of a Sin | igle Tu             | nnel Diode        |          | 45         |

|      |        | 2.3.1.1.  | Current I  | rive                | • • • •           |          | 46         |

|      |        | 2.3.1.2.  | Voltage I  | rive                | • • • •           |          | 48         |

|      |        | 2.3.1.3.  | Practical  | Case                | • • • •           |          | 51.        |

|      | 2.3.2. | Switching | g of a Ser | ies of              | Two Tunne         | l Diodes | 54         |

|      |        | 2.3.2.1.  | Current D  | rive c              | f the Tunn        | el Diode |            |

|      |        |           | Pair       |                     | • • • •           |          | 55         |

|      |        | 2.3.2.2.  | Voltage D  | rive c              | f the Tunn        | el Diode |            |

|      |        |           | Pair       |                     | • • • •           |          | <i>5</i> 7 |

|      |        |           | 2.3.2.2.1  | . Diff              | erent Peak        | Currents |            |

|      |        |           | ,          | $I_{\mathfrak{pl}}$ | < I <sub>p2</sub> |          | 58         |

|      |        |           | 2.3.2.2.2  | . Iden              | tical Peak        | Currents |            |

|      |        |           |            | Ipl                 | $= I_{p2}$        | •        | 60         |

|      |        | 2.3.2.3.  | Practical  | Cases               | _                 |          | 62         |

|      |        |           | 2.3.2.3.1  | . Diff              | erent Peak        | Currents | 62         |

|      |        |           | 2.3.2.3.2  | . Equa              | l Peak Cur        | rents    | 65         |

|      | 2.3.3. | Switching | g of a Ser | ies of              | N Tunnel          | Diodes   | 67         |

|      | 2.3.4. | Static Ch | naracteris | tic of              | the Chain         |          | 67         |

|      |        | 2.3.4.1.  | Lower Lim  | it of               | Trigger Pu        | Lse      |            |

|      |        |           | Amplitud   | e                   | • • • •           |          | 73         |

|      | •      | 2.3.4.2.  | Upper Lim  | it of               | Trigger Pu        | Lse      |            |

|      |        |           | Amplitud   | е                   |                   |          | 74         |

|      | 2.3.5. | The Stair | case Wave: | form                | • • • •           |          | 80         |

|      | 2.3.6. | Precision | of the S   | teps i              | n the Chair       | ı        | 81         |

|      |                                              | 7    |

|------|----------------------------------------------|------|

|      |                                              | page |

| 2.4. | Methods of Resetting                         | 86   |

|      | 2.4.1. Direct Transistor Switching           | 87   |

|      | 2.4.1.1. Resetting Action                    | 87   |

|      | 2.4.1.2. Disadvantages of Direct Transis-    |      |

|      | tor Switching Technique                      | 90   |

|      | 2.4.2. Use of Intermediate Switching         | 92   |

| 2.5. | The Astable Oscillator                       | 93   |

|      | 2.5.1. Loading of the Tunnel by a Transistor | 101  |

|      | 2.5.2. Computation of the Switching Times    | 106  |

| 2.6. | The Monopulser                               | 107  |

|      | 2.6.1. Design Equation for the Tunnel Diode  |      |

|      | Monopulser                                   | 112  |

|      | 2.6.2. Design Procedure for Monopulser       | 113  |

|      | 2.6.3. Practical Design of a Monopulser      | 114  |

| 2.7. | Design of Output State                       | 119  |

|      | 2.7.1. Transient Response of the Output      |      |

|      | Transistor                                   | 123  |

|      | 2.7.2. Output Pulse Width                    | 125  |

| CHAP | TER 3. THE COMPLETE STAIRCASE GENERATOR      | 128  |

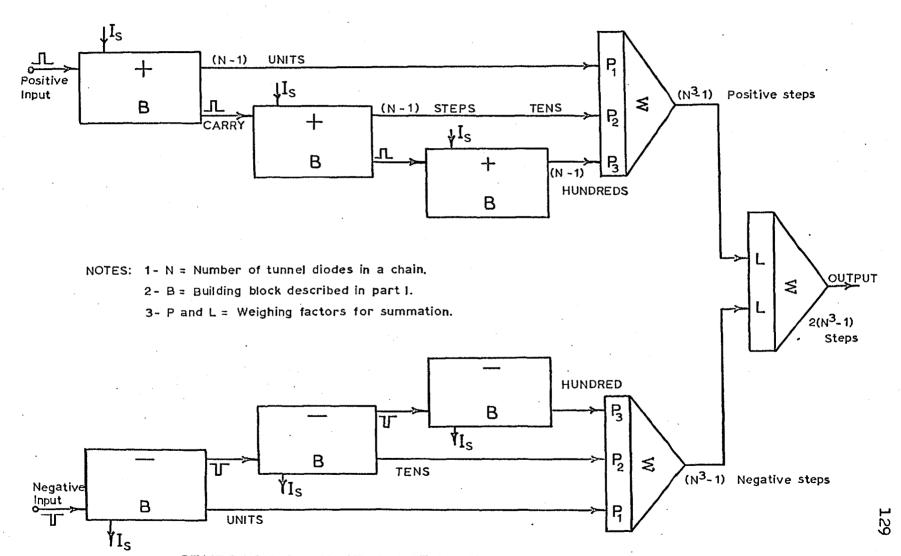

| 3.1. | Basic System                                 | 128  |

| 3.2. | Precision of the Decades                     | 131  |

| 3.3. | Thermal Drift                                | 132  |

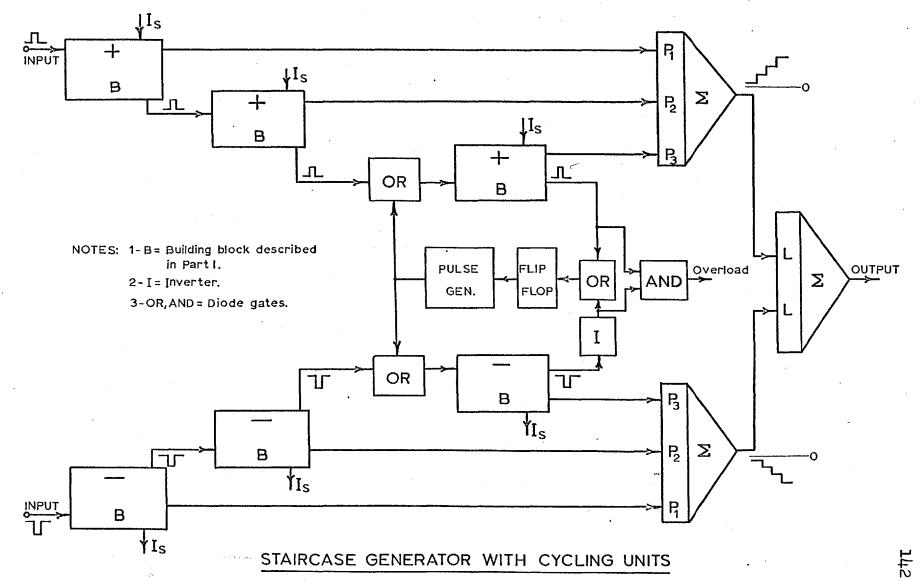

| 3.4. | High Speed Cycling Process                   | 141  |

|      | 3.4.1. Influence of the Cycling Process on   |      |

|      | the Speed of Operation                       | 7 44 |

|       |         |                           |                   | page |

|-------|---------|---------------------------|-------------------|------|

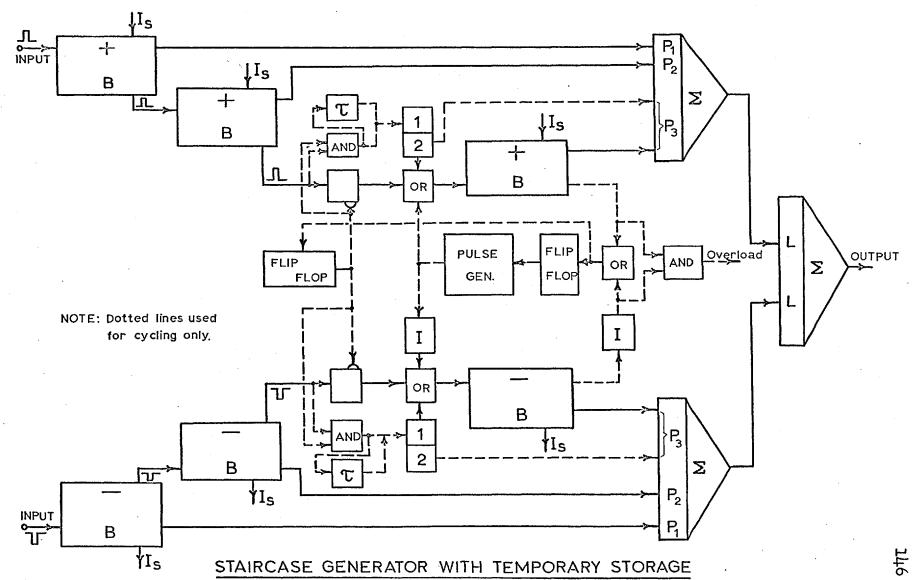

|       | 3.4.2.  | Temporary Storage         | • • • •           | 145  |

| 3.5.  | Design  | of Control Circuits       | ••••              | 147  |

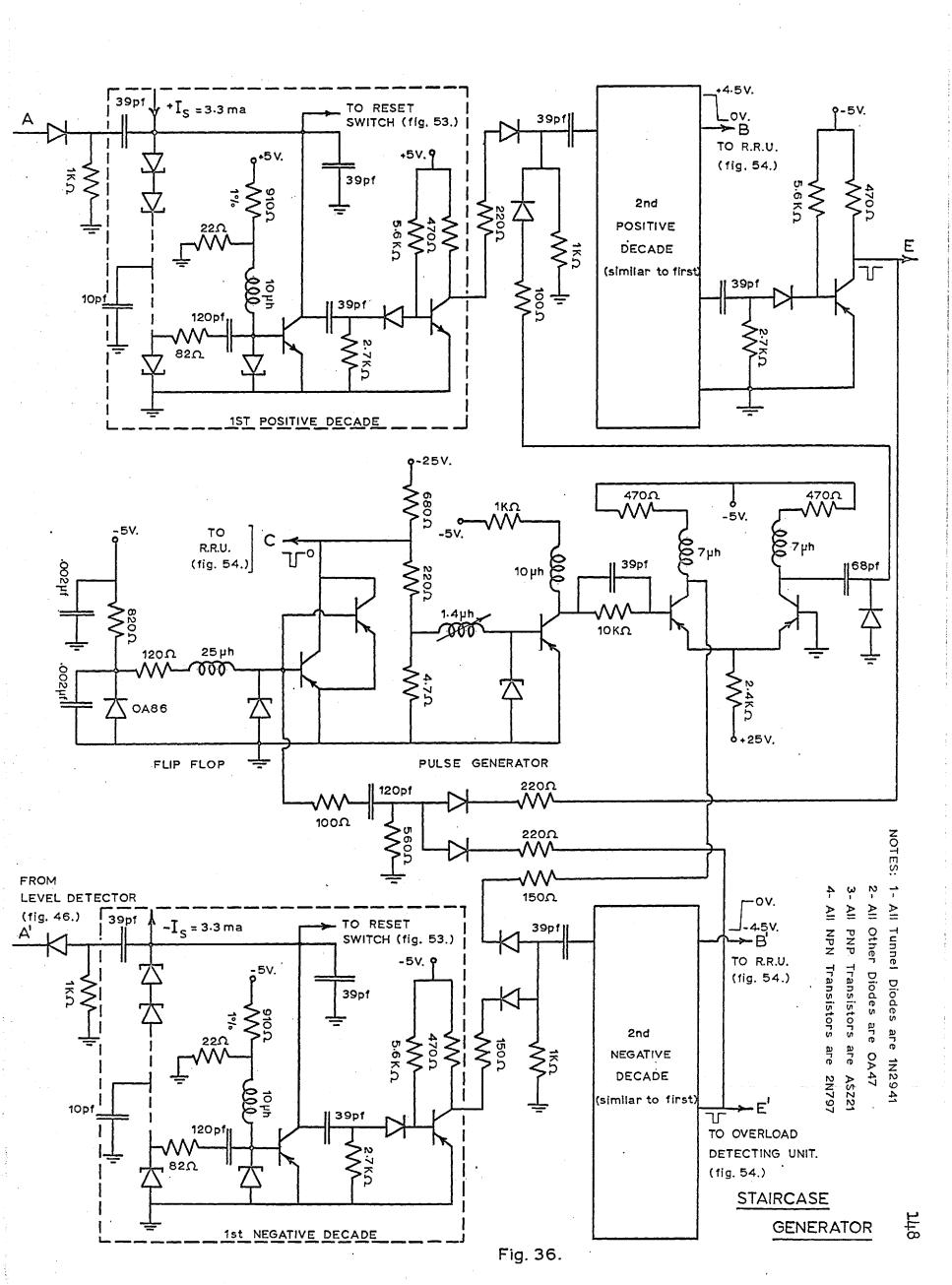

|       | 3.5.1.  | Pulse Generator           | ••••              | 147  |

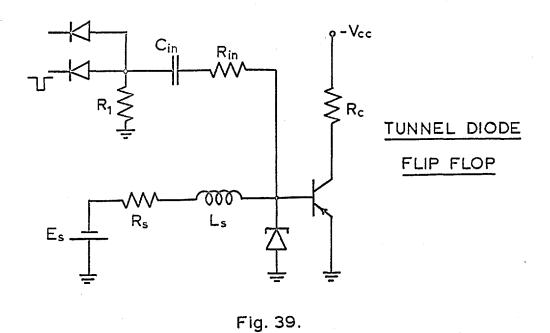

|       | 3.5.2.  | One-Tunnel Diode Flip Fl  | op                | 153  |

|       |         | 3.5.2.1. Analysis of the  | One-Tunnel        |      |

|       |         | Diode Flip Flo            | p                 | 156  |

|       |         | 3.5.2.2. Design of the O  | ne-Tunnel         |      |

|       |         | Diode Flip Flo            | p                 | 157  |

|       |         | 3.5.2.3. Summary of the   | Design Procedure  | 162  |

|       |         | 3.5.2.4. Practical Desig  | n and Performance | 163  |

|       |         |                           |                   |      |

| PART  | II      | THE QUANTIZER             |                   | 170  |

| CHAP! | TER 4.  | DESIGN OF AUXILIARY CIRC  | UITS              | 170  |

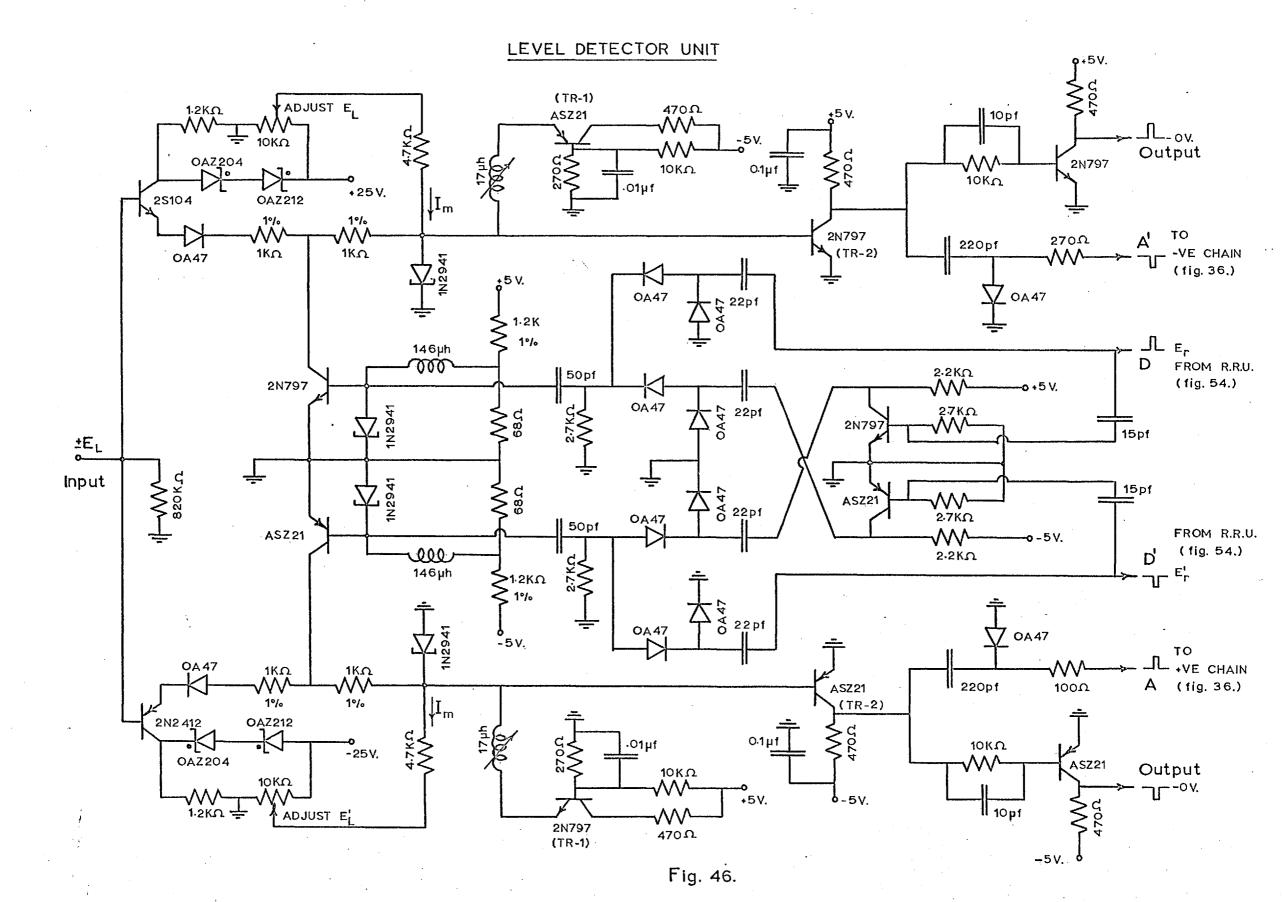

| 4.1.  | Level 1 | Detector                  | ••••              | 175  |

|       | 4.1.1.  | Basic Circuit of Level D  | etector           | 175  |

|       | 4.1.2.  | Related Problems          | ••••              | 180  |

|       | 4.1.3.  | Temperature Coefficient   | ••••              | 181  |

|       | 4.1.4.  | Performance               | • • • •           | 183  |

|       | 4.1.5.  | The Level Detector Gate   | • • • •           | 185  |

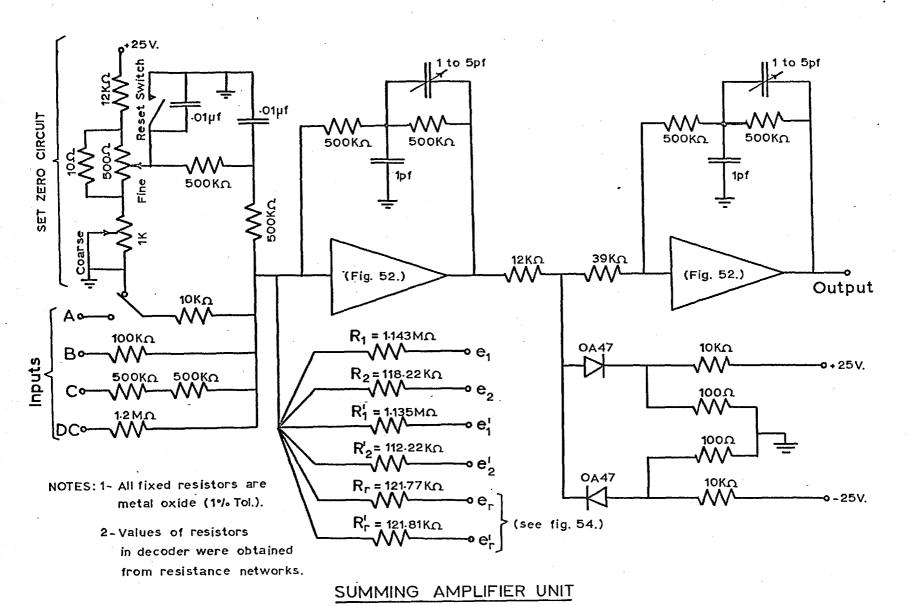

| 4.2.  | Summing | g Amplifier               | ••••              | 188  |

|       | 4.2.1.  | Performance               | • • • •           | 192  |

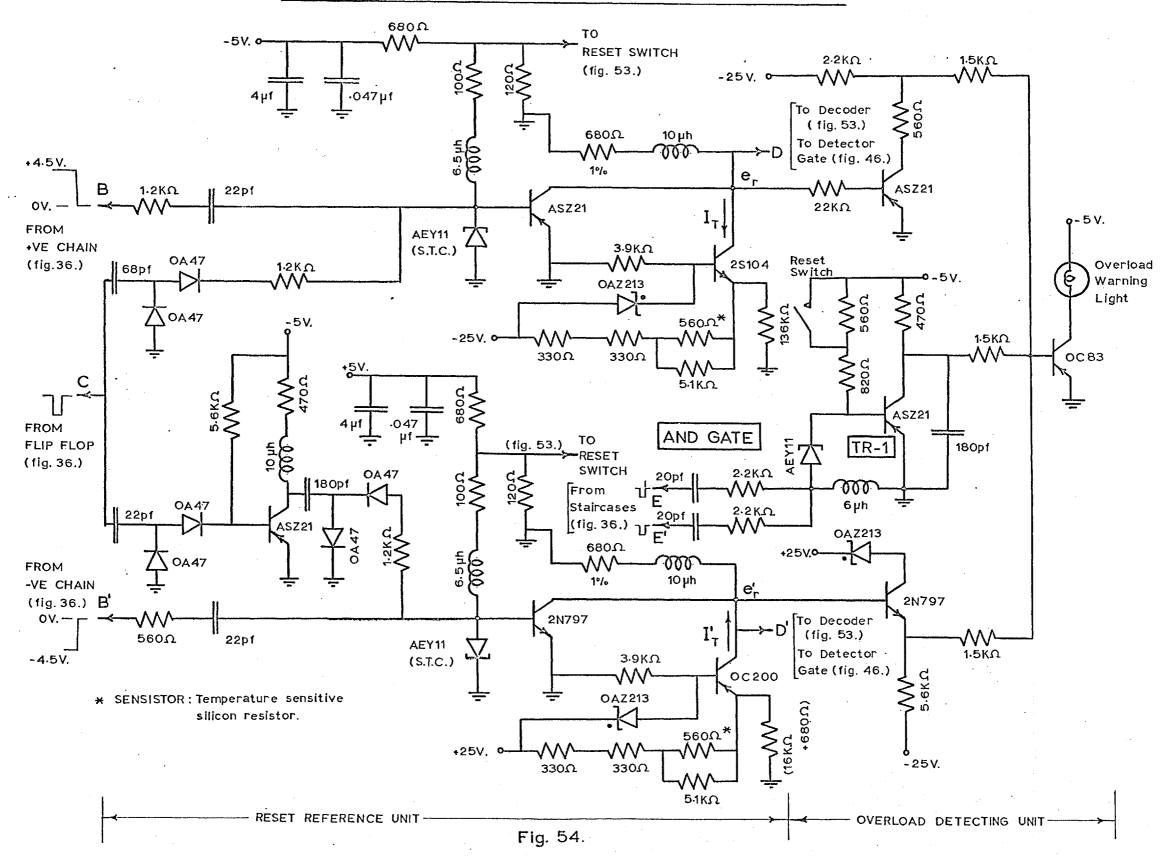

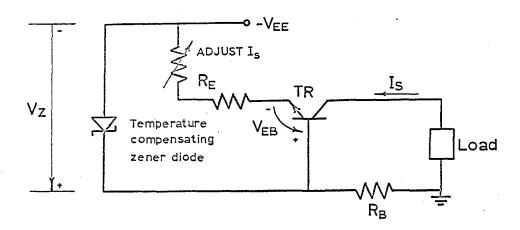

| 4.3.  | Reset F | Reference Unit            | ••••              | 194  |

| 4.4.  | Overloa | ad Detection Unit         | • • • •           | 197  |

| 15    | Lineari | ty of Staircase Generator | r                 | 199  |

|                                                 | 9<br>page |

|-------------------------------------------------|-----------|

| CHAPTER 5. PERFORMANCE OF THE PROTOTYPE AND     |           |

| DISCUSSION OF THE RESULTS                       | 202       |

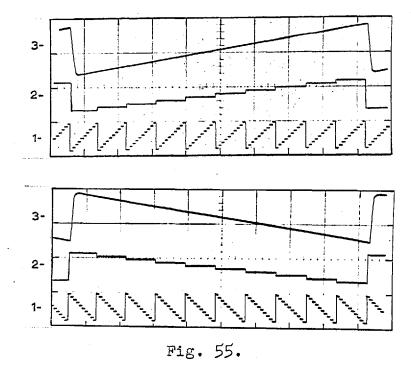

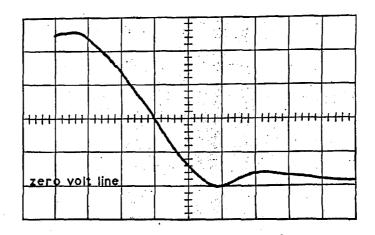

| 5.1. Very Low Frequency Test                    | 206       |

| 5.2. Dynamic Tests                              | 211       |

| 5.2.1. Step Response                            | 21.4      |

| 5.2.2. Frequency Response                       | 21.8      |

| 5.3. Applications                               | 221       |

| 5.4. Conclusion                                 | 226       |

| APPENDIX                                        |           |

| A.l. The Tunnel Diode Characteristic            | 230       |

| A.1.1. Linear Approximation of the Tunnel Di    | ođe       |

| Characteristic                                  | 230       |

| A.2. The Tunnel Diode Relaxation Oscillator     | 232       |

| A.2.1. Linear Approximation of the Tunnel Di    | odę       |

| Characteristic; (Improved Accuracy)             | 232       |

| A.3. Test on the Accuracy of the Two Methods of |           |

| Analysis of the Tunnel Diode Relaxation         |           |

| <u>Oscillator</u>                               | 236       |

| A.4. Accuracy of the Analytical Expressions for | the       |

| Tunnel Diode Relaxation Oscillator Loaded       | оу        |

| a Transistor                                    | 239       |

| A.5. Constant Current Source                    | 240       |

| A.5.1. Sensitivity to Supply Fluctuations       | 242       |

| A.5.2 Thermal Drift                             | 243       |

|                                                      | 10   |

|------------------------------------------------------|------|

|                                                      | page |

| A.5.3. Output Impedance of Current Source            | 244  |

| A.5.4. Performance of Current Source                 | 244  |

| A.6. Trimming of the Tunnel Diode Chain for          |      |

| Improved Accuracy                                    | 246  |

| A.7. Characteristics of the Tunnel Diode Chains      | 251  |

| A.8. Measurements of the Thermal Coefficients of     |      |

| the Chains                                           | 255  |

| A.9. Tunnel Diode Specifications                     | 259  |

| A.10. Transient Response of the Resetting Transistor | 260  |

| A.10.1. Current Available from Monopulser            | 260  |

| A.10.2. Risetime at the Output of the Chain          | 262  |

| A.10.3. "Switching On" of the Resetting              |      |

| Transistor                                           | 265  |

| A.10.4. "Switching Off" the Resetting                |      |

| Transistor                                           | 268  |

| A.11. Analysis of Precision Requirements in the      |      |

| Quantizer                                            | 271  |

| A.ll.l. List of Symbols                              | 273  |

| A.11.2. Basic Equation                               | 276  |

| A.11.3. Computation of Zero Conditions               | 279  |

| A.11.3.1. Nominal Value of $E_3$                     | 279  |

| A.11.3.2. Range of Adjustments of $E_3$              | 280  |

| A.11.4. Summary of Prevailing Conditions for         |      |

| the Remaining Part of the Analysis                   | 281  |

| A.11.5. The Decoder Unit                             | 281  |

|       |                                                | 7.7  |

|-------|------------------------------------------------|------|

|       |                                                | page |

|       | A.11.5.1. Computation of $R_1$                 | 282  |

|       | A.11.6. Precision in Tunnel Diode Chains       |      |

|       | (No Cycling Operation)                         | 283  |

|       | A.11.6.1. First Decades                        | 283  |

|       | A.11.6.2. Second Decades                       | 285  |

|       | A.11.7. Precision Required in the Voltage      |      |

|       | References During the Cycling Process          | 285  |

|       | A.11.7.1. Reset Reference Unit Switched        |      |

|       | On                                             | 286  |

|       | A.11.7.2. Both Chains Being Stepped            |      |

|       | Simultaneously                                 | 289  |

|       | A.11.7.3. Reset Reference Unit                 |      |

|       | Switched Off                                   | 291  |

| A.12. | Computation of the Precision Requirements in   |      |

|       | the Quantizer                                  | 292  |

|       | A.12.1. List of Symbols Used in Appendix A.12. | 292  |

|       | A.12.2. Sources of Error in the Chains         | 294  |

|       | A.12.3. Sources of Error in the Reset          |      |

|       | Reference Unit                                 | 295  |

|       | A.12.3.1. Analytical Expressions for           |      |

|       | Reset Reference Voltages                       | 295  |

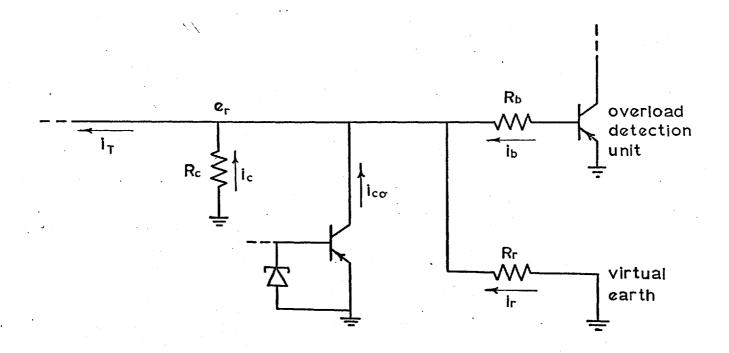

|       | A.12.3.2. Calculation of $E_r$ and $i_T$       | 299  |

|       | A.12.3.3. Investigation of the Various         |      |

|       | Error Terms                                    | 300  |

| A.12.3.4. Expressi         | ion for ${\tt X_r}$ as a Function |             |

|----------------------------|-----------------------------------|-------------|

| of the                     | Temperature Range                 | 304         |

| A.12.4. Precision Requirem | ments for the Chains              | 304         |

| A.12.4.1. Precision        | on Requirements During            |             |

| the Cyc                    | cling Process                     | 305         |

| A.12.4.2. Temperat         | ture Coefficient of the           |             |

| Reset B                    | Reference Unit                    | 307         |

|                            |                                   |             |

| Pantagaaaa                 |                                   | <b>71</b> 0 |

## Introduction.

The work described here has been carried out in the Engineering in Medicine laboratory of Imperial College and has been intended to assist current research in biophysics. One of the most striking features of biophysical research is probably that it covers a large variety of widely differing problems. This situation arises from the complexity of the subject under study and it creates a need for correspondingly versatile laboratory equipment capable of coping with a variety of often unforeseeable operating requirements.

The problem was presented a few years ago, in conjunction with the requirements of the laboratory, of investigating the potentiality of adaptive circuit techniques in the design of highly flexible laboratory equipment intended primarily for physiological measurements. In the present context, the term "adaptive" was used to describe a class of circuits in which the mode of operation or the transfer characteristic can be altered according to the behaviour of an input signal. Furthermore, it was decided to couple this study of a new potentially adaptive circuit to an investigation of the possibility of employing tunnel diodes to generate accurately defined staircase waveforms which would constitute a stepping reference in the new system and would permit a considerable reduction of the

circuit complexity. The fundamental idea was to use such a voltage reference to track an input variable at a speed depending on some dynamic characteristic of the signal itself and with an easily controlled accuracy. It is easy to imagine that such a system could find many applications in measurements, control as well as transformation of electrical signals. Indeed, an ultimate purpose of this entire study would be to assess the potentiality of such a scheme as the basis of more specifically adaptive operations on signals.

In order to demonstrate some of the salient features of this technique, a new analogue-to-digital converter was designed. The reasons for the choice of this particular application are explained in Chapter 1. It will be shown in that chapter that an adaptive analogue-to-digital converter can prove most useful in a bio-physical laboratory and how it is proposed to build such a converter. Chapter 2 will be devoted entirely to the design of a tunnel diode stepping reference unit. Finally, the remaining part of the thesis will be concerned with the auxiliary circuits completing the quantizer and with a description and evaluation of the over-all performance of the system.

#### CHAPTER 1.

Introduction to the Purpose and Design of an Analogue-to-Digital Converter.

# 1.1. A Note on Electronic Computers.

The well established independent techniques of analogue and digital computation have been supplemented in recent years by techniques simultaneously drawing upon both procedures for the solution of appropriate problems.

It has been common practice to classify electronic computers into two separate groups. Those operating basically on continuous signals are referred to as analogue computers<sup>2</sup>, and sequential machines capable of manipulating quantized information are generally called digital computers. A more fundamental approach, advocated by McLeod in 1962<sup>4</sup>, was well illustrated in an earlier paper by Glinski<sup>5</sup>. According to his argument, Glinski considered all computers as "processors" and defined the so-called analogue computers as "parallel sequence analog processors with continuous information". Similarly, what is popularly known as digital computers were: "serial sequence analog processors with digitized information". important characteristic of this classification is that it stresses the complementary aspects of the two methods.

## 1.2. Needs for Analogue-to-Digital Converters.

Once the concept of complementarity of analogue and digital computers has been introduced, it follows that a true hybrid machine combining the desirable features of both systems, could become a versatile and powerful tool. Various attempts to achieve this goal have been described in the literature 6,7,8,9,10 Another way of attaining the same results is to utilize each type of computer to solve those parts of one problem for which their characteristic procedures are best suited 11,12. In this case, some means of interconnecting the analogue and digital computers must be devised as the two units are not directly compatible. The equipment performing the transformation of an ahalogue (continuous) signal into a digital (quantized) form is known as an analogue-to-digital converter (A-D converter). inverse operation is effected with a digital-to-analogue Similar occasions for conversion arise whenever converter. a digital computer is introduced into a physical system 13. In its broadest sense, this last comment applies also to many cases of data handling where the information is available in an analogue form (for instance, continuous voltage signals from a transducer) and when it is desired to take advantage of the special storage facilities offered by digital systems. The utility of digital computers in most of these applications is therefore conditioned by the ability of the A-D converters to meet the various requirements imposed by the input signals.

# 1.3. Survey of Literature on A-D Converters.

The large volume of technical literature accumulated over the last few years on the description of new A-D converters is one indication of the significance of such devices to the ever increasing versatility of digital computers. Long lists of existing converters have been published already 14,15. Sorting out such a mass of information is not an easy task. A possible method of classification of all types of A-D converters, whether mechanical, electrical or else, can be found in volume II of "Analogue Computation" by Fifer 16.

## 1.3.1. Classification of Voltage-to-Digital Converters.

The present work, however, is concerned only with those A-D converters accepting electrical inputs. A comparative survey recently published 17, classified all such converters into four main groups according to their rate of analogue-to-digital conversions per second. The four divisions were listed as follows:

Low speed - up to 10 conversions/second

Medium speed - 10 to 1000 conversions/second

High speed - 1000 to 100000 conversions/second

Video speed - 100000 to 10000000 conversions/second

A description of the various techniques achieving these different speeds is given in the above reference and will not be repeated here.

However, the number of conversions/second is a measure which does not contain sufficient information by itself and the associated precision must be known before much can be said about the performance of a given converter. The present state of the art in analogue-to-digital conversion can be summarized as follows. A precision of 0.01% of full scale is possible at a speed as high as 20,000 conversions/second with converters using successive approximation techniques 17. For a precision of the order of 0.1% of full scale, speeds between 50,000 to 100,000 conversions/ second can be attained 18,19,20. Much higher conversion rates have been reported 21,22. Reference 22, for instance. describes a scheme working on a combined serial-parallel principle, operating at a clock frequency of 300Mc/s. many as 50 million conversions can be carried out every second at a precision of 1.5%. Between these extremes of speed and precision, a number of converters have been developed to satisfy the needs created by a large array of applications<sup>23</sup>,24,25,26,27,28.

# 1.3.2. General Remarks.

It is not the purpose of the present discussion to establish the relative merits of existing converters as a fair comparison can only be based on an adequate knowledge of the intended applications. On the other hand, certain general conclusions can be drawn after a careful study of

the literature.

Firstly, for any given technique, a higher conversion rate is normally possible at the cost of reduced precision.

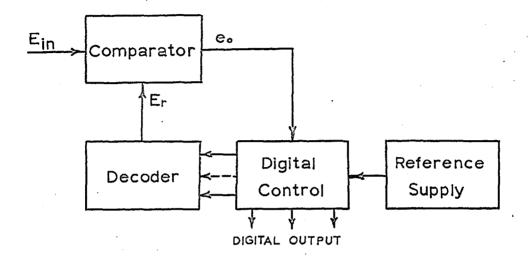

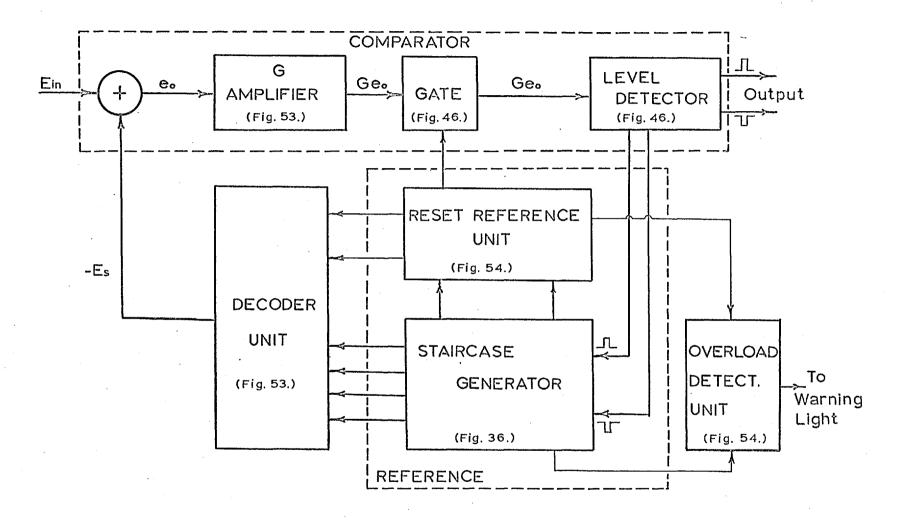

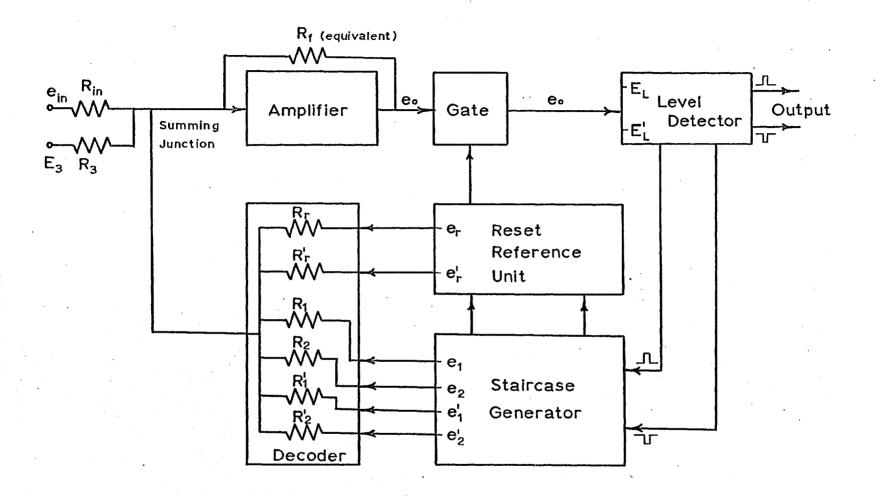

Secondly, most high speed accurate A-D converters can be represented as refined versions of the unit described by the basic block diagram of figure 1. The function of every unit should be evident from its name and only a brief explanation needs to be given. The comparator produces an error signal, eo, which is dependent on the relative amplitudes of the input signal, Ein, and the reference signal, E<sub>r</sub>. That error signal operates a digital control unit which uses an accurate reference supply to produce a certain digital code. The feedback action from the decoder tends to reduce  $e_{\Omega}$ . A digital representation of Ein is obtained whenever En approaches Ein within less than the equivalent of the least significant digit of the system.

Finally, no single A-D converter is likely to best solve all problems. To a certain extent, a converter must be tailored in accordance with the characteristics of the signal to be transformed; this is of course the main reason for the large variety of converters already available or under development. As for all engineering problems, the design of analogue-to-digital conversion equipment must take into account such features as flexibility, performance,

# BASIC BLOCK DIAGRAM OF ELECTRONIC A-D CONVERTERS

Fig. 1.

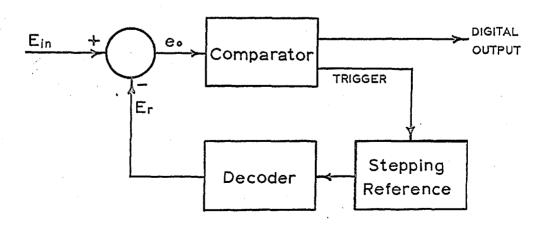

# BASIC BLOCK DIAGRAM

# OF PROPOSED CONVERTER

Fig. 2.

reliability, cost, size and maintenance. The final choice involves a number of compromises depending on the order of priority assigned to these various factors.

These basic considerations will now be used as a guide in establishing the specifications for a new A-D converter.

## 1.4. Proposed Analogue-to-Digital Converter.

# 1.4.1. Specifications.

It is often necessary to handle large quantities of information presented as analogue electrical outputs, say, of transducers; this situation arises particularly, for example, in bio-physical research. This application is of special interest in the context of the laboratory where the present work has been conducted. A most powerful method of tackling such problems is to express these signals into a digitally coded form and to use a digital computer to analyse the results. A suitable A-D converter to serve such a purpose would be required to meet the following specifications.

- (a) The frequency range should extend from very low, i.e. a fraction of a cycle per second, to approximately 10Kc/s.

- (b) A precision better than 1% should be maintained up to about 1Kc/s.

- (c) Low speed operation at 0.1% precision may be needed in certain cases and should not exceed the absolute limit imposed by the method used.

- (d) Facilities for trading precision for speed would represent a significant advantage as it would allow for higher conversion rates when necessary.

- (e) The converter should accept positive and negative input signals of a fraction of a volt as well as tens of volts full scale amplitude. It means that the lower limit for the least significant digit should be equivalent to no more than a few millivolts.

- (f) Provision to balance out large DC components from the input signal and to shift the zero level at the input over the full dynamic range may also prove useful.

From the survey outlined in section 1.3., it can be concluded that in principle, specifications similar to those mentioned should lie within the potentiality of existing A-D converters. In practice, however, it is difficult to select a unit combining all of these properties. In order to obtain the desired performance, it is necessary to resort to complex and

expensive devices which for many purposes would be utilized in a very inefficient way. Even so, the rigidity of the practical scheme would often limit the range of possible uses.

It was therefore felt desirable to consider the possibility of designing an A-D converter especially suited to the conditions just described. The particular interest of the Engineering in Medicine laboratory in physiological measurements has dictated that special attention be paid to the feasibility of trading speed with precision for various purposes; many biological measurements demand low precision (5%) and high speed while, for others, a precision of one or two orders better, Indeed, it became clear that at low speed is desirable. such an instrument could be not only of real value in biological engineering but would prove equally useful in a number of similar situations. It was thus decided to conceive the new A-D converter as a piece of general laboratory equipment i.e. which could be utilized flexibly for various purposes requiring different speeds and The specifications already established were precision. consequently orientated towards achieving maximum system flexibility while reducing complexity, maintenance and cost to a minimum. The argument leading to the proposed form of solution will now be outlined.

## 1.4.2. Proposed Solution.

Before pursuing the detailed development of the A-D converter, certain decisions were required regarding the choice of a method of approach.

In the light of the experience gained from a survey of the literature, it seemed that a converter of the asynchronous and incremental type offered the possibility of an interesting solution. It was realized that such a system would be inherently compatible with the special emphasis on flexibility. This point can be clarified by a brief description of the fundamental properties of incremental devices. In an incremental converter, a single signal event indicates when the input variable has changed by one quantum interval corresponding to the smallest unit of measure in the system. These events are then added through pulse counting or similar techniques and the excursions of the controlled variable are time integrals of these data pulses. The level reached by the input signal at the instant a pulse is generated, becomes automatically the zero reference level for the next displacement.

A block diagram representation of the proposed A-D converter is given in figure 2. Its operation is easy to explain on an incremental basis. Whenever the

error signal,  $e_{\rm C}$ , obtained from the difference between the input variable,  $E_{\rm in}$ , and the feedback voltage,  $E_{\rm r}$ , reaches a given positive or negative amplitude, the comparator generates an output pulse of the corresponding polarity. At the same time, the reference is adjusted by one quantum interval, returning  $e_{\rm C}$  to zero and establishing the next level of operation. The advantages of this technique will be discussed in detail in Part II of the thesis but certain points must be elucidated here.

It was recognised that to avoid using a fixed clock pulse frequency and to adopt a completely asynchronous system would minimize restrictions on the flexibility of the resulting apparatus. Some design problems may be simpler in synchronous machines but it is believed that the extra difficulties were outweighed by the advantages of having a converter capable of adjusting its pace to the characteristics of the input signals. In this respect, the proposed converter may be described as a true quantizer because the input signal is transformed according to equal increments of amplitude rather than being sampled at fixed time intervals. The number of conversions per second is high for a rapid rate of change,  $\Delta V/\Delta t$ , of the input signal and decreases for slowly varying inputs. It will be seen later that this property provides a simple means of trading precision for speed and

vice versa. It is to be emphasized that in this trading capability lies much of the significant potential of a scheme of this type.

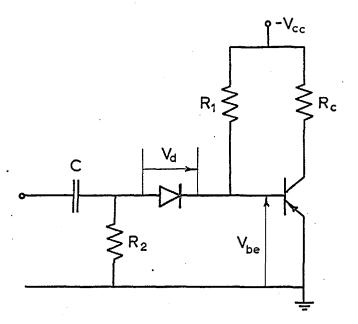

The problems related to the design of the comparator also had an important bearing on the choice of the particular layout shown in figure 2. As already mentioned (section 1.3.2., figure 1), most A-D converters employ a comparator of some kind. Certain methods use only one comparator operating over a large dynamic range (serial methods) while others replace this by a number of comparators each acting at a different level (parallel Serious objections could be raised against both approaches for the present application. A large number of parallel units would increase the complexity and the cost of the system. On the other hand, a high speed comparator with an expanded dynamic range would be difficult to build and would have a limited accuracy. In order to avoid these obstacles in an incremental machine, the feedback from the decoder can be applied to a differential input stage, allowing the comparator to operate from an error signal over a fixed amplitude range. This expedient simplifies considerably the design of the comparator. Any error introduced at that stage represents only a fraction of one quantum interval and is likely to be smaller than the quantization error itself. Furthermore, if the polarity of the reference is opposite to that of the input signal, a simple summing junction effectively replaces the difference unit. Any subsequent amplification of the error signal is free from linearity problems as only one level on each side of zero is detected by the comparator. The decoder itself is usually a network of accurate weighing resistors. One is therefore left with the stepping reference as the only unit in the converter required to maintain its accuracy over a large dynamic range.

# 1.4.3. Comparison with Delta Modulation.

Before studying the requirements imposed on the reference circuit, an interesting parallel can be established between the system just described and another existing type of A-D converter.

with the simple addition of a clock pulse generator, the block diagram of figure 2 would illustrate the principle of delta modulation. This appellation normally refers to a pulse code modulation technique primarily intended for the transmission of audio 29 or video 30 signals. It employs a one-digit code and therefore makes the sampling frequency equal to the clock pulse repetition rate. The method is well known and adequate descriptions may be found in the above references. For the sake of comparison, the present converter can be

regarded as a case of delta modulation with a clock rate proportional to the slope of the input signal. Apart from this important difference and its logical consequences, both systems operate in a similar fashion generating a one-digit code representation of the input signal. Furthermore, the mathematical expression for the maximum input frequency as a function of amplitude for a delta modulation system<sup>29</sup>, is identical to the corresponding equation to be derived later for the present converter. In this case, the clock frequency must be replaced by the maximum pulse repetition rate of the reference level generator.

The absence of a fixed clock pulse frequency in the converter under study, prevents the comparison from being pursued further. Another significant difference between the two systems arises out of the distinctive ways of generating the reference signal. It will be seen later that the output from the decoder is not obtained from the integration of the output pulses as in delta modulators. In fact, with the new reference generator, problems of instability in the closed loop are practically nonexistent.

A few general remarks on analogue-to-digital conversions will now lead to the basic requirements for the reference unit.

# 1.4.4. Basic Requirements for the Reference Unit.

The instantaneous accuracy of a given quantization process depends on the magnitude "q" of the quantization interval. The quantization error at any point can be defined as  $\frac{1}{2}q/2$ , suggesting that the quantized signal will always lie at or within these limits from the exact value. If it is desired for some reason, to keep the quantization error to a small fraction of the full scale, the number of defined levels must be increased sufficiently. It should be remembered that good filtering is necessary in order to recover the signal if only a few levels are used. The instantaneous accuracy is of prime importance whenever the quantized signal is utilized as such with little filtering. analog-to-digital converters, used in conjunction with computers, must introduce negligible quantization errors. However, dividing a given dynamic range into a greater number of intervals in order to reduce the quantization error can impose severe limitations on the speed of the A simple example will demonstrate the implicaconverter. tions of this statement.

Example: Suppose that a quantizer divides a given voltage range into 1000 intervals. Theoretically, the quantization error can be as small as ± 1 part in 2000 or ± 0.05% of full scale. If a

comparison method is used, as in the present case, the number F of steps available from the reference per unit time limits the maximum voltage variation per unit time (  $\Delta V/\Delta T$ ) acceptable at the input. The steps must be equal to the full scale amplitude divided by one thousand and the following inequality must be satisfied at all times.

$Fx(full scale amplitude)/1000 \ge \Delta V / \Delta T$

If the maximum slope of a sinewave is expressed as  $\pi fA$ , where f represents the frequency and A the peak-to-peak amplitude, the maximum frequency of a full scale sinewave that the quantizer will follow can be deduced from the above inequality. A lkc/s signal, for instance, would require the reference to operate at a speed greater or equal to  $1000 \ \pi f$  or  $F \ge 3.14 \times 10^6$  steps/sec.

This result points out the need for a high value of F (steps/sec available from the reference), even for relatively low frequencies of the input signal, if the quantization error is to be very small. Fortunately, trading accuracy for speed and vice versa is normally possible with such a system. If the number of quantization intervals is

decreased for a fixed dynamic range, the amplitude of the steps consequently increases. Assuming that the speed F (step/sec) of the reference remains the same, the maximum slope acceptable by the quantizer is proportionally larger. The quantization theory shows that in many cases, a small number of levels is perfectly adequate as long as certain conditions are satisfied. This theoretical point will be considered in a later study of the system as a whole.

The ultimate performance of the quantizer therefore depends on the extent to which the reference staircase generator can meet the speed and precision requirements.

It is now intended to enumerate the problems related to the design of this most important part of the system and to explain in detail the various steps leading to their solution.

PART I

Design of the High Speed Stepping Reference.

CHAPTER 2

Design of a Building Block.

## 2.1. Preliminary Remarks.

The first question to be answered at an early stage was how to define between one hundred to one thousand voltage or current levels extending on both sides of zero with the facilities to step up or down one level at a time at a speed possibly extending to ten million levels per second.

A number of methods were envisaged, making use of pulse counters, coincidence detecting circuits, integrators, etc... Most of these approaches were discarded in view of the further requirement for any one level to be kept as an accurate reference for long periods of time. It was finally decided to interconnect multistable circuits through weighing impedances to define the necessary levels. This principle has been applied in most of the existing digital voltmeters where binary circuits are combined to reproduce a given numerical code.

To obtain a large number of levels using binary circuits as the building block necessitates many of these units. As long as they are simple and inexpensive units, this solution is acceptable. In the present case however, the problem was slighly different from the example of the relatively slow digital voltmeter. The higher speed required (10 Mc/s p.r.r) would have called for expensive switching components together with careful design procedure if transistors had been used.

In the light of these remarks, the high switching speed possible with tunnel diode circuits seemed to be an interesting proposition for the reference staircase generator. Furthermore, tunnel diodes lend themselves to simple multi-stable circuits as will be shown later. Their use simplified considerably the design of the building block to be introduced in this chapter.

# 2.2. The Tunnel Diode.

The tunnel diode is a heavily doped semiconductor junction diode. Its characteristic shows a voltage-controlled negative resistance.

This behaviour has been explained by Esaki as being due to quantum-mechanical tunnelling of carriers through a narrow p-n junction<sup>31</sup>. The tunnel effect is a process wherein particles can disappear from one side of

a potential barrier and appear almost instaneously on the other side. According to the laws of quantum theory, the space charge depletion region of a p-n juntion must be made extremely thin before the probability of tunnelling becomes significant.

A simple way of explaining qualitatively the generation of the tunnel current in a diode is to consider the effect on the characteristic of a p-n junction, of increasing the concentration of the free carriers in the semiconductor crystal. A direct consequence would be to decrease the breakdown voltage of the junction in the The extent to which the breakdown reverse direction. voltage can be reduced, is limited by the solubility of the impurities determining the carrier concentration. For many semiconductor materials, this limit is greater than what is needed to reduce the breakdown voltage to In these cases, the junction can still be in the zero. reverse breakdown condition at a slight forward bias. Application of a larger forward voltage would bring the junction out of the breakdown condition and the current would fall to a smaller value. The junction would finally behave in a similar fashion as a normal diode taking into account the difference in construction.

Qualitative physical description of the tunnel diode junction in terms of electron energy band theory,

can be found in the literature <sup>32</sup> and will not be included here. References 31-33 and 34 present a more rigorous analysis of the tunnel diode junction. These theoretical derivations will not be unnecessarily reproduced here and the device will now be investigated as a circuit element.

## 2.2.1. The Tunnel Diode as a Circuit Element.

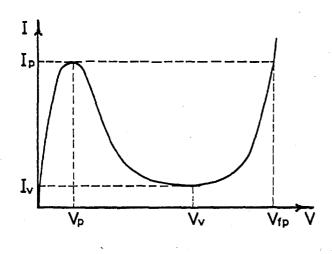

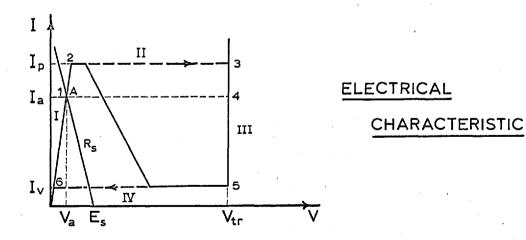

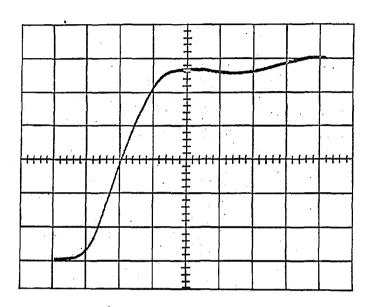

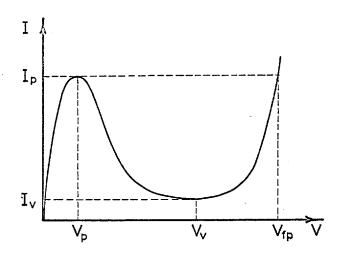

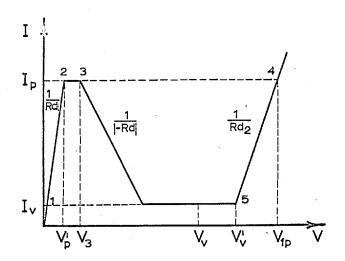

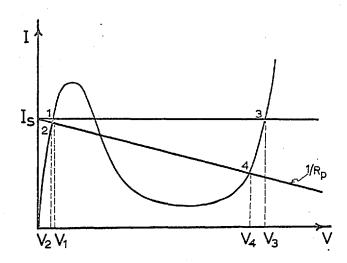

Figure 3 shows the static characteristic of a tunnel diode. This I vs V curve is voltage controlled and is made up of two positive resistance regions separated by It is worth noting that the one negative slope. characteristic of figure 3 has been obtained from accurate measurements taken on a 1N2941 tunnel diode. quent figures representing the tunnel diode curve or its linear approximation, have been derived equally from these Whenever possible, the same scales have been results. preserved on the co-ordinates in order to permit direct comparison between the figures of different sections. The curve of figure 3 can be described by the following points:

- I peak point current, the maximum tunnel diode current to the left of the negative resistance region.

- $V_p$  = peak point voltage, the voltage across the diode when  $I=I_p$ , to the left of the negative resistance region.

Fig. 3,

SMALL SIGNAL EQUIVALENT CIRCUIT FOR NEGATIVE REGION

Flg.4.

- $\mathbf{I}_{\mathbf{V}}$  = valley point current, the minimum diode current to the right of the negative resistance region.

- $\mathbf{V}_{\mathbf{v}}$  = valley point voltage, the voltage at which  $\mathbf{I} = \mathbf{I}_{\mathbf{v}} \text{ to the right of the negative resistance}$  region.

- $V_{\mathrm{fp}}$  = forward peak point voltage, the voltage across the diode for  $I=I_{\mathrm{p}}$  in the high voltage region (to the right of  $V_{\mathrm{v}}$ ).

The peak point current,  $I_p$ , is controlled by an etching process and can be held to within  $\pm 2.5\%$  or better on a production basis  $^{32}$  (pege 12). Tunnel diodes can be made with peak currents anywhere from a few microamps to several amperes. When the peak current is less than about 50  $\mu\text{A},$  the device is often called a "backward diode" and is used in the reverse direction as a rectifier in conjunction with tunnel diode circuits because of its low voltage drop.

The peak point voltage,  $V_p$ , the valley point voltage,  $V_v$ , and the forward peak point voltage,  $V_{fp}$ , are fixed to a certain extent by the semiconductor material. Table I compares between typical voltages obtained with germanium, silicon and gallium arsenide tunnel diodes.

| Material | V <sub>p</sub><br>mv | V <sub>v</sub><br>mv | V <sub>fp</sub><br>mv |

|----------|----------------------|----------------------|-----------------------|

| Ge       | 55                   | 350                  | 500                   |

| Si       | 75                   | 450                  | 750                   |

| GaAs     | 150                  | 500                  | 1200                  |

#### TABLE I

The higher voltages obtainable with GaAs combined with a possibly greater  $I_p/I_v$  ratio, seems to suggest the choice of this material as being more advantageous. At the present, however, germanium diodes are generally cheaper and are available from a large number of firms. This situation is due mainly to special difficulties encountered in the production of reliable GaAs tunnel diodes.

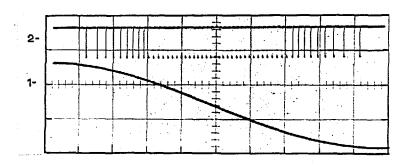

It appears from the previous description of the tunnel diode characteristic, that the slopes in the three regions are directly related to the magnitude of the peak current  $I_p$ . The negative resistance in particular is nearly inversely proportional to  $I_p$ , imposing certain limitations on the design of tunnel diode oscillators and amplifiers  $^{32-33}$ . A useful linear approximation of the negative resistance can be computed as 0.4 times the resistance joining the peak point,  $(I_p, V_p)$ , to the valley point,  $(I_v, V_v)$ .

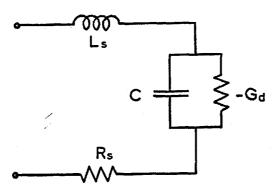

Before analysing the switching action of a tunnel diode, one more question is worth answering. What parameters will limit the speed of a tunnel diode as a The tunnel effect is responsible for circuit element? the generation of the negative resistance. This basic conduction mechanism has a theoretical frequency limit of the order of 10<sup>7</sup> megacycles per second. This figure cannot fail to strike the imagination of circuit designers familiar with the many times slower mechanisms of drift or diffusion involved in conventional diodes and transistors. However, the equivalent circuit of the tunnel diode operating in the negative resistance region (fig. 4.), can be used to demonstrate the drastic effect of some parameters on the frequency response of the practical device.

In this diagram,  $R_s$  represents the total series resistance determined mainly by the bulk of the semiconductor material. The inductance,  $L_s$ , is limited by the minimum inductance of the leads or the package. The capacitance, C, is the summation of the capacitance of the junction and the capacity introduced by the package and the leads. Finally,  $-g_d$  is the slope of the characteristic at the particular bias point under consideration and can be assumed independent of frequencies.

If the impedance of the tunnel diode in the negative region is computed from the equivalent circuit,

two significant cut off frequencies can be derived. One is the resistive cut off frequency,  $f_{ro}$ , and is defined as the frequency at which the real part of the tunnel diode impedance goes to zero. The device will not amplify above this frequency. The second point of interest is the self-resonant frequency,  $f_{xo}$ , and it occurs when the imaginary part of the diode impedance goes to zero. No oscillation can be sustained above this frequency. Expressions for  $f_{ro}$  and  $f_{xo}$  are easily derived 32 (page 14).

$$f_{rc} = \frac{|gd|}{2\pi C} \sqrt{\frac{1}{Rs |gd|} - 1} \qquad .. (1)$$

$$f_{xo} = \frac{1}{2\pi} \sqrt{\frac{1}{LsC} - \left(\frac{gd}{C}\right)^{2}} \qquad .. (2)$$

For a typical 1N2941 germanium tunnel diode in a TO-18 package, manufactured by General Electric, the relevant parameters given in the data sheet are as follows: C = 15 to 50 pf;  $L_s = 6$  to 19 x  $10^{-9}$  henries and  $\left| -g_d \right| = 0.03$  mhos. In this case, with the minimum values of C and  $L_s$ ,  $f_{ro} = 2.58$  KMc/s and  $f_{xo} = 420.3$  Mc/s.

In practice, the cut off frequencies are circuit dependent and may be considerably smaller unless great care is taken to keep the inductance of the leads and the external parallel capacitance to a minimum. It should

therefore be remembered that operation above a few hundred megacycles is not always possible with all tunnel diodes. On the other hand, it can be said that most tunnel diodes are fast enough to be used advantageously in circuits operating at frequencies up to some twenty to fifty megacycles per second without any special difficulties. It will be seen later on that switching from one side of the negative resistance region to the other side can readily be effected in less than 10 nanoseconds with a 1N2941 tunnel diode loaded by a transistor.

#### 2.2.2. Basic Circuit.

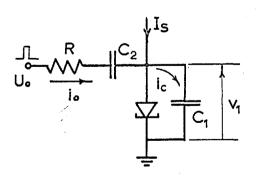

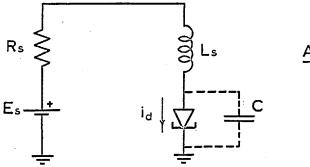

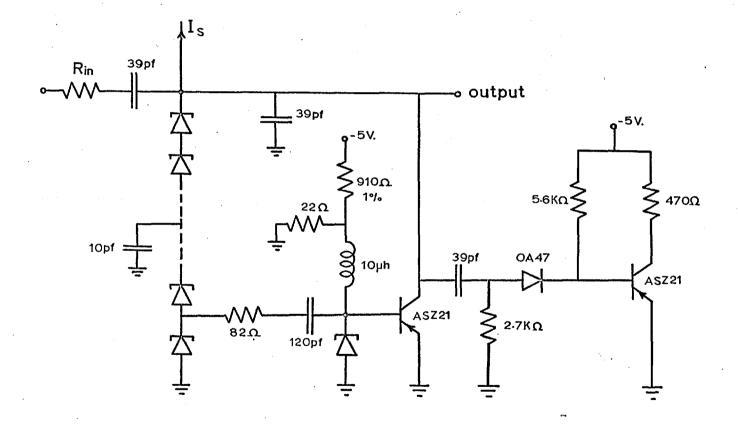

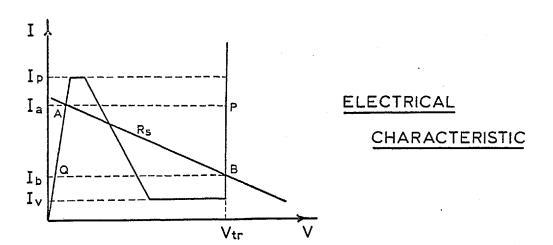

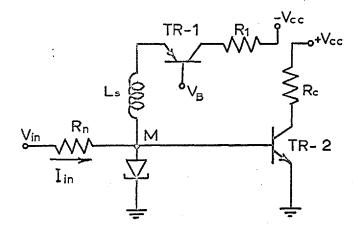

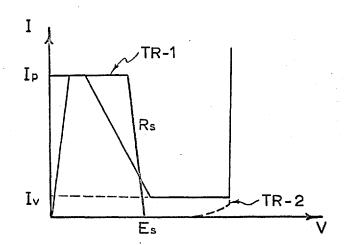

A study of the simple tunnel diode circuit of figure 5, will provide enough information for the design of all subsequent circuits required by the staircase generator.

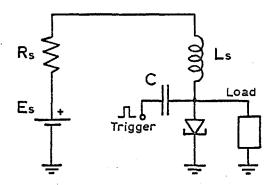

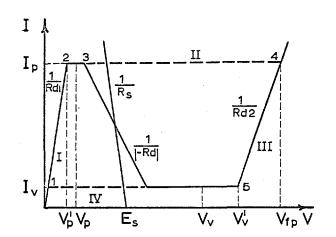

This basic circuit consists of a voltage source,  $E_{\rm S}$ , in series with a resistance,  $R_{\rm S}$ , an inductance,  $L_{\rm S}$ , and the tunnel diode itself. It is assumed for the moment that the parallel load can be neglected. Figure 6 represents the static characteristic of the tunnel diode with possible values of the supply voltage,  $E_{\rm S}$ , and of the series resistance,  $R_{\rm S}$ , drawn as a load line. Reference to figure 6 is sufficient to establish the remarkable flexibility of this circuit. Suppose, for instance, that the tunnel diode is initially biased at point A and that

## BASIC CIRCUIT

Fig. 5.

# SWITCHING CHARACTERISTIC

Fig. 6.

a trigger signal increases the current above the peak,  $I_p$ . Provided that certain conditions are satisfied, switching occurs in a manner illustrated by the trajectories of figure 6, depending on the magnitude of the inductance,  $L_s$ . Adjustment of the bias voltage,  $E_s$ , and of the series resistance,  $R_s$ , (and of the inductance,  $L_s$ , in certain cases) would suffice to transform the circuit into an astable, a monostable or a bistable unit. It can therefore become a sinewave oscillator, a monostable trigger circuit, a bistable flip flop, a level detector, etc.. The analyses for the cases of the sinewave oscillator and of the amplifier can be based on the equivalent circuit of figure 4 and are derived in chapters 3 and 4 of reference 32.

However, the present work is concerned entirely with the tunnel diode as a switching element. It is now intended to consider in detail the switching action of a tunnel diode in order to acquire a better understanding of all the switching circuits based on the diagram of figure 5 and to define their operating conditions. This study will be carried out as part of a general description of the tunnel diode chain.

## 2.3. The Tunnel Diode Chain.

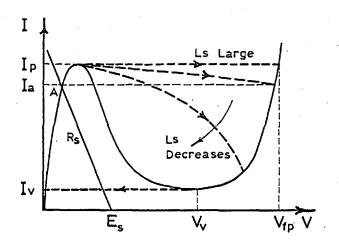

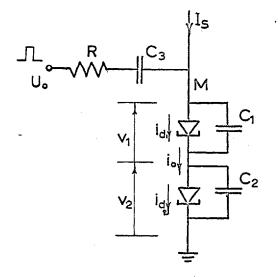

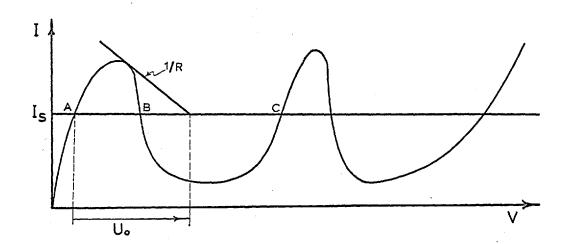

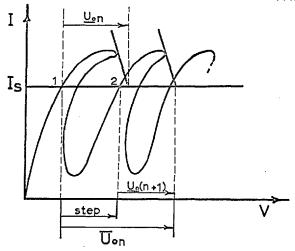

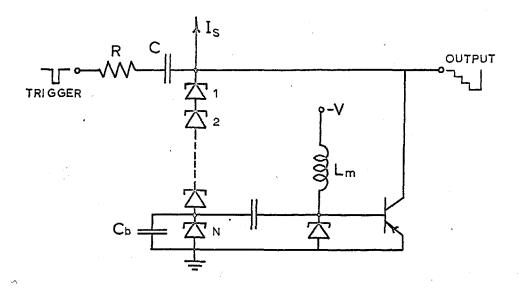

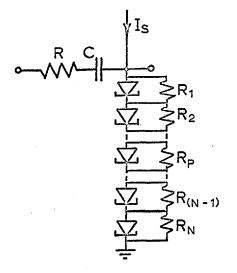

If a chain of tunnel diodes is connected to a constant current source as illustrated in figure 7, a

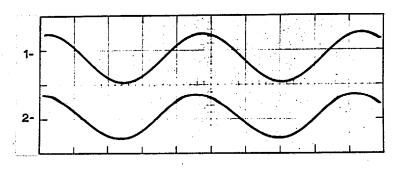

Fig. 9.

Fig. 10.

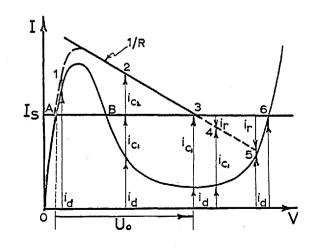

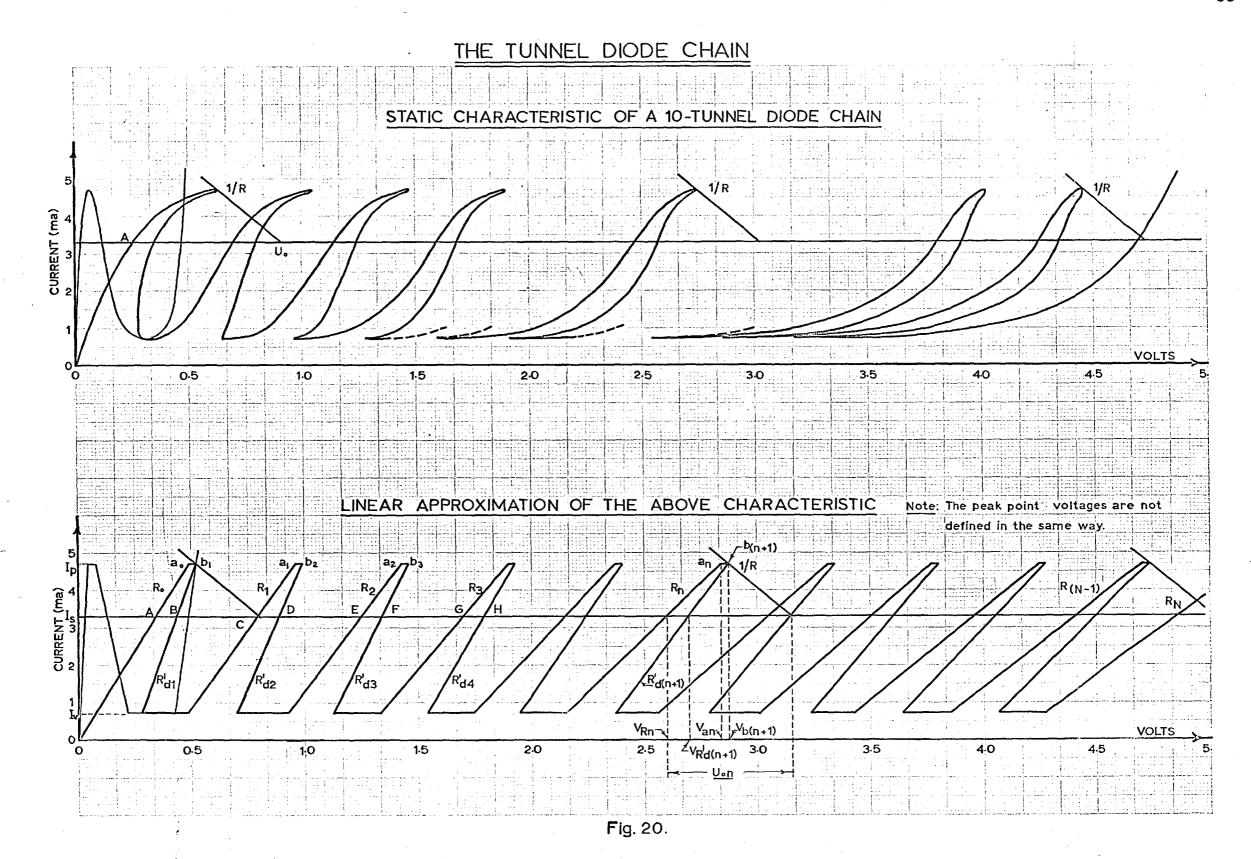

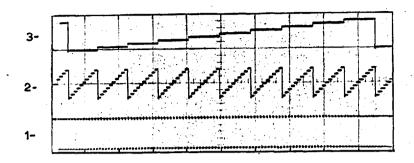

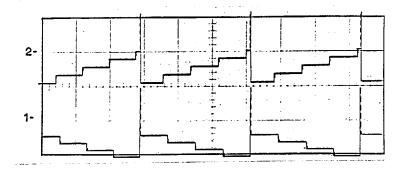

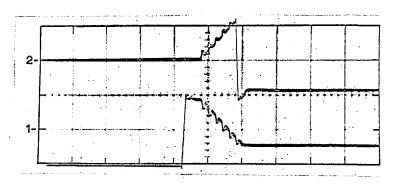

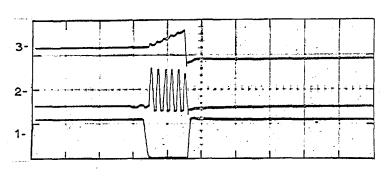

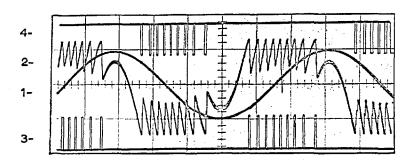

multistable circuit is obtained. The over-all static characteristic of the chain is shown in figure 8, assuming that all tunnel diodes are identical. The standing current,  $\mathbf{I}_s$ , is adjusted to a value below the minimum peak current,  $\mathbf{I}_p$ , in the chain and all the diodes are initially in their low voltage state. If a series of pulses switches the diodes one at a time to their high voltage state, a staircase voltage waveform is generated at the output.

It can be shown experimentally that, for a given range of input pulse amplitudes, only one tunnel diode can be triggered at a time. It is now proposed to establish the conditions to be met both by the tunnel diodes in the chain and by the trigger pulses for this situation to prevail. To do so, the behaviour of a single tunnel diode operated from a current source and then from a voltage source will first be analysed qualitatively. The switching of two tunnel diodes in series will then be studied. Finally, equations will be derived giving the limits of acceptable trigger pulse amplitudes for a series of N diodes biased from a constant current source.

## 2.3.1. Switching of a Single Tunnel Diode.

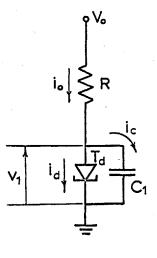

In the circuit of figure 9,  $i_d$  represents the current flowing through the ideal tunnel diode,  $T_d$ , at any instant. The voltage  $v_l$  across the diode is given by

the static characteristic of the device at a point corresponding to a current,  $i_d$ . The capacitor, C, represents the total capacitance appearing across the diode and  $i_c$  is the instantaneous current taken by that capacitance.

## 2.3.1.1. Current Drive.

In the case of a current drive, the resistance, R, is made arbitrarily large. Assume that the voltage,  $V_{\rm O}$ , is initially standing at zero and starts increasing positively. The input current, i<sub>0</sub>, also increases from zero and is divided between i<sub>d</sub> and i<sub>c</sub> in a manner illustrated by figure 10. The following equalities must be satisfied at all times.

$$i_{O} = i_{d} + i_{C} \qquad .. (3)$$

$$\Delta i_{O} = \Delta i_{d} + \Delta i_{C} \qquad .. (4)$$

Equation (4) expresses the fact that any change in  $i_0$  per unit time must be reflected as corresponding variations of  $i_d$  and  $i_c$ .

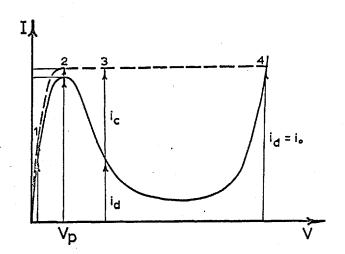

Referring to figure 10, the complete transition from point zero to point 4 can be described as follows. For the first part of the characteristic to the left of the peak, the magnitude of the capacitor current,  $i_c$ , depends on the rate of rise of  $V_o$  and is kept small by the shunting effect of the low dynamic resistance of the

tunnel diode in that region. As the peak is approached, the diode begins to look like a very large impedance and any further increase in the current, io, is taken almost entirely by the capacitor, C, i.e. the voltage, v1, starts increasing faster for a given rate of rise of in. presence of the charging current, ic, causes the voltage, v1, across the capacitor, C, to exceed the peak point voltage,  $V_{p}$ , producing a decrease of the tunnel diode current, id. From that moment on, the negative resistance initiates a regenerative action and no additional increase in in in the second is a sure complete switching of the tunnel diode to the high voltage state. Suppose, for instance, that the input current, io, is maintained constant, (  $\Delta i_0 = 0$ ), as soon as the peak point is passed. Eq. (4),  $\Delta i_c = -\Delta i_d$  and, as the tunnel diode current is decreasing,  $\Delta i_d$  is negative, giving a positive value for The increasing capacitor current causes the voltage, v1, to become still larger, producing further decrease of the diode current,  $i_d$ . After the valley point,  $(V_v, I_v)$ , is passed, the diode impedance becomes positive again and the increase of v<sub>1</sub> produces an increase in the current, id, which in turn asks for an equivalent reduction of ic, slowing down the rate of change of v1. Switching is completed when the capacitor current, ic, has been reduced to zero and the diode current, id, is equal to the input current, ic.

The same argument holds in the general case when the input current,  $i_{\rm o}$ , is not kept constant during the switching action of the diode. If  $i_{\rm o}$  increases much above the peak current,  $I_{\rm p}$ , the available capacitor current is larger and the switching time becomes shorter. In the case of a significant reduction of  $i_{\rm c}$  taking place during the switching, it is only necessary for  $i_{\rm c}$  not to fall to zero until the valley point is passed. The final value of  $i_{\rm c}$  must obviously be greater than the valley current,  $I_{\rm v}$ , if the tunnel diode is to remain in the high voltage state at the end of the switching process.

In practice, the tunnel diode would be biased from a constant current source,  $I_{\rm S}$ , and an additional current pulse would bring the operating point above the peak. In this case, the triggering pulse must not be removed before the tunnel diode current has fallen to a value below the standing current,  $I_{\rm S}$ , otherwise, the capacitor current would be reduced to zero at a point on the negative resistance and the diode would return to the low voltage state.

## 2.3.1.2. Voltage Drive.

The circuit of figure 9 can also be used to describe the switching of a single tunnel diode driven from a low impedance source. In this case, the resistance, R, is very small and it is important to emphasize the fact

that it represents the total dynamic as well as static impedance in series with the diode. In other words, any inductive effect must be minimized such that the impedance, R, remains the same even during the very fast switching transients.

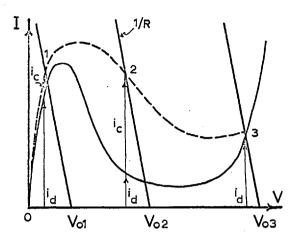

Two different conditions may prevail when the voltage,  $V_{\rm O}$ , is increased from zero depending on whether the resistance, R, is smaller or greater than the negative resistance,  $|-R_{\rm d}|$ , of the tunnel diode.

In the circuit of figure 9, the resistance, R, is effectively in parallel with the tunnel diode. becomes self-evident if the voltage source, Vo, in series with the resistance, R, is replaced by its equivalent current source, V<sub>C</sub>/R, in parallel with R. resistance, R, is smaller than  $|-R_d|$ , their parallel combination can never present a negative resistance to the current source, Vo/R, and no regeneration can take place. The circuit is therefore stable at all points and the tunnel diode can be said to possess a voltage-stable characteristic. The behaviour of the tunnel diode under these conditions is illustrated by figure 11, when the voltage, Vo, is increased from zero to a value, Vo3. exact trajectory depends on the timing of the transition of the voltage from zero to  $V_{03}$  but a possible example is given by the dotted line 0-1-2 and 3. It should be

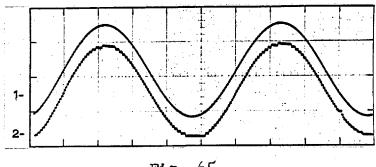

Fig. 11.

Fig.12.

Fig.13.

Fig.14.

remembered that  $V_0$  may be stopped anywhere such that the resistance, R, intersects the diode characteristic at any point and the circuit would remain stable. No switching can occur as long as R is smaller than  $|-R_d|$ .

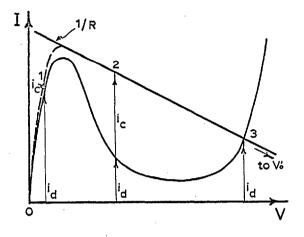

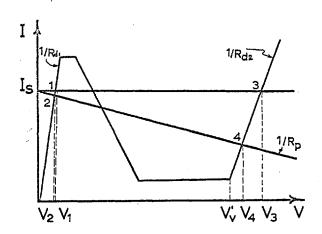

If on the other hand, the resistance, R, is made greater than  $\left| -R_{d} \right|$ , the switching action is similar to the case of current drive already explained. Figure 12 shows the trajectory, 0-1-2-3, followed by the input current,  $i_{0}$ , when the voltage,  $V_{0}$ , is increased from zero to a final value,  $V_{0}^{*}$ . It is seen that the current,  $i_{0}$ , is divided between the tunnel diode and the parallel capacitance in exactly the same way as in the case of current drive. The same equations (3) and (4) are valid and the description of the switching process need not be repeated.

## 2.3.1.3. Practical Case.

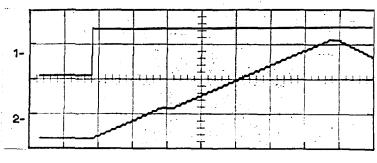

In practice, the tunnel diode is biased with a standing current,  $I_{\rm S}$ , as in figure 13. The current,  $I_{\rm S}$ , can be obtained from a voltage source in series with a large resistance or from a smaller resistance in series with an inductance providing a large dynamic impedance for faster switching. Assume that a voltage pulse is fed through a resistance, R, connected to the diode via a capacitor,  $C_2$ . The tunnel diode is initially resting at

point A (figure 14.). For complete switching to occur from the low voltage to the high voltage state, the trigger pulse must be large enough to increase the voltage across the diode from point A to point B. As soon as point B is reached, the standing current,  $\mathbf{I}_{\mathbf{s}}$ , continues to charge up the capacitances,  $C_1$  and  $C_2$ , until switching is completed, regardless of the magnitude of the resistance, R. assumed for the moment that the duration of the input pulse is longer than the switching time. Point 6 in figure 14 is therefore the new operating point by the time the trailing edge of the triggering pulse applies a signal of the reverse polarity across the diode. Whether the tunnel diode resets to the low voltage state or not at that moment depends on the magnitude of Is relative to the valley current, I, and on the amplitude of the input pulse. a diode gate is employed at the input, the effect of the trailing edge may be controlled independently of these factors and the pulse may be removed immediately after point B is passed without fear of resetting the dicde.

The minimum amplitude of the trigger pulse,  $\underline{U_O}$ , to ensure reliable switching depends on the magnitude of the resistance, R. If R is smaller than the negative resistance,  $\left| -R_d \right|$ ,  $\underline{U_O} \geq V_B - V_A$  must be satisfied. The trajectory from point A to point B depends on the rise time of  $U_O$  and can be deduced as was done for the corresponding

theoretical case (see figure 11.). The presence of  $I_{\mathbf{S}}$  in this region of the curve merely acts as a constant term and does not influence the transition from A to B.

The situation met when R is greater than  $|-R_d|$ , is not significantly different. However, it lends itself to a clear graphical representation, as shown in figure 14, and will be used to explain the influence of the resistance, R, and of the capacitor,  $C_2$ , on the switching process. In this case, the minimum input pulse amplitude is given by  $\underline{U_0} \ge V_p - V_A + R(I_p - I_s)$ . Suppose an input pulse  $U_{\rm C} = V_{\rm 3} - V_{\rm A}$  is fed into the circuit. The transition from A to point 6 in figure 14 takes place as follows. It is assumed for the moment that the input pulse width is much longer than the complete switching transient. Until point B is reached, the capacitor charging current, ic, and the part of the tunnel diode current lying above Is, are supplied entirely by the trigger pulse. point B to point 3, the standing current, Is, supplies the tunnel diode current, id, and part icl of the charging current, ic. By the time point 3 is reached, the trigger current, io, has been reduced to zero by an increase in the voltage,  $v_1$ , equal to  $U_0$  and both  $i_c$  and  $i_d$  are due entirely to Is. The further increase of volume to the current, ic, produces a reverse current, ir, to flow across the resistance, R, until point 5 is reached. charge building up across the coupling capacitor, C2,

gradually decreases the current, i, shifting the operation towards point 6, the final quiescent condition. This effect can be illustrated graphically if it is noted that the voltage appearing across C, is in series with Uo, and is effectively moving point 3 towards point 6 along the I line until the dotted part of the load line, 1/R, intersects the diode characteristic at point 6. Another approach is to consider the reduction of ir to be due to an increase of the effective driving impedance as seen by the diode. The graphical representation would then be a rotation of the dotted part of the load line about point 3 until point 5 coincides with point 6. effect of the removal of the input pulse has been explained above and is of no concern here as diode gates are normally introduced at the input. The time needed for the operating point to move from 5 to 6 depends mainly on the time constant  $(R + R_{d2})C_2$ .

The switching of a single tunnel diode has been thoroughly investigated thus far for the cases of current and of voltage drive. The results will now be utilized to study the behaviour of a series of two tunnel diodes under similar conditions.

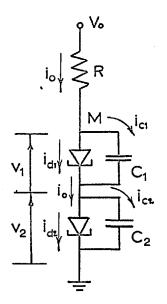

## 2.3.2. Switching of a Series of Two Tunnel Diodes.

The switching of a series of two tunnel diodes

will be investigated using the same approach as above. True current drive of the pair will be explained at first. The next case, the low impedance drive, will then be subdivided in two parts depending on whether the peak currents,  $I_{pl}$  and  $I_{p2}$ , are equal or different. Finally, the standing current will be introduced in order to elucidate the practical implications of the results.

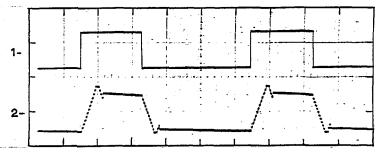

### 2.3.2.1. Current Drive of the Tunnel Diode Pair.

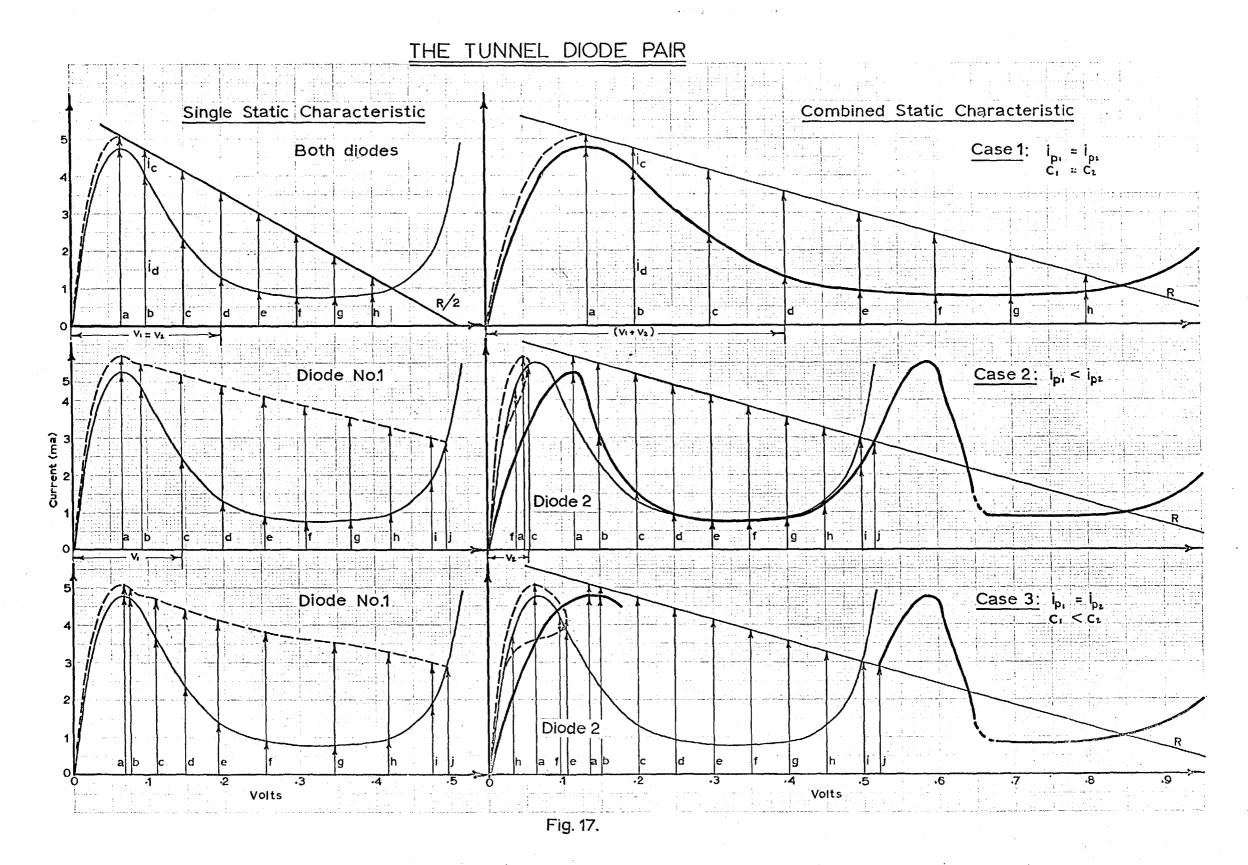

Suppose that in the circuit of figure 15, the two diodes differ only by a slight change in their peak currents such that  $I_{pl} < I_{p2}$ . The total static characteristic seen at point M is given in figure 16. If the resistance, R, is very large and  $V_{o}$  is increased slowly from zero, a current,  $i_{o}$ , starts to flow. As soon as  $i_{o}$  becomes greater than  $I_{pl}$ , the first diode switches to the high voltage state, quite independently of the presence of the second diode. The switching takes place at constant current because  $i_{o}$  is defined by a large resistance, R. The second diode does not switch until  $i_{o} \geq I_{p2}$ .

In this case of true current drive, the interaction between the two diodes is nil because the driving current,  $i_0$ , is not influenced by the changes in either  $v_1$  or  $v_2$ . This is to say that if the peak currents were

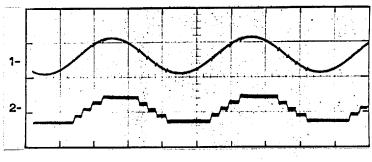

## THE TUNNEL DIODE PAIR

Fig. 15.

## COMBINED STATIC CHARACTERISTIC

Fig. 16.

identical, the two diodes would always switch together to their high voltage state.

Therefore, this driving mode relies on a difference between the peak currents in order to achieve sequential triggering of the diodes. In practice a driving current ramp could be used and the switching of the first diode could be detected as a rapid voltage change at point M by an auxiliary circuit which could stop the drive before the next peak is reached. This method necessitates the operation of the control circuit every time a tunnel diode is switched and over-all speed may be seriously impaired.

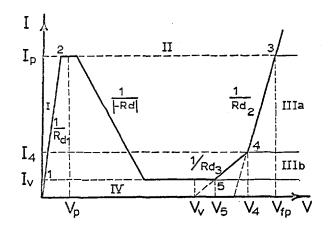

## 2.3.2.2. Voltage Drive of the Tunnel Diode Pair.

If the resistance, R, in the circuit of figure 15, is given a very low value, and the voltage,  $V_0$ , is increased from zero, the behaviour of the tunnel diodes depends on whether their peak currents are equal or not. Regardless of the prevailing conditions, the following equations must be satisfied at all times.

$$i_0 = i_{cl} + i_{dl} = i_{c2} + i_{d2}$$

.. (5)

$$V_0 = Ri_0 + v_1 + v_2$$

.. (6)

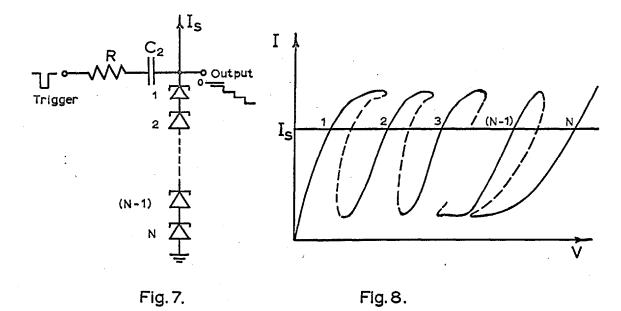

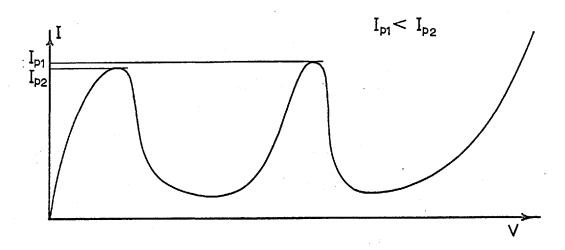

# 2.3.2.2.1. Different Peak Currents $I_{pl} < I_{p2}$ .

If  $I_{pl}$  is smaller than  $I_{p2}$ , the first tunnel diode passes its peak point before the other one. Assume at first that the resistance, R, is smaller than  $\left|-R_{d}\right|$ , the negative resistance of one tunnel diode. For the same reasons as those given for a single diode, no regeneration can occur and a voltage-stable characteristic displaying two peaks (as in figure 16 ) could be plotted point by point by slowly increasing  $V_{0}$  over a sufficient range.

Suppose on the other hand, that the resistance, R, is larger than  $\left| -R_{d} \right|$ , such that switching can occur. In this case, the first tunnel diode would switch to the high voltage state in a manner similar to that illustrated in figure 12 and already explained for a single diode. The presence of the second diode in its low voltage state can be regarded as a mere increase of the resistance, R, by an amount equal to  $R_{dl}$ . Further increase of  $V_{o}$  would then bring the operating point above  $I_{p2}$  and the second diode would switch in exactly the same way. Graphical representation of this case can be seen in figure 17. In order to ensure that the second peak is not passed before the switching of the first diode is completed, the rate of rise of  $V_{o}$  during that time must not be greater than that of  $v_{1}$  across the switching diode. In fact, it can be

seen from Eq. (6), that as long as  $v_1$  is increasing as fast or faster than  $V_0$  while  $v_2$  is not changing appreciably, the current  $i_0$  must remain constant or decrease. This limitation imposed on the rise time of the driving signal will be used to great advantage later on in order to ease the tolerance requirements on the amplitude of the trigger pulses fed to long chains of tunnel diodes.

## 2.3.2.2.2. Identical Peak Currents $I_{p1} = I_{p2}$ .

One important question has remained unanswered so far. Is it possible to use tunnel diodes with identical peak currents and still trigger them one at a time?

It has been shown earlier that, for a current drive, the answer would be no. However, provided certain conditions are satisfied in a low impedance circuit, two tunnel diodes, as in figure 15 for instance, can pass their peaks simultaneously and during the regeneration that follows, one of them can return to the low voltage stage while the other one completes its switching. In order to explain this operation, the circuit of figure 15 can be assumed to contain two identical tunnel diodes except for a slight difference in their parallel capacitances  $C_1 < C_2$ . The resistance, R, is larger than  $|-R_{\bar{d}}|$  by a small amount and  $V_{\bar{C}}$  increases slowly. As soon as the peak currents

are passed, both diodes begin to switch and  $v_1 + v_2$ increases rapidly. At first, the conditions of both diodes are identical and  $i_{cl} = i_{c2}$ . However,  $C_l$  is smaller than  $C_2$  and the voltage  $v_1$  increases faster than Consequently, the current, id, decreases more rapidly than the current, id2, for identical negative It follows from equation (5), that icl is resistances. getting larger than ice favouring some further advance of the voltage, v1, on v2. This regenerative action has been described before and will not be repeated. Meanwhile, assuming that V changes very little during the switching time of a tunnel diode, the current in is decreasing as equation (6) must be satisfied at all times. voltage,  $v_2$ , is not changing as rapidly as  $v_1$ , it is possible that the reduction of id2 may not be sufficient to account for the lowering of i and the capacitor current, ic2, starts to decrease. For small values of the resistance, R, this action may be rapid enough for ic2 to become zero at a point on the negative resistance of the second diode. At that moment, icl is still greater than zero  $(i_{c1} > i_{c2})$  and the voltage,  $v_1$ , is increasing. first diode is then getting closer to the valley point and therefore entering a region of very large negative It means that even a small decrease of the resistance. current, idl, (or of io, because of the very large

negative resistance in parallel with  $c_1$ ) would cause a large increase of the voltage,  $v_1$ . It can be seen that, for equation (6) to be satisfied under these conditions, the changes in the voltage,  $v_2$ , must be negative. A current,  $i_{c2}$ , begins to discharge the capacitor,  $c_2$ , in order to reduce  $v_2$  while the voltage,  $v_1$ , continues to increase. The action is again regenerative and the first diode completes its switching while the second one resumes its low voltage state. Figure 17 gives a graphical representation of this case.

The experience gained during the theoretical study of the tunnel diode pair, will now prove valuable in establishing the operating conditions of the practical circuit of figure 18.

## 2.3.2.3. Practical Cases.

## 2.3.2.3.1. Different Peak Currents.

The description already given for the case of two different peak currents,  $I_{pl} < I_{p2}$ , is still perfectly valid. Owing to the presence of the current,  $I_{s}$ , the trigger pulse needs to shift the operating point only from A to B, (figure 19.), and one diode switches while the other one remains below its peak. The switching action is very similar to that illustrated by figure 14. for a single unit except that the small nonlinear resistance

# TUNNEL DIODE PAIR (practical case)

Fig. 18.

## COMBINED STATIC CHARACTERISTIC

Fig. 19.

introduced by the second diode alters slightly the shape The minimum trigger pulse amplitude of the characteristic. is given approximately by  $\underline{U_0} \ge 2V_p - V_A + (I_p - I_s)R$ directly from figure 19. Provided that the rate of rise of the leading edge of the input signal is slower than the switching speed of a tunnel diode, the amplitude, U, may be larger than the minimum,  $\underline{U_0}$ , by as much as the full voltage step generated by the first diode, before the two units can be switched together. If the risetime of  $\mathbf{U}_{\mathbf{O}}$ is shorter than this limit, it was shown earlier that the input current, io, is still increasing after the first diode has passed its peak and the second diode may be triggered with the same pulse unless the difference between the peaks is widened. The tolerance requirements on Uo become correspondingly more stringent and unless the extra speed is essential, this condition should be avoided. The 1N2941 tunnel diode can switch over in less than 10 nsec and this time is more than adequate for the present The minimum amplitude,  $\boldsymbol{\mathbf{U}}_{\mathbf{O}}\text{, of input pulses, is}$ proportional to the magnitude of the resistance, R. has just been pointed out that the voltage range of acceptable trigger pulse amplitudes is a fixed value equal to the step generated across one tunnel diode. The resistance, R, should therefore be kept small in order to ease the tolerance required on Uo.

## 2.3.2.3.2. Equal Peak Currents.

The introduction of a standing current,  $I_{\rm S}$ , was shown not to modify seriously the basic operation of the tunnel diode pair from that of the theoretical case as long as the peak currents were different. On the other hand, when the peaks are identical, such that both tunnel diodes can start switching together, the presence of  $I_{\rm S}$  has a great significance. In effect, one of the diodes can return to the low voltage state only if its capacitor current is reduced to zero when the diode current is still above the intersection of the current level,  $I_{\rm S}$ , with the corresponding negative resistance. The limit has been shifted from the valley point to point B which lies much closer to the peak (see figure 19.).

It will be remembered how the interaction between the diodes was shown to engender the return of one of them to the low voltage state. The reduction of the capacitor current, i<sub>c2</sub>, to zero was a consequence of a sufficiently large discrepancy betwen the magnitudes of the negative resistances of the diodes which itself was caused by the disparity of their switching speeds. In the present context, it means that the faster diode must approach the valley region before the other one has reached point B. Therefore, the high frequency performance of the two units must differ considerably.

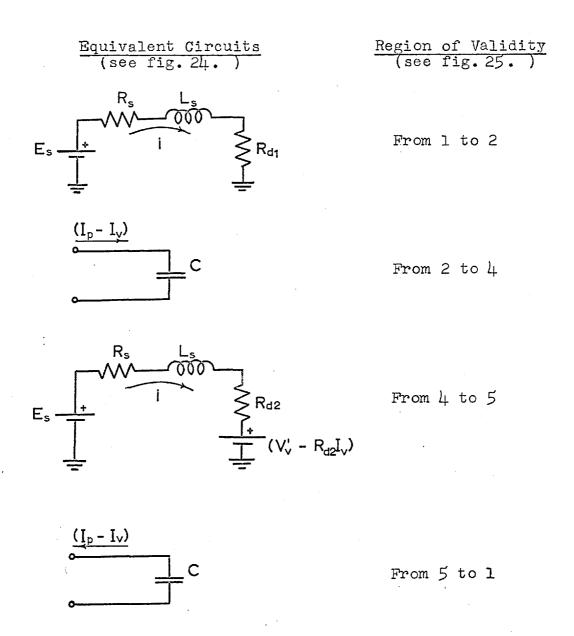

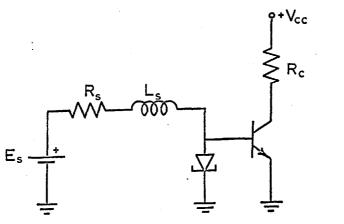

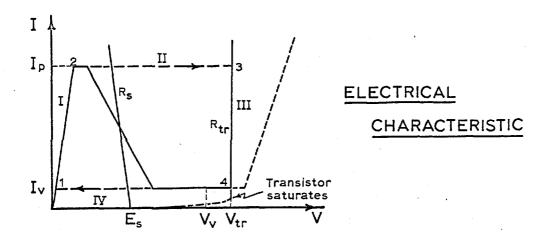

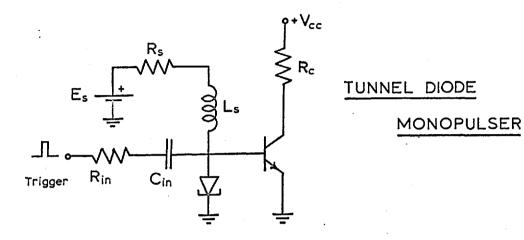

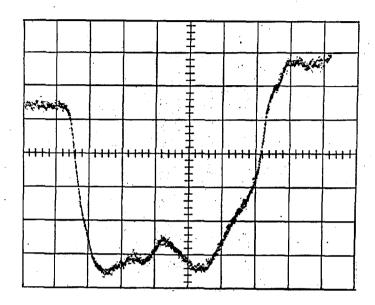

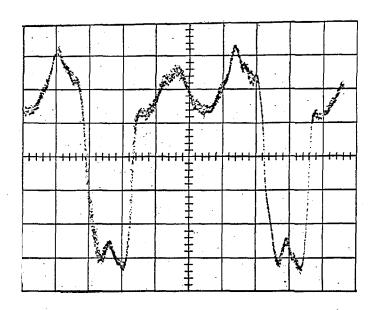

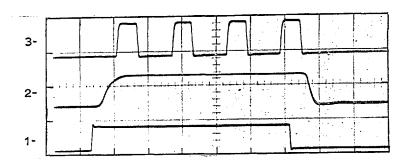

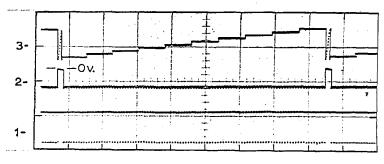

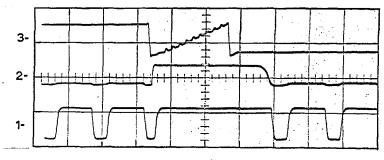

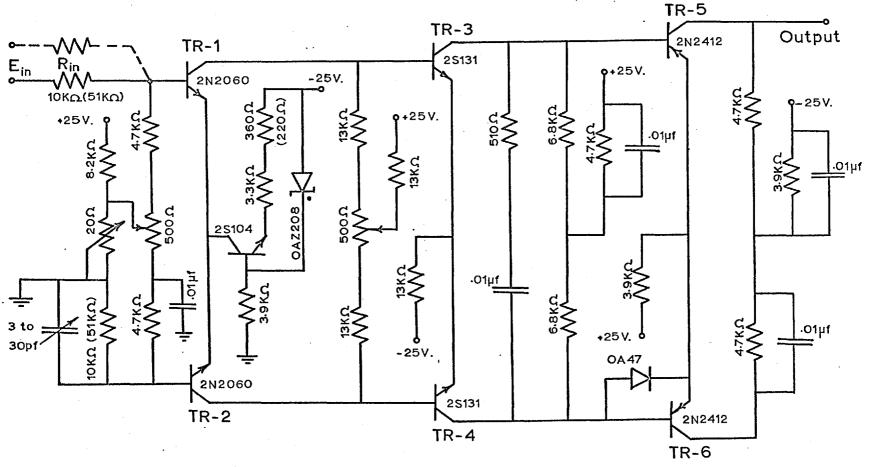

In a chain containing more than two tunnel diodes, the situation becomes even worse. At any moment, the diodes not being switched contribute an additional resistance in series with the external R and if two units trigger at the same time, the drive being no longer of the low impedance type, both diodes reach their high voltage state.