Imperial College London Department of Electrical and Electronic Engineering

## Formal Verification of High-Level Synthesis

Yann Herklotz Grave

April 2024

Supervised by John Wickerson

Submitted in part fulfilment of the requirements for the degree of Doctor of Philosophy in Electrical and Electronic Engineering of Imperial College London and the Diploma of Imperial College London.

Supervisor:Dr John WickersonInternal Examiner:Prof George ConstantinidesExternal Examiner:Prof Xavier Leroy

Copyright © 2024 Yann Herklotz Grave.

The copyright of this thesis rests with the author. Unless otherwise indicated, its contents are licensed under a Creative Commons Attribution-NonCommercial 4.0 International Licence (CC BY-NC).

Under this licence, you may copy and redistribute the material in any medium or format. You may also create and distribute modified versions of the work. This is on the condition that: you credit the author and do not use it, or any derivative works, for a commercial purpose.

When reusing or sharing this work, ensure you make the licence terms clear to others by naming the licence and linking to the licence text. Where a work has been adapted, you should indicate that the work has been changed and describe those changes.

Please seek permission from the copyright holder for uses of this work that are not included in this licence or permitted under UK Copyright Law.

## **Statement of Originality**

I, Yann Herklotz Grave, declare that the work presented in this thesis is my own, and that any other work has been appropriately referenced.

### Abstract

Latency, throughput, and energy efficiency are becoming increasingly important, leading to custom hardware accelerators being designed for numerous applications instead of using less efficient general processors. Alas, designing these accelerators can be an error-prone process, especially when using hardware description languages (HDLs) such as Verilog, which operate at the register transfer level.

An attractive alternative is *high-level synthesis (HLS)*, where hardware designs are automatically compiled from software written in a high-level language like C. This way, hardware designers can benefit from mature software development tools. HLS tools promise designs with comparable performance and energy-efficiency to those hand-written in HDLs, reducing the time needed to design new accelerators. Reasoning about behaviour at a higher level should also make the process less error-prone. Unfortunately, HLS tools are unreliable; Vivado HLS produces incorrect designs in 1.2% of randomly generated C programs, undermining testing performed at the higher level of abstraction.

In an attempt to improve this situation, I propose a formally verified HLS tool called Vericert, providing a computer-checked proof that ensures it only generates hardware designs that behave like the input software program. Vericert extends CompCert, an established formally verified C Compiler, with a hardware back-end.

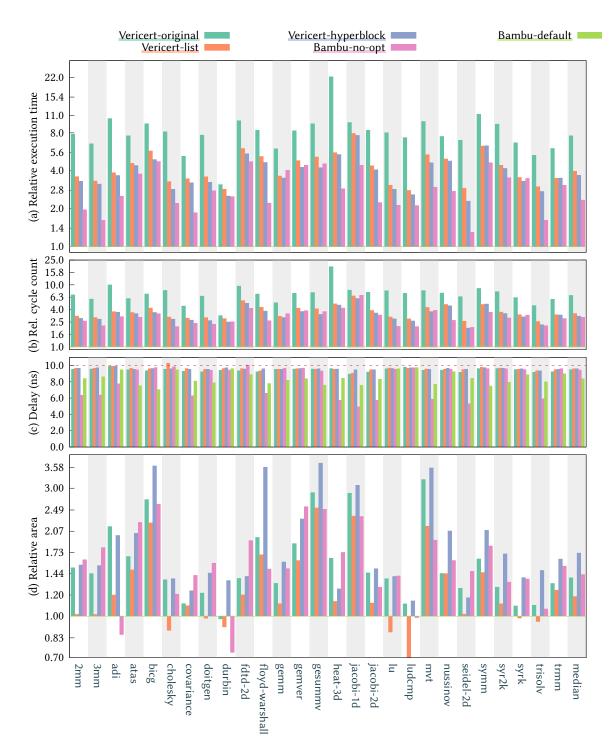

One expects a verified tool to produce significantly worse hardware than existing optimising HLS tools, as each transformation has to be simple enough to be proven correct. Indeed, an initial version of Vericert was up to  $8 \times$  slower than a state-of-the-art HLS tool called Bambu. However, by verifying *hyperblock scheduling* in Vericert, a transformation which parallelises instructions in regions of code without loops, hardware produced by Vericert becomes only  $1.6 \times$  slower than Bambu without optimisations and  $3.6 \times$  slower than optimised Bambu. This is encouraging, showing that a verified HLS tool is comparable with an existing HLS tool, while being guaranteed to generate correct hardware designs.

## Acknowledgements

First and foremost I would like to thank my supervisor John Wickerson for his continued guidance and patience throughout the PhD. He has allowed me to explore freely, and was generous with his time whenever I needed help or advice. He has also always encouraged me to present my work in diverse venues, leading to many interesting discussions and connections. His wonderful ability to understand technical descriptions and expose the core contribution clearly and creatively has been invaluable, and has taught me how to communicate my ideas clearly. I would also like to thank my examiners George Constantinides and Xavier Leroy for the many thought-provoking discussions and helpful suggestions that lead to a much clearer dissertation and many new ideas to explore.

Next, I would like to thank my colleagues in the Circuits and Systems group for many interesting discussions and creating an enjoyable atmosphere in the lab: Jianyi for a joint journey through the PhD, Nadesh for introducing me to high-level synthesis and helping me run them in the first place, Aditya and Diederik for many discussions about compilers over drinks, my coauthors James Pollard, Zewei and Michalis for all their help on our publications, and Kate, Roy, Divyansh and Mariano for being amazing flatmates. Finally, I would like to thank Alex Dalton, Alex Montgomerie-Corcoran, Ben Biggs, Ben Chua, Cheng, Dan, Erwei, Guoxuan, Ian, Marta, Quentin, Sina and Zhewen for many insightful discussions and advice, as well as help working with FPGAs and hardware tools.

I also gratefully acknowledge the Cyber Security Centre (NCSC) for funding this PhD through the Research Institute on Verified Trustworthy Software Systems (VeTSS).

I have also had the great pleasure to be able to work in the Celtique group at Irisa in Rennes as a visiting researcher over the summer in 2022. I would like to thank Sandrine Blazy and Delphine Demange for their deep insights into the CompCert compiler and for countless interesting discussions on different verification techniques and how these could be integrated into CompCert.

I would also like to sincerely thank Sandro Stucki and Bor-Yuh Evan Chang for their invaluable guidance during my internship at Amazon Prime Video, as well as my colleagues

#### Acknowledgements

during my time there with whom I had enlightening discussions with: Daniel, Francesco, Franco, Horia, Ilina, Ioannis, Pauline, Philipp, Sarek, Stefan, and Vlad. Additionally, I would like to thank Stefan Zetzsche for all his help understanding Dafny.

I would also like to thank my family and friends for their invaluable support and understanding during the PhD. Thank you to my father and especially my mother for their continued support, helping me get through stressful times.

Finally, I would like to thank my partner and best friend Nikita for her continued support.

| Copyright Assignment |                            |                                                  |      |  |  |  |

|----------------------|----------------------------|--------------------------------------------------|------|--|--|--|

| St                   | Statement of Originality 3 |                                                  |      |  |  |  |

| Al                   | bstrad                     | t                                                | 5    |  |  |  |

| A                    | c <mark>kno</mark> v       | ledgements                                       | 7    |  |  |  |

| Al                   | bbrev                      | ations                                           | 17   |  |  |  |

| 1                    | Intr                       | duction                                          | 19   |  |  |  |

|                      | 1.1                        | Research Contributions                           | . 21 |  |  |  |

|                      | 1.2                        | Dissertation Outline                             | . 24 |  |  |  |

|                      | 1.3                        | Publications                                     | . 24 |  |  |  |

| 2                    | Bac                        | ground                                           | 27   |  |  |  |

|                      | 2.1                        | Field Programmable Gate Arrays                   | . 27 |  |  |  |

|                      | 2.2                        | An Introduction to Verilog                       | . 29 |  |  |  |

|                      | 2.3                        | High-Level Synthesis                             | . 29 |  |  |  |

|                      |                            | 2.3.1 Data structures for intermediate languages | . 33 |  |  |  |

|                      |                            | 2.3.2 Grouping instructions into blocks          | . 36 |  |  |  |

|                      | 2.4                        | Scheduling                                       | . 39 |  |  |  |

|                      |                            | 2.4.1 Static scheduling                          | . 39 |  |  |  |

|                      |                            | 2.4.2 Dynamic scheduling                         | . 41 |  |  |  |

|                      | 2.5                        | Verification                                     | . 42 |  |  |  |

|                      |                            | 2.5.1 Automatic theorem provers                  | . 42 |  |  |  |

|                      |                            | 2.5.2 Interactive theorem provers                | . 44 |  |  |  |

|                      | 2.6                        | Verification of High-Level Synthesis             | . 45 |  |  |  |

|                      |                            | 2.6.1 Unmechanised verification of HLS           | . 46 |  |  |  |

|   |                                              | 2.6.2                                   | Mechanised compiler proofs in high-level hardware design    | 50  |  |  |  |

|---|----------------------------------------------|-----------------------------------------|-------------------------------------------------------------|-----|--|--|--|

|   |                                              | 2.6.3                                   | HLS formalised in Isabelle                                  | 51  |  |  |  |

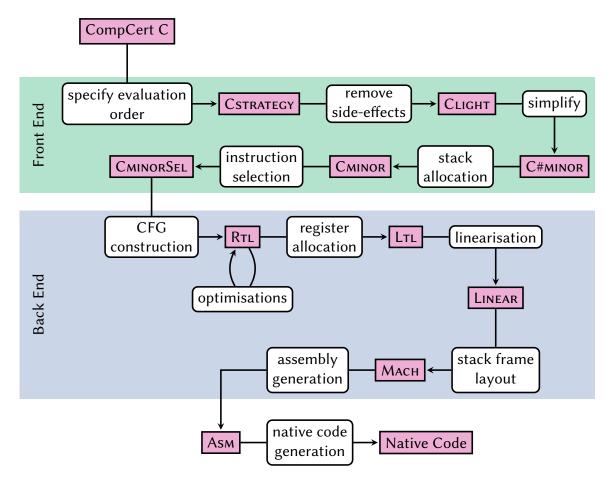

|   | 2.7                                          | Comp                                    | Cert                                                        | 52  |  |  |  |

|   |                                              | 2.7.1                                   | CompCert correctness theorem                                | 54  |  |  |  |

|   |                                              | 2.7.2                                   | Instruction scheduling in CompCert                          | 57  |  |  |  |

|   |                                              | 2.7.3                                   | Trace scheduling                                            | 59  |  |  |  |

|   | 2.8                                          | Summ                                    | ary                                                         | 62  |  |  |  |

| 3 | Intr                                         | oductio                                 | on to Vericert                                              | 63  |  |  |  |

|   | 3.1                                          | Unreli                                  | ability of High-Level Synthesis                             | 63  |  |  |  |

|   | 3.2                                          | Main                                    | Design Decisions of Vericert                                | 65  |  |  |  |

|   | 3.3                                          | Transl                                  | lating C to Verilog by Example                              | 69  |  |  |  |

|   |                                              | 3.3.1                                   | Translating C to RTL                                        | 70  |  |  |  |

|   |                                              | 3.3.2                                   | Scheduling RTL instructions                                 | 70  |  |  |  |

|   |                                              | 3.3.3                                   | Translating RTLPAR to HTL                                   | 72  |  |  |  |

|   |                                              | 3.3.4                                   | Translating HTL to Verilog                                  | 75  |  |  |  |

| 4 | Correctness Theorem and Verilog Semantics 72 |                                         |                                                             |     |  |  |  |

|   | 4.1                                          | Formu                                   | llating the Correctness Theorem                             | 77  |  |  |  |

|   | 4.2                                          | A For                                   | mal Semantics for Verilog                                   | 79  |  |  |  |

|   |                                              | 4.2.1                                   | Changes to the semantics                                    | 81  |  |  |  |

|   |                                              | 4.2.2                                   | Integrating the Verilog semantics into CompCert's model     | 83  |  |  |  |

|   |                                              | 4.2.3                                   | Memory model                                                | 86  |  |  |  |

|   |                                              | 4.2.4                                   | Deterministic Verilog semantics                             | 88  |  |  |  |

|   | 4.3                                          | Summ                                    | ary                                                         | 88  |  |  |  |

| 5 | Veri                                         | fied Hy                                 | yperblock Scheduling                                        | 89  |  |  |  |

|   | 5.1                                          | Overv                                   | iew                                                         | 90  |  |  |  |

|   | 5.2                                          | New I                                   | ntermediate Languages                                       | 93  |  |  |  |

|   | 5.3                                          | Verified If-Conversion                  |                                                             |     |  |  |  |

|   | 5.4                                          | Implementing Hyperblock Scheduling    9 |                                                             |     |  |  |  |

|   | 5.5                                          | Validation of Hyperblock Scheduling     |                                                             |     |  |  |  |

|   |                                              | 5.5.1                                   | First attempt: basic symbolic execution                     | 102 |  |  |  |

|   |                                              | 5.5.2                                   | Second attempt: using value summaries                       | 103 |  |  |  |

|   |                                              | 5.5.3                                   | Third attempt: using value summaries and final-state guards | 105 |  |  |  |

|             |      | 5.5.4                                                       | Handling overwritten expressions                          |  |  |  |

|-------------|------|-------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

|             |      | 5.5.5                                                       | Formalising the symbolic state and symbolic execution 107 |  |  |  |

|             |      | 5.5.6                                                       | Defining a Verified Scheduler                             |  |  |  |

|             | 5.6  | Provin                                                      | g the Validator Correct                                   |  |  |  |

|             |      | 5.6.1                                                       | A semantics for symbolic states                           |  |  |  |

|             |      | 5.6.2                                                       | Establishing the chain of simulations                     |  |  |  |

|             |      | 5.6.3                                                       | Managing complexity in the proof                          |  |  |  |

|             | 5.7  | Compa                                                       | arison Against Other Validated Schedulers                 |  |  |  |

|             |      |                                                             | ted three-valued Logic Using an SMT Solver                |  |  |  |

| 5.9 Summary |      |                                                             |                                                           |  |  |  |

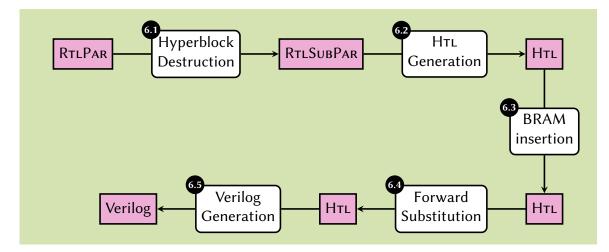

| 6           | Hare | dware                                                       | Generation 121                                            |  |  |  |

|             | 6.1  | Hyper                                                       | block Destruction                                         |  |  |  |

|             |      | 6.1.1                                                       | Proof of hyperblock destruction                           |  |  |  |

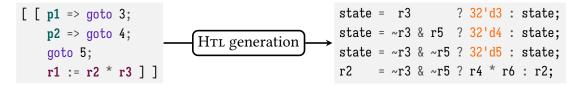

|             | 6.2  | Htl G                                                       | eneration                                                 |  |  |  |

|             |      | 6.2.1                                                       | HTL structure and semantics                               |  |  |  |

|             |      | 6.2.2                                                       | HTL generation algorithm 125                              |  |  |  |

|             |      | 6.2.3                                                       | HTL generation correctness proof                          |  |  |  |

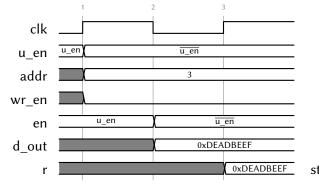

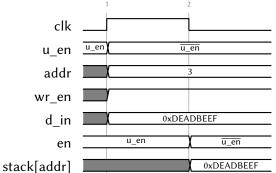

|             | 6.3  | BRAM                                                        | insertion                                                 |  |  |  |

|             |      | 6.3.1                                                       | BRAM model semantics                                      |  |  |  |

|             |      | 6.3.2                                                       | BRAM insertion and correctness proof                      |  |  |  |

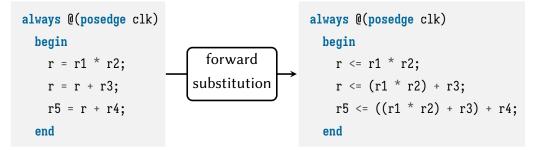

|             | 6.4  | Registe                                                     | er Forward Substitution                                   |  |  |  |

|             |      | 6.4.1                                                       | Forward substitution correctness proof                    |  |  |  |

|             | 6.5  | Verilog                                                     | g Generation                                              |  |  |  |

|             |      | 6.5.1                                                       | Forward simulation from HTL to Verilog                    |  |  |  |

|             | 6.6  | Summ                                                        | ary                                                       |  |  |  |

| 7           | Eval | aluation 147                                                |                                                           |  |  |  |

|             | 7.1  | Experi                                                      | mental Setup                                              |  |  |  |

|             | 7.2  | RQ1: I                                                      | s Vericert Competitive With Unverified Tools              |  |  |  |

|             | 7.3  | RQ2: A                                                      | Area and Delay Improvements of Vericert                   |  |  |  |

|             | 7.4  | RQ3: Hyperblock Scheduling Compared to Naïve Scheduling 151 |                                                           |  |  |  |

|             | 7.5  | RQ4: 0                                                      | Compilation Times of Vericert                             |  |  |  |

|             | 7.6  | RQ5: E                                                      | Effectiveness of Vericert's Correctness Theorem           |  |  |  |

|             | 7.7  | Summa                                                       | ary                                                       |  |  |  |

| 8 | Con | clusior | 1                                     | 155 |

|---|-----|---------|---------------------------------------|-----|

|   | 8.1 | Coq m   | echanisation                          | 155 |

|   | 8.2 | Limita  | tions and Future Work                 | 156 |

|   |     | 8.2.1   | Limitations to the generated hardware | 156 |

|   |     | 8.2.2   | Limitations on the software input     | 158 |

|   |     | 8.2.3   | The Future of Vericert                | 159 |

|   | 8.3 | Summ    | ary                                   | 159 |

|   |     |         |                                       |     |

#### Bibliography

## **List of Figures**

| 2.1  | FPGA layout showing a place and routed design                             | 28 |

|------|---------------------------------------------------------------------------|----|

| 2.2  | A simple Verilog implementation of a finite-state machine                 | 30 |

| 2.3  | Comparison of lists, control-flow graphs, data-flow graphs and control-   |    |

|      | and data-flow graphs.                                                     | 34 |

| 2.4  | Comparison of basic blocks, superblocks and hyperblocks.                  | 36 |

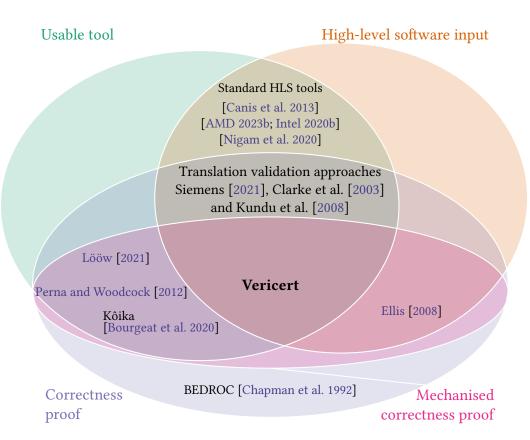

| 2.5  | Summary of related work.                                                  | 47 |

| 2.6  | CompCert diagram describing the intermediate languages                    | 53 |

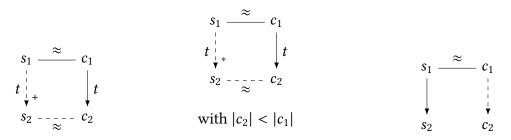

| 2.7  | Examples of simulation diagrams that make up the backward simulation      | 56 |

| 2.8  | Examples of forward simulation diagrams.                                  | 57 |

| 2.9  | Example of symbolic execution adapted from Tristan and Leroy              | 58 |

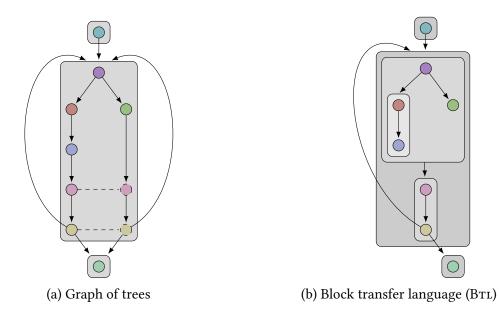

| 2.10 | Comparison of the graph of trees structure and BTL                        | 60 |

| 3.1  | Miscompilation bug in Xilinx Vivado HLS v2018.3, v2019.1 and v2019.2      | 64 |

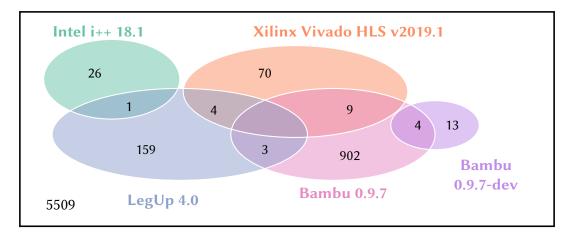

| 3.2  | The number of failures per tool.                                          | 65 |

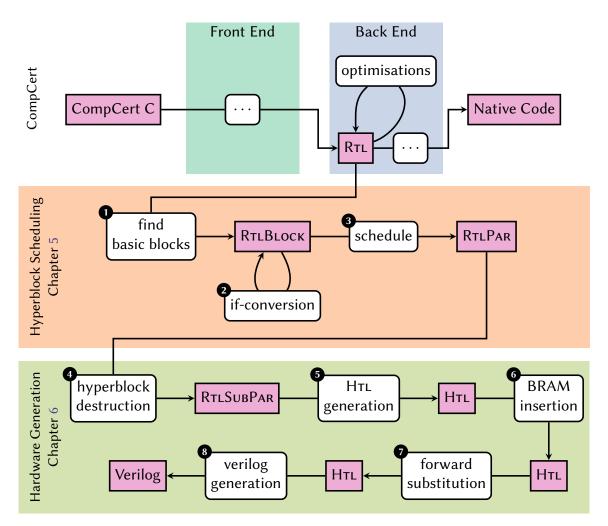

| 3.3  | Vericert as a Verilog back end to CompCert.                               | 67 |

| 3.4  | Translating a simple program from C to RTL                                | 70 |

| 3.5  | Scheduling a simple program from RTLBLOCK to RTLPAR                       | 71 |

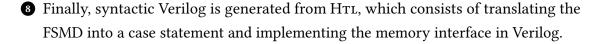

| 3.6  | Diagram of the FSMD for the example.                                      | 73 |

| 3.7  | Verilog implementation of the RTL code.                                   | 74 |

| 4.1  | Top-level small-step semantics for Verilog modules in CompCert's compu-   |    |

|      | tational framework.                                                       | 84 |

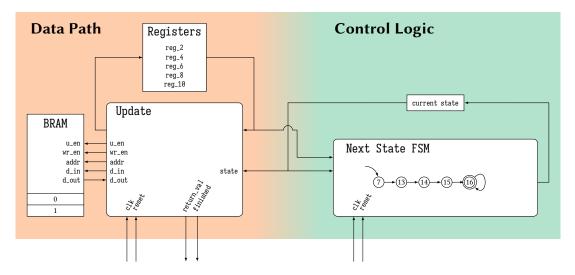

| 4.2  | Change in the memory model during the translation of RTL into HTL         | 87 |

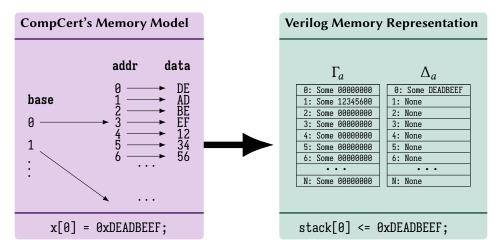

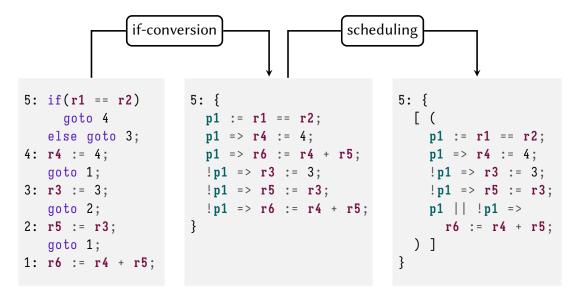

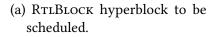

| 5.1  | New passes and intermediate languages introduced in this work             | 91 |

| 5.2  | Example of an if-conversion transformation followed by a scheduling op-   |    |

|      | eration.                                                                  | 92 |

| 5.3  | Syntax of RTLBLOCK and RTLPAR, with our hyperblock additions highlighted. | 94 |

| 5.4  | Semantics of RTLBLOCK and RTLPAR hyperblocks.                             | 96 |

| List | of | Fig | ures |

|------|----|-----|------|

|      |    |     |      |

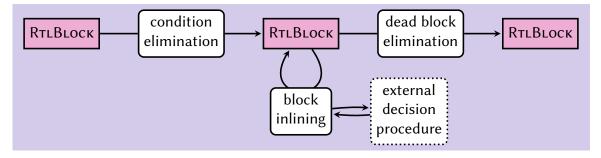

| 5.5  | Details of the if-conversion pass, showing the three different stages of the |

|------|------------------------------------------------------------------------------|

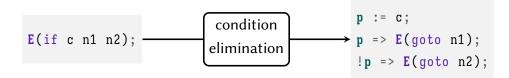

|      | transformation                                                               |

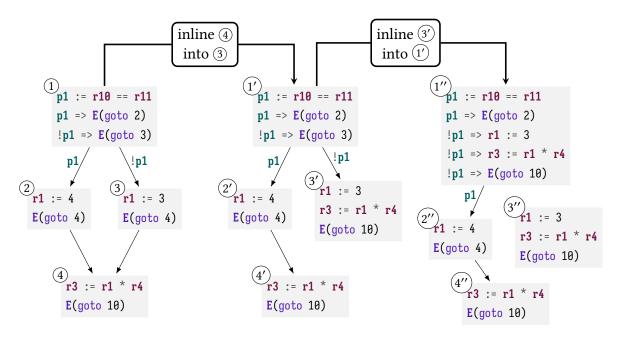

| 5.6  | An example showing two iterations of the block-inlining pass 97              |

| 5.7  | Example of scheduling a hyperblock                                           |

| 5.8  | An example schedule                                                          |

| 5.9  | Syntax of symbolic states                                                    |

| 5.10 | Symbolic execution of selected instructions                                  |

| 5.11 | Semantics of symbolic states                                                 |

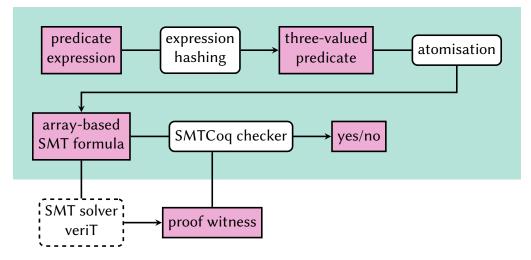

| 5.12 | Validation of predicate expressions using three-valued logic                 |

| 5.13 | Truth tables for three-valued logic operators                                |

| 5.14 | Evaluation of three-valued logic predicates                                  |

| 6.1  | Hardware generation transformation passes introduced to convert RTLPAR       |

|      | to Verilog                                                                   |

| 6.2  | Hyperblock destruction transformation splitting up the hyperblock into       |

|      | multiple locations                                                           |

| 6.3  | Syntax of HTL                                                                |

| 6.4  | Simple translation from an RTLSUBPAR block into an HTL block 126             |

| 6.5  | Describing the control flow translation from RTLSUBPAR to HTL 128            |

| 6.6  | Verilog implementation of the BRAM interface generated by Vericert 132       |

| 6.7  | Timing diagrams showing the execution of loads and stores over multiple      |

|      | clock cycles                                                                 |

| 6.8  | Specification for the memory implementation in HTL                           |

| 6.9  | Memory transformation specification                                          |

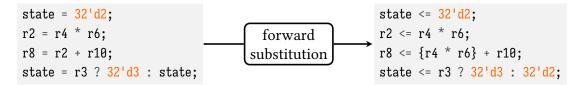

| 6.10 | Simple example of the forward substitution transformation                    |

| 6.11 | Simple forward substitution transformation with the runtime association      |

|      | maps                                                                         |

| 6.12 | Instantiation of BRAM specification with Verilog implementation 144          |

| 7.1  | Benchmark results compared to Bambu HLS and other Vericert versions 150      |

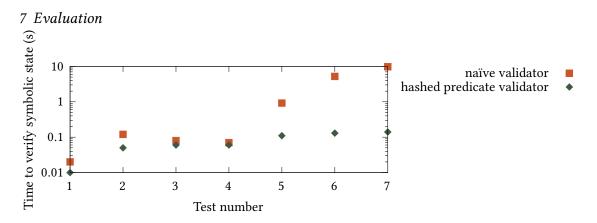

| 7.2  | Comparing the performance of predicate validators                            |

| 7.3  | Results of fuzzing Vericert using 155267 random C programs generated by      |

|      | Csmith                                                                       |

## **List of Tables**

| 5.1 | First attempt: basic symbolic execution                                    |

|-----|----------------------------------------------------------------------------|

| 5.2 | Second attempt: using value summaries                                      |

| 5.3 | Third attempt: using value summaries and final values in guards 106        |

| 8.1 | Statistics about the numbers of lines of code in the proof and implementa- |

|     | tion of Vericert, counted using coqwc                                      |

## Abbreviations

- ALAP as late as possible

- **ASAP** as soon as possible

#### ASIC application-specific integrated circuit

- Asм CompCert assembly language

- ASMBLOCK CompCert KVX assembly block language

- **AST** abstract syntax tree

- BRAM block random-access memory

- BTL block transfer language

- C#MINOR CompCert intermediate language

- **CDFG** control- and data-flow graph

- **CFG** control-flow graph

- CLIGHT CompCert intermediate language

- CMINOR CompCert intermediate language

- **CMINORSEL** CompCert intermediate language

- **CPU** central processing unit

- **DFG** data-flow graph

- **DRAM** dynamic random-access memory

- DSL domain-specific language

#### Abbreviations

- DSP digital signal processor

- **FPGA** field-programmable gate array

- FSM finite-state machine

- **FSMD** finite-state machine with data path

- GPU graphics processing unit

- HDL hardware description language

- **HLS** high-level synthesis

- **IP core** intellectual property core

- **IR** intermediate representation

- **LP** linear programming

- LSQ load-store queue

- LTL linear transfer language

- LUT look-up table

- **MACH** CompCert intermediate language

- **RTL** register transfer language

- **SAT** satisfiability

- **SDC** system of difference constraints

- **SMT** satisfiability modulo theories

- **SSA** static single assignment

- VLIW very large instruction word

## Introduction

As latency, throughput, and energy efficiency are becoming increasingly important, we are seeing companies move towards designing their own application-specific hardware accelerators tailored to their workloads instead of relying on general-purpose central processing units (CPUs) or graphics processing units (GPUs). By specialising the hardware to the application, the hardware can be optimised further than general purpose processors, unlocking better performance while often using less power. Apple and Google, for example, are integrating machine learning accelerators into consumer hardware to allow models to run more efficiently than if they used the CPU or GPU [Apple 2022; Gupta 2023]. Machine learning is an example of an application that benefits greatly from having dedicated and specialised hardware accelerators designed for it [Reuther et al. 2020].

Alas, designing these accelerators can be a tedious and error-prone process. Hardware is normally designed using a hardware description language (HDL) such as Verilog or VHDL, which operates at the register-transfer level where the hardware needs to be described manually. As the complexity of hardware designs increases, designing hardware at this level becomes increasingly difficult, because the low-level description of the hardware makes it time-consuming and expensive to thoroughly test to ensure that it behaves as expected. An attractive alternative is high-level synthesis (HLS), where hardware designs are automatically compiled from software written in a high-level language like C. This way, hardware design can benefit from mature software development tools while working on the general functionality of the hardware, and then use a modern HLS tools such as LegUp [Canis et al. 2013], Vitis HLS [AMD 2023b], Intel i++ [Intel 2020a], Stratus HLS [Roane 2023] or Bambu HLS [Pilato and Ferrandi 2013] to produce the registertransfer level description. These HLS tools promise designs with comparable performance and energy-efficiency to those hand-written in an HDL [Gauthier and Wadood 2020; Homsirikamol and Gaj 2014; Pelcat et al. 2016]. This reduces the time needed to design new hardware accelerators and as the design is performed at a higher level, the process should also be less error-prone.

#### 1 Introduction

**Verifying the functionality of HLS designs** Compared to software, it is even more important to ensure that hardware functions as it is supposed to, because once the hardware has been taped-out into an application-specific integrated circuit (ASIC), it becomes impossible to properly fix the issue except through workarounds in software. This may come at a great cost in terms of energy usage and the performance of the system compared to fixing the issue in hardware itself [Bowen and Lupo 2020; Herzog et al. 2021]. These hardware faults can also often be exploited and can be hard to detect, even using state-of-the-art hardware verification methodologies [Dessouky et al. 2019], either because the correctness properties themselves can be hard to express, or because the state-space that needs to be explored by the tools is too large.

HLS should simplify the process of verifying the functionality of the hardware design. Verifying designs at the register-transfer level requires large engineering efforts because of the level of detail and the size of the design. Even testing such large designs can be problematic, because the size of the design often means one cannot simulate running the hardware for more than a few seconds. Instead, HLS moves the verification of the functionality of the design to a higher level, where less detail is exposed, making it possible for software tools to reason about the behaviour of the program instead. Although a recent survey by Lahti et al. [2019] describes that verification remains a time-consuming part of the design process even with the use of HLS, it finds that in general it still reduced the verification effort by half.

Unfortunately, there are reasons to doubt that HLS tools actually preserve the behaviour of the design, increasing the chance of there being exploitable hardware faults in the resulting accelerator, and making verification at the level of the high-level language less useful. Some of these reasons are general: HLS tools are large pieces of software, they perform a series of complex analyses and transformations, and the HDL output they produce has superficial syntactic similarities to a software language but a subtly different semantics. Other reasons are more specific: for instance, Vivado HLS has been shown to apply pipelining optimisations incorrectly<sup>1</sup> or to silently generate wrong code should the programmer stray outside the fragment of C that it supports.<sup>2,3</sup> Meanwhile, Lidbury et al. [2015] had to abandon their attempt to fuzz-test Altera's (now Intel's) OpenCL to hardware compiler since it 'either crashed or emitted an internal compiler error' on many

<sup>&</sup>lt;sup>1</sup>https://support.xilinx.com/s/question/0D52E00006jt7LfSAI/crtl-cosimulation-failed-caused-bypragma-hls-pipeline

<sup>&</sup>lt;sup>2</sup>https://support.xilinx.com/s/question/0D52E00006hpMZSSA2/pointer-synthesis-in-vivado-hls-v201 <sup>3</sup>https://docs.xilinx.com/r/en-US/ug1399-vitis-hls/Pointer-Limitations

of their test inputs. More recently, Herklotz et al. [2021a] fuzz-tested three commercial HLS tools using Csmith [Yang et al. 2011], and despite restricting the generated programs to the C fragment explicitly supported by all the tools, they still found that on average 2.5% of test-cases were compiled to designs that behaved incorrectly.

**Existing workarounds** Aware of the reliability shortcomings of HLS tools, hardware designers routinely check the generated hardware for functional correctness. This is commonly done by simulating the generated design against a large test-bench. But unless the test-bench covers all inputs exhaustively – which is often infeasible – there is a risk that bugs remain.

One alternative is to use *translation validation* [Pnueli et al. 1998] to prove equivalence between the input program and the output design. Translation validation has been successfully applied to several HLS optimisations [Banerjee et al. 2014; Chouksey and Karfa 2020; Chouksey et al. 2019; Karfa et al. 2006; Youngsik Kim et al. 2004]. Nevertheless, it is an expensive task, especially for large designs, and it must be repeated every time the compiler is invoked. For example, the translation validation for Catapult C [Siemens 2021] may require several rounds of expert 'adjustments' [Chauhan 2020, p. 3] to the input C program before validation succeeds. And even when it succeeds, translation validation does not provide watertight guarantees unless the validator itself has been mechanically proven correct [e.g. Tristan and Leroy 2008], which has not been the case in HLS tools to date.

My position is that none of the above workarounds are necessary if the HLS tool can simply be trusted to work correctly. This dissertation explores the implementation of a mechanically verified and optimising HLS tool built on the CompCert verified C compiler [Leroy 2006, 2009b; Leroy et al. 2016]. The main thesis of this dissertation is therefore the following:

**Thesis** A realistic and optimising high-level synthesis tool can be proven correct using an interactive theorem prover, guaranteeing the correctness of the hardware while also remaining practical and efficient.

#### **1.1 Research Contributions**

The main contributions of this dissertation is Vericert, a formally verified and optimising HLS tool. Vericert is written in the Coq theorem prover and comes with a machine-checked

#### 1 Introduction

proof that any output design it produces always has the same behaviour as the input C program. Vericert is automatically extracted to an OCaml program from Coq, which ensures that the object of the proof is the same as the implementation of the tool. Vericert is built by extending the CompCert verified C compiler with a new hardware-specific intermediate language and a Verilog back end. It supports many C constructs, including integer operations, function calls (which are all inlined), local arrays, structs, unions, and general control-flow statements, but currently excludes support for case statements, function pointers, recursive function calls, non-32-bit integers, floats, and global variables. The main research contributions of Vericert are the following:

- **Formulate overall correctness theorem with Verilog semantics** First, I state the correctness theorem of Vericert with respect to an existing semantics for Verilog due to Lööw and Myreen [2019]. The key challenge here involved integrating the hardware semantics within CompCert's model of computation and calling convention. This required specifying the external module interface used to interact with the final hardware produced by Vericert, for example specifying how the hardware can be reset, and how the final return value is extracted. Another challenge was extending the Verilog semantics with support for arrays, which is necessary to model hardware memory interfaces. Lastly, one particular difficulty that had to be overcome is proving that the function stack frame could be modelled by this finite Verilog array.

- **First mechanisation of general if-conversion** CompCert does already perform limited if-conversion, removing branches that contain a single instruction and replacing them with a conditional move instruction, because predicated instructions are unsupported. I describe the formalisation of a general if-conversion transformation in CompCert used to generate hyperblocks, which are sequences of possibly branching predicated instructions, where the only incoming edges are to the start of the block. The key challenge was to generalise the if-conversion pass so that any external unverified heuristic could be used to inline blocks, while keeping the correctness proof conceptually simple. It is also flexible enough to allow for light loop transformations like loop unrolling and loop peeling.

- **Formal verification of hyperblock scheduling** Next, I present a verified implementation of hyperblock scheduling, a critical optimisation for any HLS tool, taking advantage of the parallel nature of the hardware that is generated. I implement and validate the system of difference constraints (SDC) scheduling algorithm [Cong and

Zhang 2006], which is the base of the scheduling algorithm used by most HLS tools. Prior work verifying scheduling algorithms in CompCert [Six et al. 2022; Tristan and Leroy 2008] either were not general enough, being unable to schedule two branches of an if-statement together, or were inefficient because of unnecessary duplication when checking the correctness of the schedule. Instead, the key insight for this contribution is that predicates can be used to share otherwise duplicate expressions along different paths through the program.

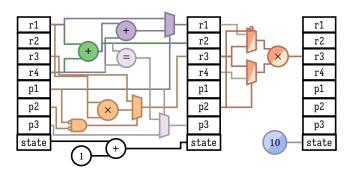

- **SAT and SMT solvers for translation validation in CompCert** I also present a novel use of a satisfiability (SAT) solver and a three-valued logic solver, implemented using an satisfiability modulo theories (SMT) solver, during translation validation to reason about the equivalence of functions before and after the scheduling transformations. The key challenge here is integrating an existing SMT proof checker, meant for assisting with interactive Coq proofs, and using it as a checker that can be used by the compiler at runtime to check that, for example, a three-valued predicate always holds. This can be used as a general validator for any transformation pass where the correctness depends on dynamically generated properties expressible in three-valued logic that need to be checked.

- **Evaluation of Vericert on PolyBench/C** Finally, I evaluate different versions of Vericert against the state-of-the-art open source and unverified HLS tool Bambu HLS [Pilato and Ferrandi 2013] on a standard C benchmark suite called PolyBench/C. One might expect a fully verified tool to perform significantly worse than a more optimised, unverified tool, however, I show that Vericert produces designs that have around the same cycle count as Bambu without optimisations, with a slightly worse maximum clock speed, leading to an overall execution speed of around 1.6× that of Bambu designs. However, when comparing against optimised Bambu, Vericert is 3.6× slower, which can be explained by the extensive loop optimisations present in Bambu.

**Companion material** Vericert is fully open source and available on GitHub at:

#### https://github.com/ymherklotz/vericert

A snapshot of the Vericert development is also available in a Zenodo repository [Herklotz et al. 2024].

#### **1.2 Dissertation Outline**

This dissertation is organised into the following chapters.

- **Chapter 2** provides background for the rest of the dissertation and also discusses related work around verification of high-level synthesis.

- **Chapter 3** introduces Vericert itself, giving an overview of how it is structured, as well as what kind of transformations are performed. Design choices made during the development of Vericert are also described and compared against other possible approaches.

- **Chapter** 4 then describes the Verilog semantics and the final correctness theorem of Vericert, which covers the main trusted computing base.

- **Chapter 5** then describes the front end of Vericert, which hooks into the middle end of CompCert. This chapter describes the implementation of hyperblock scheduling.

- **Chapter 6** then describes how the hyperblocks optimised by the scheduling algorithm are then turned into a hardware design in Verilog.

- **Chapter 7** evaluates different versions of Vericert in a number of ways on certain metrics comparing it against Bambu.

- **Chapter 8** finally gives a description of the limitations of Vericert as well as a discussion of the formalisation. In addition to that, many possible future directions are discussed.

#### **1.3 Publications**

The research in this dissertation has also been presented in the following three publications.

**FCCM 2021** This first paper evaluates the reliability of HLS tools and motivates the need for a more reliable HLS tool, as well as a more robust verification flow for HLS designs. This paper is described in section 3.1.

**Yann Herklotz**, Zewei Du, Nadesh Ramanathan and John Wickerson. 2021a. 'An Empirical Study of the Reliability of High-Level Synthesis Tools'. In: *2021 IEEE 29th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM)*, 219–223. DOI: 10.1109/FCCM51124.2021.00034.

**OOPSLA 2021** Next, we introduce Vericert and describe an initial translation from C to Verilog using CompCert, without optimisations. This article is the basis for the dissertation, making up parts of chapters 3, 4 and 6.

Yann Herklotz, James D. Pollard, Nadesh Ramanathan and John Wickerson. Oct. 2021b. 'Formal Verification of High-Level Synthesis'. *Proceedings of the ACM on Programming Languages*, 5, OOPSLA, (Oct. 2021). DOI: 10.1145/3485494.

**PLDI 2024** Finally, we describe a critical optimisation in the HLS flow called hyperblock scheduling. This article underpins chapter 5.

Yann Herklotz and John Wickerson. June 2024. 'Hyperblock Scheduling for Verified High-Level Synthesis'. *Proceedings of the ACM on Programming Languages*, 8, PLDI, Article 225, (June 2024), 25 pages. DOI: 10.1145/3656455.

The following publications did not directly contribute to the dissertation.

**FPGA 2020** This paper describes bugs that were found in hardware synthesis tools by generating random, deterministic hardware designs.

Yann Herklotz and John Wickerson. 2020. 'Finding and Understanding Bugs in FPGA Synthesis Tools'. In: *ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA)*. Seaside, CA, USA. ISBN: 978-1-4503-7099-8. DOI: 10.1145/3373087.3375310.

**FCCM 2022** This short paper describes an implementation of function calls in Vericert allowing function bodies to be shared between calls.

Michalis Pardalos, **Yann Herklotz** and John Wickerson. 2022a. 'Resource Sharing for Verified High-Level Synthesis'. In: 2022 IEEE 30th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 1–6. DOI: 10.1109 /FCCM53951.2022.9786208.

**CPP 2023** Finally, this paper described an implementation of a control-flow based semantics for gated-SSA in CompCertSSA, a first step towards a pure data-flow intermediate language in CompCert.

Yann Herklotz, Delphine Demange and Sandrine Blazy. 2023. 'Mechanised Semantics for Gated Static Single Assignment'. In: *Proceedings of the 12th ACM SIGPLAN International Conference on Certified Programs and Proofs* (CPP 2023). Association

#### 1 Introduction

for Computing Machinery, Boston, MA, USA, 182–196. ISBN: 9798400700262. DOI: 10.1145/3573105.3575681.

# Background 2

This chapter briefly describes field-programmable gate arrays (FPGAs) followed by introducing high-level synthesis (HLS) and the current state-of-the-art optimisations used by HLS tools, focusing in particular on static scheduling. Next, common testing and verification workflows for HLS are also described. Finally, an overview of CompCert is given, on which Vericert is built.

#### 2.1 Field Programmable Gate Arrays

This section introduces field-programmable gate arrays (FPGAs), which is assumed to be the final target for the hardware produced by Vericert, as well as the HLS tools that Vericert is directly compared against.

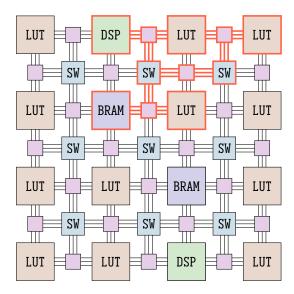

FPGAs are programmable hardware chips that can be used to implement and run custom hardware without having to tape-out an ASIC, which may take years of development time. FPGAs instead provide a platform to test custom hardware quickly without these long turnaround times, and can be reprogrammed at will in case the hardware ever needs to change. Because they still allow for reprogrammability, they can never be as efficient as an equivalent ASIC design, however, for many applications having the chance to reprogram the hardware is an advantage. In addition to that, an FPGA will still generally be more efficient and more performant than running the same workload on a general-purpose processor. FPGAs comprise the following four main components [Boutros and Betz 2021], which are also shown in figure 2.1.

**Look-up table (LUT)** A LUT can implement any kind of logic with a set number of inputs and an output. On an FPGA, LUTs are often grouped into larger programmable logic units called *slices* that can handle multiple inputs and outputs. LUTs are also normally paired with an optional register at the output so that they can also be used as a memory.

#### 2 Background

- **Figure 2.1:** FPGA layout, showing an example of a design that is placed and routed on the FPGA highlighted in red. The beige blocks correspond to LUTs, followed by green blocks being DSPs and purple blocks being BRAMs. The programmable interconnects are made up of connection blocks and switches shown in pink and blue respectively.

- **Programmable interconnect** The LUTs are connected using programmable interconnects, so that these arbitrary logical units can also be connected in arbitrary ways, making it possible to implement any kind of hardware design.

- **Block random-access memory (BRAM)** Instead of relying on implementing memories to store a large amount of data using LUTs, there is often BRAM on the FPGA, which provides efficient storage for data.

- **Digital signal processor (DSP)** Finally, FPGAs also often contain DSPs, which can be used to implement common arithmetic functions efficiently, that may otherwise take up a lot of space if implemented using LUTs. Some common arithmetic functions that are often implemented using DSPs include integer multipliers and multiply-accumulate operations.

The standard process to translate a hardware design from an HDL, such as Verilog or VHDL, to be placed onto an FPGA is to first *synthesise* the hardware design, which generates a lower level netlist description of the hardware in terms of the resources that are available on the FPGA. Next, the netlist is place-and-routed on the FPGA, which assigns a physical location to each resource and programs the interconnects so that all the components are connected properly. This low-level description of the hardware is then turned into a bit

stream that will program all the individual resources on the FPGA. The result can be seen in figure 2.1 by looking at the highlighted paths in red, as the place-and-route process placed logical functions into LUTs and connected them together making use of a BRAM and a DSP.

#### 2.2 An Introduction to Verilog

This section will introduce Verilog for readers who may not be familiar with the language, concentrating on the features that are used in the output of Vericert. Verilog [IEEE 2006] is an HDL and is used to design hardware ranging from complete CPUs that are eventually produced as integrated circuits, to small application-specific accelerators that are placed on FPGAs. Verilog is a popular language because it allows for fine-grained control over the hardware, and also provides high-level constructs to simplify development.

Verilog behaves quite differently to standard software programming languages due to it having to express the parallel nature of hardware. The basic construct to achieve this is the always-block, which is a collection of assignments that are executed every time some event occurs. In the case of Vericert, this event is either a positive (rising) or a negative (falling) clock edge. All always-blocks triggering on the same event are executed in parallel. Always-blocks can also express control flow using if-statements and case-statements.

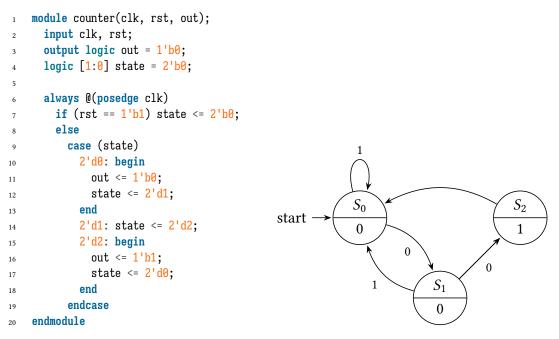

A simple state machine can be implemented as shown in figure 2.2. This state machine implements a pulse generator that generates a pulse every three clock cycles. At every positive edge of the clock (clk), the always-blocks will trigger. First, the rst input is checked, and if it is high the state variable is set back to 2'b0. Otherwise, the state machine is implemented by checking the current value of state and defining the next state, including setting a value for the output out. No explicit value is set for the output in state 2'd1, however, as out is a register, it will keep the same value from the last state, which in this case is 1'b0. Assignments are performed using nonblocking assignment (<=), which assigns registers simultaneously at the end of each clock cycle. This state machine has the same general structure as the state machines discussed in this dissertation.

#### 2.3 High-Level Synthesis

High-level synthesis is the transformation of software directly into hardware. There are many different types of HLS, which can vary in terms of the languages they accept or the

#### 2 Background

**Figure 2.2:** A simple pulse generator implemented using a state machine in Verilog, with its diagrammatic representation on the right. The only input to the state machine is the reset rst, and the output in each state is represented by the lower half of the nodes in the finite-state machine diagram.

devices that are targeted, however, they often share similar steps in how the translation is performed, as they all go from a higher level, behavioural description of the algorithm to a timed hardware description. In this dissertation, I will assume that I am targeting FPGAs instead of ASICs, which means there are often different constraints in terms of available resources, as well as clock frequency.

The main steps performed in the translation of an HLS tool is the following [Canis et al. 2013; Coussy et al. 2009]:

**Compilation of input language** First, the program or specification written in the input language to the HLS tool is compiled into an intermediate language that is more suitable to be transformed by optimisations. The input language for most traditional HLS tools is a restricted version of C or C++, however, HLS tools such as Google XLS [Google 2024] can use a domain-specific language (DSL) based on communicating sequential processes [Hoare 1978] as an input specification as well. There are also HLS tools based on OpenCL [Intel 2020b] or Matlab through the Simulink block diagram language [Constantinides et al. 2001; Ou and Prasanna 2005]. This specification is then turned into some intermediate language that is easier to

manipulate through optimisations and transformations to hardware. This includes intermediate languages such as the LLVM intermediate representation (IR) [Lattner and Adve 2004], MLIR [Lattner et al. 2021] or a custom representation of the code. The structure of these intermediate languages is further discussed in section 2.3.2.

- Hardware resource allocation Depending on if the hardware target is a specific FPGA or an ASIC built on a specific technology library, the HLS tool will have to allocate resources differently. For example, on FPGAs there are only a limited number of LUTs, DSPs and BRAMs available. The HLS tool therefore often decides ahead of time which resources the program will need based on the operations that are present in the program. A few resources are often assumed to be infinite to simplify the resource allocation, examples being registers, which are normally cheap especially on FPGAs, or simple logic circuits that are cheap enough to be duplicated such as integer adders or multiplexers. Other circuits may require more resources in which case it would make sense to only have a few instantiations of the circuit and share it as much as possible. Examples of these circuits could be integer division modules or floating point arithmetic units that will most likely not have dedicated hardware on the FPGA and would therefore have to be implemented in logic. These circuits also often have trade-offs between area, latency and throughput which should be considered, and will be important in the operation scheduling step. Finally, memory and multiplication units lie in the middle, where there are usually enough BRAMs or DSPs resources on the FPGA, but they might introduce different challenges such leading to designs that are more difficult to place-and-route. In particular, if one uses too many of these resources, BRAMs and operations in the DSPs can be implemented using LUTs.

- **Operation scheduling** Once the available resources have been chosen, the operations in the intermediate representation need to be scheduled into a clock cycle based on these resource constraints, creating a timed representation of the program. The goal of the operation scheduling step is to maximise the instruction-level parallelism of the program while also honouring the various resource constraints that are imposed by the available resources. Scheduling is further described in section 2.4. As part of the scheduling step, operations are also often preliminarily bound to specific resources.

Resource binding After scheduling, each operation is assigned a concrete instantiation of

#### 2 Background

its resource. For example, an integer divide operation will be assigned to the integer divider resource, and if this resource is used by another divider in the design, the inputs and outputs will have to be multiplexed. The resource constrained scheduling step should have ensured that two divisions are not taking place in the same cycle, and that the result of the division will only be used when the divider resource has finished computing the result.

**Hardware description generation** Finally, the hardware description is generated from the code that was described in the intermediate language and from the states and resources that each operation and register was assigned to.

There are many examples of existing high-level synthesis tools, the most popular ones being Bambu HLS [Pilato and Ferrandi 2013], LegUp [Canis et al. 2013], Vitis HLS [AMD 2023b], Catapult C [Siemens 2021], Google XLS [Google 2024] and Intel's OpenCL SDK [Intel 2020b]. These HLS tools all accept general programming languages such as C/C++ or OpenCL.

The concept of HLS has also evolved over time, from describing the transformation of the behavioural level of Verilog and VHDL to the register-transfer level in the 90s, to describing the transformation of C code into hardware automatically like tools do today, as synthesis tools have accepted increasingly larger subsets of Verilog and VHDL that include the behavioural level. In addition to that, languages like Bluespec [Nikhil 2004] are also considered HLS tools despite having different goals to more traditional HLS tools accepting C code. Bluespec provides a high-level hardware specification language that can be used to define concurrently running rules. These are automatically scheduled by the Bluespec synthesis tool and converted to a traditional synthesisable HDL. Handel-C [Aubury et al. 1996; Bowen 1998] is in a similar position, being a C-like language for hardware development. Handel-C and its translation to hardware is based on occam [Page and Luk 1991]. It supports many C features such as assignments, if-statements, loops, pointers and functions. In addition to these constructs, Handel-C also supports explicit concurrency as well as sequential or parallel assignments, similar to blocking and nonblocking assignments in Verilog. It therefore was popular as a hardware/software co-design language as the language could naturally be used to define sequential code running in software and parallel code which could be synthesised to hardware. However, it is inherently timed, and the Handel-C synthesis tool does not usually perform automatic parallelisation of the code as is the case with HLS tools that accept C as input.

In this dissertation I will be focusing on the more traditional HLS conversion from software languages into hardware designs.

#### 2.3.1 Data structures for intermediate languages

This section describes how intermediate languages in the HLS flow are usually represented and the differences in these approaches. Next, in section 2.3.2 I will describe techniques used to group instructions into a contiguous blocks to simplify analyses and transformations of instructions within the blocks.

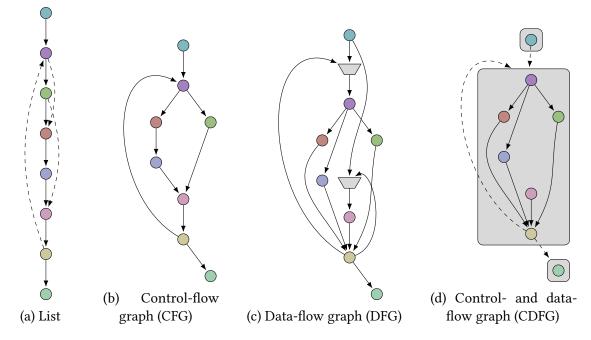

There are many ways to represent the code that makes up a function or a program. High-level languages that are written by the programmer are normally represented as an abstract syntax tree (AST) in the front end of the compiler, which is a tree representing the parsed source file. An AST is a good representation for high-level optimisations that may need information about the intent of the programmer. An example being a loop which is represented as a structured for-loop instead of unstructured goto statements. On the opposite end, the assembly that will run on the processor can simply be represented by a list of instructions. This simple representation of the program is useful because individual instructions can directly be stored contiguously in memory and are then loaded by the processor to be executed. However, storing instructions as a list means that much of the original structure of the program is lost, which makes program analysis and transformations more difficult. In between these two representations, there is often one or more intermediate languages that can be represented in a variety of ways, and are either used purely for analysis or also as an intermediate transformation step.

#### Lists

An example of a list representing code is shown abstractly in figure 2.3a. In the figure, the solid arrows between nodes show how the instructions are stored as a linked list, one instruction feeding to the next. However, programs may have loops in them, which cannot directly be expressed in the list representation, as each instruction can only have one successor. Instead, instructions that are represented as a list will have labels attached to them, and goto instructions can then jump to those labels. These jumps are represented using the dashed arrows in the figure. This is the simplest representation of the code as it is completely linear, however, analysing such a program will be more difficult because a lot of information, like information on many of the edges, is implicit in the representation.

**Figure 2.3:** Comparison of lists, control-flow graphs, data-flow graphs and control- and data-flow graphs.

Every analysis pass would have to reconstruct the control-flow edges between the nodes, which would have to be stored as a graph, so lists are likely only the final representation of the code.

#### **Control-flow graphs**

A control-flow graph (CFG) representation of the code is a graph instead of a list, and allows any instruction to be connected to any other instruction explicitly by a control-flow edge. This signifies that after executing an instruction, the execution will then move to one of the successors of the current node. This turns control-flow analysis into a graph problem [Allen 1970], simplifying many program analysis passes and making it more natural to traverse the program with graph search algorithms. Figure 2.3b shows how the list representation of the code would be represented as a CFG, where nodes can now have multiple outgoing or incoming edges. Because the edges represent control flow, only one edge will be taken at a time as the program executes.

#### **Data-flow graphs**

Alternatively, instead of reasoning about the control flow of the program, one might be interested in the data flow of the program. Many compiler optimisations, such as dead-code elimination or constant propagation, need to perform data-flow analyses on the CFG [Kam and Ullman 1976; Kildall 1973]. In addition to that, hardware circuits are naturally expressed using pure data flow as netlists can be viewed as data flow graphs, and even HDLs can be modelled by synchronous data flow programming languages [Halbwachs et al. 1991]. One could therefore represent the code as a pure data-flow graph (DFG) to help with data-flow optimisations as well as the translation to the final hardware. An example of a DFG that is be compatible with the CFG shown in figure 2.3b is represented in figure 2.3c, where arrows now represent data dependencies between nodes instead of control-flow dependencies.

As can be observed in the diagram, the edges between the nodes are very different to the edges in the CFG. Nodes in the CFG may not have needed to be in that particular order, because when two instructions are independent, one still needs to define an order between them. This is necessary due to the sequential nature of the CFG, instead, the DFG only represents the necessary edges between the nodes. Additionally, we have added two additional nodes to handle the back edges of the loop, which are also data dependencies. These nodes are represented by a trapezium in the DFG and act as loop headers to control the loop iterations when interpreting the graph as pure data flow. These additional nodes are needed because otherwise the data dependencies due to the back edges of the loop would conflict with the data dependency that actually enters the loop. We therefore need an additional node to turn the data dependencies into the correct control-dependencies, allowing data into the loop when the loop is not executing, but while it is executing the node should only allow data through from the back edge of the loop. The example shown in figure 2.3c is similar to the concepts of  $\mu$ -nodes in gated static single assignment form and the program dependence web [Campbell et al. 1993; Havlak 1994; Ottenstein et al. 1990; Tu and Padua 1995], which are intermediate languages that can be interpreted in a data flow oriented context.

#### Control- and data-flow graphs

As mentioned in the previous section, loops are especially problematic for pure DFGs. Instead, one can try to get the best of both CFGs and DFGs by creating a control- and data-flow graph (CDFG). In a CDFG, one instead has a CFG where each node is a DFG

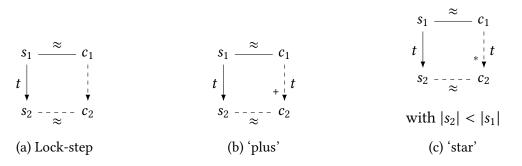

Figure 2.4: Comparison of basic blocks, superblocks and hyperblocks.

instead of just an instruction. The example is shown in figure 2.3d, where the dashed arrows are control dependencies between DFGs, and the solid lines are the data dependencies within the DFG. In this way, loops can be supported without having to introduce special nodes, leaving the loop back edge as a control dependency instead. DFGs can represent the sections of code without arbitrary external incoming control-flow edges using data dependencies, thereby being more flexible in how instructions are rearranged without the downside of having to introduce additional nodes.

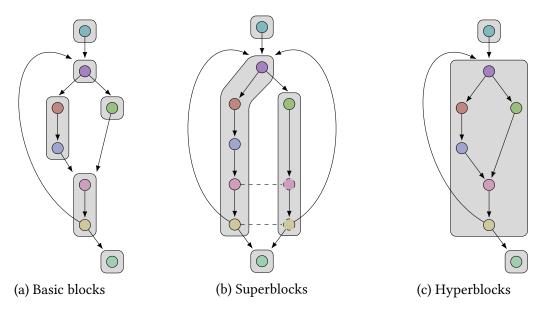

#### 2.3.2 Grouping instructions into blocks

This section describes the representation of intermediate languages that are often used within an HLS tool. In particular, we will base our intermediate language on a CFG, but will describe various ways to group blocks of instructions together and describe the advantages and drawbacks that they provide. Especially when considering compiler targets that allow for instruction-level parallelism, such as very large instruction word (VLIW) processors or custom hardware, it is important to schedule instructions so that the parallelism can be exploited. Various ways in which instructions can be grouped affect the size of the regions of instructions that can be scheduled together, and therefore affect the performance that can be achieved [Faraboschi et al. 2001], due to how much reordering the scheduler can perform.

## **Basic blocks**

To build a bit more structure in the CFG, it is useful to group non-branching instructions without any external incoming edges together forming basic blocks. An example of the CFG segmented into basic blocks is shown in figure 2.4a. Instructions within a basic block can then be represented as a list of instructions, as there cannot be any branches, and these lists of instructions can then be safely manipulated because there is a guarantee that there is no external incoming control flow in the middle of a basic block. For example, as long as two instructions in a basic block are independent, they can be safely reordered. This would have otherwise not been possible, because external incoming control flow may mean that reordering the instructions now leads to the unintended execution of an instruction. Basic blocks are used by IRs in real compilers such as Gimple in GCC or LLVM IR in clang as the default grouping of sequential instructions. They are a useful representation for various optimisations and transformations, because one does not have to inspect the control flow within basic blocks, and provides useful assumptions that can be made when performing intra-block transformations.

#### Superblocks

As figure 2.4a shows, one issue with basic blocks is that they are often quite small, therefore limiting the benefits that they can provide. One extension to basic blocks is superblocks [Hwu et al. 1993], shown in figure 2.4b. Superblocks extend the notion of basic blocks to contiguous regions without arbitrary incoming control-flow edges, but with multiple control-flow edges out of the superblock. The main benefit of this is that due to the extra flexibility of the multiple exits, superblocks can contain arbitrary linear traces through regions of non-looping code. The 'hot path' of the loop body can be grouped into a single superblock for example, which can then be heavily optimised. Various other important paths through the program can then also be grouped and optimised together. If different paths through the program reuse nodes from another path, as is shown with the pink and yellow nodes in figure 2.4b, then these nodes will have to be duplicated so that they can be included in a different path. As long as any optimisation takes into account the arbitrary exits that are possible in superblocks, the nodes within a superblock can be optimised independently from the rest of the code.

Unlike basic blocks, superblocks are not generally used to represent the IR itself, and they are mainly used to perform superblock scheduling. GCC, for example, implements a superblock scheduling optimisations, but does not use the superblock representation for other transformations passes.

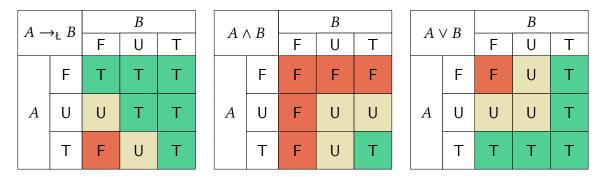

#### Hyperblocks

One downside of superblocks is that they cannot represent branching and joining control flow within a single block. For example, the block present in the CDFG shown in figure 2.3d could not be represented by a superblock. Hyperblocks are defined as basic blocks of predicated instructions with arbitrary outgoing edges leading to the next hyperblock [Mahlke et al. 1992]. They can represent arbitrary branching and joining control flow without arbitrary external incoming control-flow edges, and are therefore an extension to superblocks. This means that they could represent the CDFG shown in figure 2.3d, and an example of a hyperblock is shown in figure 2.4c, where in practice code within the hyperblock has been linearised using predicated instructions, instead of being represented as a graph. This leads to possibly more complex control flow than in both of the previous cases, however, it can be reasoned with using a SAT or SMT solver as the path information is part of the predicates.

Superblocks may require many blocks to be duplicated to group all the wanted instructions together. However, with predicated instructions, hyperblocks can represent joining control flow without having to duplicate any blocks because predicates can be selected so that the block is executed when either incoming edge is taken. Hyperblocks are not common in regular compilers, because predicated execution is rare in modern instruction set architectures. For example, Arm recently removed most conditionally executed instructions from their A64 ARMv8 ISA, because 'predicated execution of instructions does not offer sufficient benefit to justify its [...] implementation cost in advanced implementations' (Arm [2011, sec 3.2, p. 10]). However, hyperblock scheduling has been a popular intermediate language for HLS [Budiu and Goldstein 2002; Callahan and Wawrzynek 1998], as the flexibility of targeting hardware directly means that predication can be implemented efficiently.

On the other hand, GPUs often have sophisticated support for predication so that the same sequence of instructions (also called warps) can be executed on multiple different threads on the GPU, and so that diverging control flow can still be handled by a single, large warp. This can be achieved by designing predicates based on the thread identifier [Narasiman et al. 2011] and instructions operating on such predicates can be found in the SPIR-V specification [Kessenich et al. 2018, p. 172]. Trace scheduling methods that are aware of

warps produced by the GPU have therefore been developed, however, if-conversion is only performed after scheduling instead of using a scheduling algorithm that is aware of predication. 'Warp-Aware Trace Scheduling could benefit from trace-enlarging techniques, like Superblock scheduling's tail duplication and Hyperblock scheduling's predication' (Jablin et al. [2014]).

# 2.4 Scheduling

Instruction scheduling is the main transformation and optimisation performed by traditional HLS tools. The scheduling transformation introduces time into the untimed input representation by placing each instruction into a clock cycle in which it should execute. The scheduler must take into account the resources that were selected during the resource allocation step and schedule the instructions so that they meet certain constraints. In this section I will discuss scheduling techniques used by HLS tools, first discussing static scheduling in section 2.4.1, which is the scheduling algorithm used by Vericert in this dissertation, followed by describing dynamic scheduling in section 2.4.2, which is an alternative scheduling technique with different trade-offs to static scheduling.

## 2.4.1 Static scheduling

Static scheduling is used by the majority of synthesis tools [AMD 2023b; Canis et al. 2013; Intel 2020b; Roane 2023; Siemens 2021] and means that the time at which each operation will execute is known at compile time. The first step is to generate a CDFG, which is either already the structure of the code, or can be generated from a hyperblock CFG representation, for example, by using static analysis on each hyperblock to gather all data dependencies and convert them into DFGs.

Scheduling can have different optimisation goals for the design in terms of latency and resource usage. We will assume that scheduling is performed independently on blocks of code without back edges, i.e. on the DFG blocks in a CDFG like the one shown in figure 2.3d. Within these blocks, each operation in the DFG can be scheduled as soon as its predecessor in the graph has been scheduled, resulting in an as soon as possible (ASAP) schedule, where the start time of each node corresponds to the longest path from the start of the DFG to that node. If instead the start time of a node is taken to be the longest path from the node to the end of the DFG, then this would result in an as late as possible (ALAP) schedule. The difference between these two types of schedules shows the

*slack* of a particular operation, which can be exploited by schedulers to minimise resources while also minimising latency.

A more advanced scheduler can either optimise for resource usage based on a maximum latency or for latency based on a maximum amount of resources. In general this is an NP-hard problem, however, *list scheduling* [Baker 2019, p. 257] provides a heuristic for this problem by ordering nodes that can be scheduled according to a priority function and picking a subset of these nodes to actually be scheduled as long as the resources used by the subset is not greater than the available resources. Another alternative scheduling algorithm initially used to perform synthesis of behavioural hardware description languages is called force-directed scheduling [Paulin and Knight 1989], which is tasked to minimise the number of functional units, memory and buses by balancing operations associated with these resources. The intuition is that this balancing creates a schedule with high utilisation and therefore low resource usage, without sacrificing on overall execution time of the design. It works by iteratively calculating forces associated with each node and scheduling the node with the lowest force.

#### System of difference constraints scheduling

The main static scheduling algorithm used by HLS tools is the system of difference constraints (SDC) scheduling algorithm [Cong and Zhang 2006]. It generates an SDC that is a subset of a linear programming (LP) problem that can be incrementally modified and checked for feasibility as new constraints are added. Then, to solve the SDC it can be converted into an LP problem guaranteeing integer solutions.

The scheduling algorithm is built on the notion of constraining scheduling variables for an operation v (sv<sub>i</sub>(v)). Each operation is associated with a set of scheduling variables, but at a minimum it must have an initial and a final scheduling variable (sv<sub>init</sub>(v) and sv<sub>fin</sub>(v)). The main advantage of this scheduling algorithm is that one can define different concepts as constraints in terms of scheduling variables. For example, if one has a data dependency from operation a to operation b, the following constraint is added to the SDC.

$$\operatorname{sv}_{\operatorname{fin}}(a) - \operatorname{sv}_{\operatorname{init}}(b) \le 0$$

(2.1)

Other types of constraints that are normally added to get a valid schedule are:

**Control dependency constraint** Constraint between blocks of instructions that are connected by a control-flow dependency. This ensures that a block is not scheduled

before another block it depends on. In particular, loop back edges therefore need to be removed during the SDC construction, as otherwise the system would become unsatisfiable.

- **Relative timing constraint** This constraint ensures that two operations are separated by at least or at most a fixed number of cycles. This can be used to satisfy I/O timings.

- Latency constraint This constraint specifies a maximum latency for a set of blocks.

- **Cycle time constraint** This constraint is used to target a specific final clock period, and split up long combinational paths through the DFG into separate cycles. This allows for *operation chaining*, whereby multiple operations that are estimated to have a latency less than a clock cycle can be chained within the same clock cycle.

- **Resource constraint** To handle limited resources, constraints can be used to make it infeasible to have operations use the same resource within the same clock cycle. Constructing these constraints relies on a linear ordering of the DFG, so some combination of ALAP or ASAP scheduling can be done to form the linear ordering before the actual scheduling step.

Solving the SDC with different optimisation functions produces different kinds of schedules. For example, optimising the following function will produce an ALAP schedule, as the start time of every operation is maximised.

$$\max \sum_{v \in V_{\rm op}} {\rm sv}_{\rm init}(v) \tag{2.2}$$